宽带分数分频频率综合器中电荷泵和分频器电路设计 的量化序列动态地调整分频比,从而实现分数分频。分数的小数部分越小,频率 精度也就越高。输出频率精度也就不再受限于参考时钟频率,这为选取较大的环 路带宽来提高锁定速度提供了方便。当然,△Σ分数分频频率综合器也存在许多 问题需要解决,譬如△Σ调制器引入的量化噪声、环路的非线性等。 1.2论文的主要贡献 本论文主要设计了△Σ分数分频频率综合器中的鉴频鉴相器、电荷泵、分频 器以及/Q分频器等电路模块。针对设计中遇到的问题,采用了相应的技术和解 决办法,本论文的主要贡献有: )分析了电荷泵型鉴频鉴相器的非线性对带内噪声的影响,提出了一种降低非 线性的技术来减小鉴频鉴相器和电荷泵对带内噪声的贡献。 2)在鉴频鉴相器的设计中,同时引入两种工作模式:一种是基于传统的工作模 式,并且导通时间可供选择:另外一种是基于降低电路非线性的工作模式。 此外,本论文还设计了重置信号开关电路和锁定检测电路,用于环路的控制。 3)采用全差分结构的电荷泵,来提高频率综合器的性能。设计的源端开关型电 荷泵单元简化了电路,并且使得电荷泵上下电流的调节来得更为简单。 4)把整个全差分电荷泵的有源电路版图置于环路滤波器的MIM(Metal Insulator Metal)电容之下,用第三铝金属层作为隔离层,使得电荷泵和环路 滤波器的芯片面积减小近二分之一。 5)详细分析了晶体管间的mismatch对电荷泵电路性能的影响,得出了晶体管 间的mismatch在整个电荷泵上下电流匹配特性中占主要地位的结论。 6)设计了一种全新的Q分频器电路,可以减小工艺误差对电路性能的影响。 其间,引入一个对输入信号放大整形的电路,很好地解决了困扰电路的灵敏 度问题。 1.3论文的研究内容和组织结构 本论文主要介绍了△Σ分数分频频率综合器中几个模块的设计,包括鉴频鉴 相器、电荷泵、分频器和Q分频器电路模块。论文从频率综合器的性能要求出 发,分别指出各个模块设计中所要考虑的因素,并提出相应的解决方案。论文各 部分内容安排如下: 第二章“频率综合器”首先阐述了频率综合器的原理;然后指出频率综合器 设计时需要关注的几个重要参数,分析了这些参数的影响并且给出了相应的推导 过程;最后总结了频率综合器的设计流程。 第三章“鉴频鉴相器分析与设计”首先介绍了鉴频鉴相器的电路结构:然后 分析了鉴频鉴相器中的非理想效应,相位噪声模型以及非线性特性,并且提出了 2

宽带分数分频频率综合器中电荷泵和分频器电路设计 2 的量化序列动态地调整分频比,从而实现分数分频。分数的小数部分越小,频率 精度也就越高。输出频率精度也就不再受限于参考时钟频率,这为选取较大的环 路带宽来提高锁定速度提供了方便。当然,∆Σ分数分频频率综合器也存在许多 问题需要解决,譬如∆Σ调制器引入的量化噪声、环路的非线性等。 1.2 论文的主要贡献 本论文主要设计了 ∆Σ 分数分频频率综合器中的鉴频鉴相器、电荷泵、分频 器以及 I/Q 分频器等电路模块。针对设计中遇到的问题,采用了相应的技术和解 决办法,本论文的主要贡献有: 1) 分析了电荷泵型鉴频鉴相器的非线性对带内噪声的影响,提出了一种降低非 线性的技术来减小鉴频鉴相器和电荷泵对带内噪声的贡献。 2) 在鉴频鉴相器的设计中,同时引入两种工作模式:一种是基于传统的工作模 式,并且导通时间可供选择;另外一种是基于降低电路非线性的工作模式。 此外,本论文还设计了重置信号开关电路和锁定检测电路,用于环路的控制。 3) 采用全差分结构的电荷泵,来提高频率综合器的性能。设计的源端开关型电 荷泵单元简化了电路,并且使得电荷泵上下电流的调节来得更为简单。 4) 把整个全差分电荷泵的有源电路版图置于环路滤波器的 MIM(Metal Insulator Metal)电容之下,用第三铝金属层作为隔离层,使得电荷泵和环路 滤波器的芯片面积减小近二分之一。 5) 详细分析了晶体管间的 mismatch 对电荷泵电路性能的影响,得出了晶体管 间的 mismatch 在整个电荷泵上下电流匹配特性中占主要地位的结论。 6) 设计了一种全新的 I/Q 分频器电路,可以减小工艺误差对电路性能的影响。 其间,引入一个对输入信号放大整形的电路,很好地解决了困扰电路的灵敏 度问题。 1.3 论文的研究内容和组织结构 本论文主要介绍了 ∆Σ 分数分频频率综合器中几个模块的设计,包括鉴频鉴 相器、电荷泵、分频器和 I/Q 分频器电路模块。论文从频率综合器的性能要求出 发,分别指出各个模块设计中所要考虑的因素,并提出相应的解决方案。论文各 部分内容安排如下: 第二章“频率综合器”首先阐述了频率综合器的原理;然后指出频率综合器 设计时需要关注的几个重要参数,分析了这些参数的影响并且给出了相应的推导 过程;最后总结了频率综合器的设计流程。 第三章“鉴频鉴相器分析与设计”首先介绍了鉴频鉴相器的电路结构;然后 分析了鉴频鉴相器中的非理想效应,相位噪声模型以及非线性特性,并且提出了

第一章绪论 相应的改进方案,包括提出的一种降低非线性的技术:最后给出了具体的鉴频鉴 相器的电路版图和仿真结果。 第四章“全差分电荷泵设计”首先分析了基于全差分电荷泵电路的环路稳定 特性:然后从晶体管级别分析了影响电荷泵性能的一些考虑因素,其中对晶体管 间的mismatch做了详细的分析:最后给出了全差分电荷泵的电路版图和仿真结 果。 第五章“分频器分析与设计”介绍了基于高速电流模式(Current Mode Logic, CML)结构的4/5预分频器和/Q分频器的设计。分别对4/5预分频器的时序问题 和/Q分频器的匹配特性进行了详细分析并且给出了相应的解决方法。设计了一 种全新的/Q分频器电路,解决了困扰电路的灵敏度问题。最后,给出了4/5预 分频器和/Q分频器的电路版图和仿真结果。 第六章“展望与总结”首先对本文的工作进行总结,然后对未来的工作进行 了简单的展望。 3

第一章 绪论 3 相应的改进方案,包括提出的一种降低非线性的技术;最后给出了具体的鉴频鉴 相器的电路版图和仿真结果。 第四章“全差分电荷泵设计”首先分析了基于全差分电荷泵电路的环路稳定 特性;然后从晶体管级别分析了影响电荷泵性能的一些考虑因素,其中对晶体管 间的 mismatch 做了详细的分析;最后给出了全差分电荷泵的电路版图和仿真结 果。 第五章“分频器分析与设计”介绍了基于高速电流模式(Current Mode Logic, CML)结构的 4/5 预分频器和 I/Q 分频器的设计。分别对 4/5 预分频器的时序问题 和 I/Q 分频器的匹配特性进行了详细分析并且给出了相应的解决方法。设计了一 种全新的 I/Q 分频器电路,解决了困扰电路的灵敏度问题。最后,给出了 4/5 预 分频器和 I/Q 分频器的电路版图和仿真结果。 第六章“展望与总结”首先对本文的工作进行总结,然后对未来的工作进行 了简单的展望

第二章 频率综合器概述 2.1引言 随着移动终端的飞速发展,便携式的电子产品己经明显改变了人们的生活方 式。诸如智能手机的普及,人们习惯性地通过3G等无线网络连接到互联网,使 得无线通讯市场蓬勃发展。被誉为电子系统“心脏”的频率综合器在通讯领域得 到了越来越广泛的重视。 频率综合器可以产生一个或多个频率信号,为数字系统和射频接受发送器提 供时钟信号或者本振信号。按照实现结构分,频率综合器可以分为直接数字频率 综合器和锁相环频率综合器。直接数字频率综合器基于全数字技术,将抽样正弦 波形存在存储器中,直接合成所需频率的波形。它具有速度快、频率分辨率高等 优点。但是它的功耗比较大而且频率范围受到限制。锁相环频率综合器通过反馈 环路能够得到高纯度的输出频谱,而且很容易得到不同频率的信号,所以得到了 广泛的应用。 2.2频率综合器 整数分频频率综合器的结构相对简单,如图2-1所示。实质上,频率综合器 是一个基于相位的负反馈系统。它的工作过程,大致可以描述如下:鉴频鉴相器 检测来自参考时钟与分频器输出的频率信号,比较它们的相位差,并把相位差转 换成两路数字脉冲信号。通过这两路数字信号分别去控制电荷泵的上下导通开 关,使得电荷泵产生相应的电流。这些电流注入到环路滤波器(Loop Filter,,LPF) 中,导致环路滤波器电容上的电荷不断积累,从而完成了电流到电压的转换。压 控振荡器(Voltage Control Oscillator,VCO)具有近似线性的调控特性,能够把 环路滤波器的电压转换成相应的频率。但是压控振荡器的频率很高,需要分频器 对其分频处理后,才能与参考时钟频率比较。这样就完成了一个循环的过程。 up PFD Charge Loop 几威 Pump Filter dn Divider VCo W 1/W 图21整数分频频率综合器

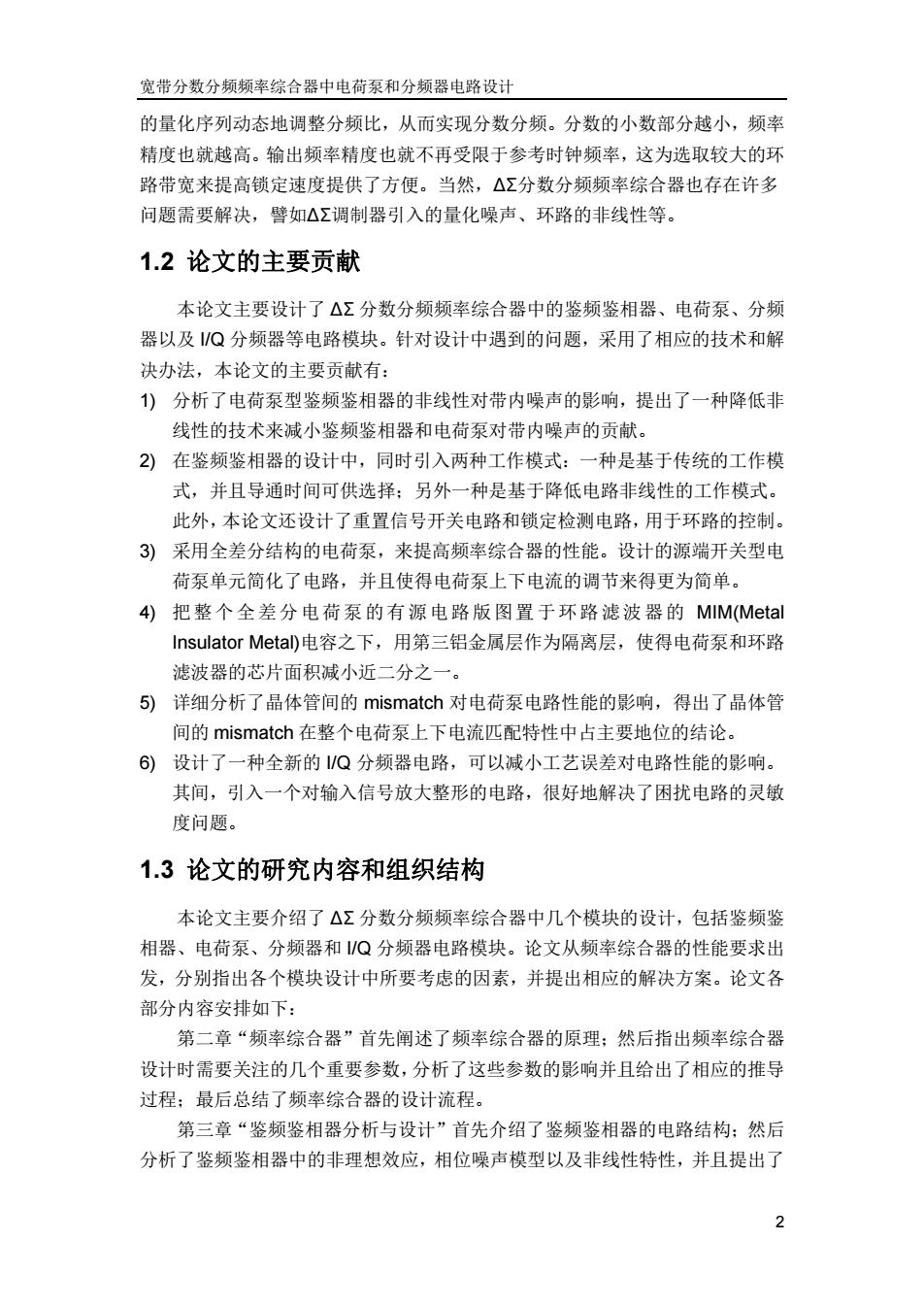

第二章 频率综合器概述 2.1 引言 随着移动终端的飞速发展,便携式的电子产品已经明显改变了人们的生活方 式。诸如智能手机的普及,人们习惯性地通过 3G 等无线网络连接到互联网,使 得无线通讯市场蓬勃发展。被誉为电子系统“心脏”的频率综合器在通讯领域得 到了越来越广泛的重视。 频率综合器可以产生一个或多个频率信号,为数字系统和射频接受发送器提 供时钟信号或者本振信号。按照实现结构分,频率综合器可以分为直接数字频率 综合器和锁相环频率综合器。直接数字频率综合器基于全数字技术,将抽样正弦 波形存在存储器中,直接合成所需频率的波形。它具有速度快、频率分辨率高等 优点。但是它的功耗比较大而且频率范围受到限制。锁相环频率综合器通过反馈 环路能够得到高纯度的输出频谱,而且很容易得到不同频率的信号,所以得到了 广泛的应用。 2.2 频率综合器 整数分频频率综合器的结构相对简单,如图 2-1 所示。实质上,频率综合器 是一个基于相位的负反馈系统。它的工作过程,大致可以描述如下:鉴频鉴相器 检测来自参考时钟与分频器输出的频率信号,比较它们的相位差,并把相位差转 换成两路数字脉冲信号。通过这两路数字信号分别去控制电荷泵的上下导通开 关,使得电荷泵产生相应的电流。这些电流注入到环路滤波器(Loop Filter, LPF) 中,导致环路滤波器电容上的电荷不断积累,从而完成了电流到电压的转换。压 控振荡器(Voltage Control Oscillator, VCO) 具有近似线性的调控特性,能够把 环路滤波器的电压转换成相应的频率。但是压控振荡器的频率很高,需要分频器 对其分频处理后,才能与参考时钟频率比较。这样就完成了一个循环的过程。 图 2-1 整数分频频率综合器

宽带分数分频频率综合器中电荷泵和分频器电路设计 分频器作用于频率综合器的反馈环路上,分频比为/N。就如同运放中的反 馈系数B,放大倍数为反馈系数的倒数1/B。在这里,压控振荡器的输出频率vco 为参考时钟频率fREF的N倍 fyco Nx fREF (2.1) 然而,整数分频频率综合器的性能受到参考频率fREF的限制。一方面,fREF 决定了频率综合器能够达到的最小精度,fF不能选得太大;另一方面,REF也 决定了环路的带宽(fw<fEF/1O),fREF不能选得太小。因为,环路带宽太小会减 慢环路的锁定时间,而且对抑制压控振荡器在环路中贡献的噪声不是很理想[5]。 考虑到上述问题,工程中应用的更多的是分数分频频率综合器,其结构如图2-2 所示。 fREF- up PFD Charge Loop Pump Filter dn Divider VCO 1/N △Σ n fVco=(N+a)EF Modulator 图2-2分数分频频率综合器 与整数分频频率综合器采用整数分频比不同,分数分频频率综合器在环路锁 定之后,Dⅳ的边沿不是严格对齐EF的边沿,而是时而超前,时而滞后。只是 fDv边沿的平均值与EF的边沿对齐。所以,分数分频实现的是一种动态的锁定。 但这又引入了另外一个问题“分数毛刺”。当相位差增加到一个不可忽略的值时, 低通滤波器输出的幅值也变得相当大,使得分数毛刺的幅值仅仅比载波信号低 20-30dB[7] 为了解决上述问题,在分数分频频率综合器的设计中应用到了△Σ调制器, 它在对输入信号过采样的同时,将低频的量化噪声搬移到较高的频率,通过对量 化噪声整形,可以进一步提高带内的信噪比,如下图2-3所示。 △Σ调制器6]输出整数序列y[],在信号fbw的协调下,控制多模分频器的 分频比N+yn]。输入信号a介于0和1之间,在锁相环锁定之后,y[n长时间的 平均值即为a。于是我们得到输出频率co为参考时钟频率fREF的N+a倍 iom-(N+2r[闪s=w+axs (2.2) 6

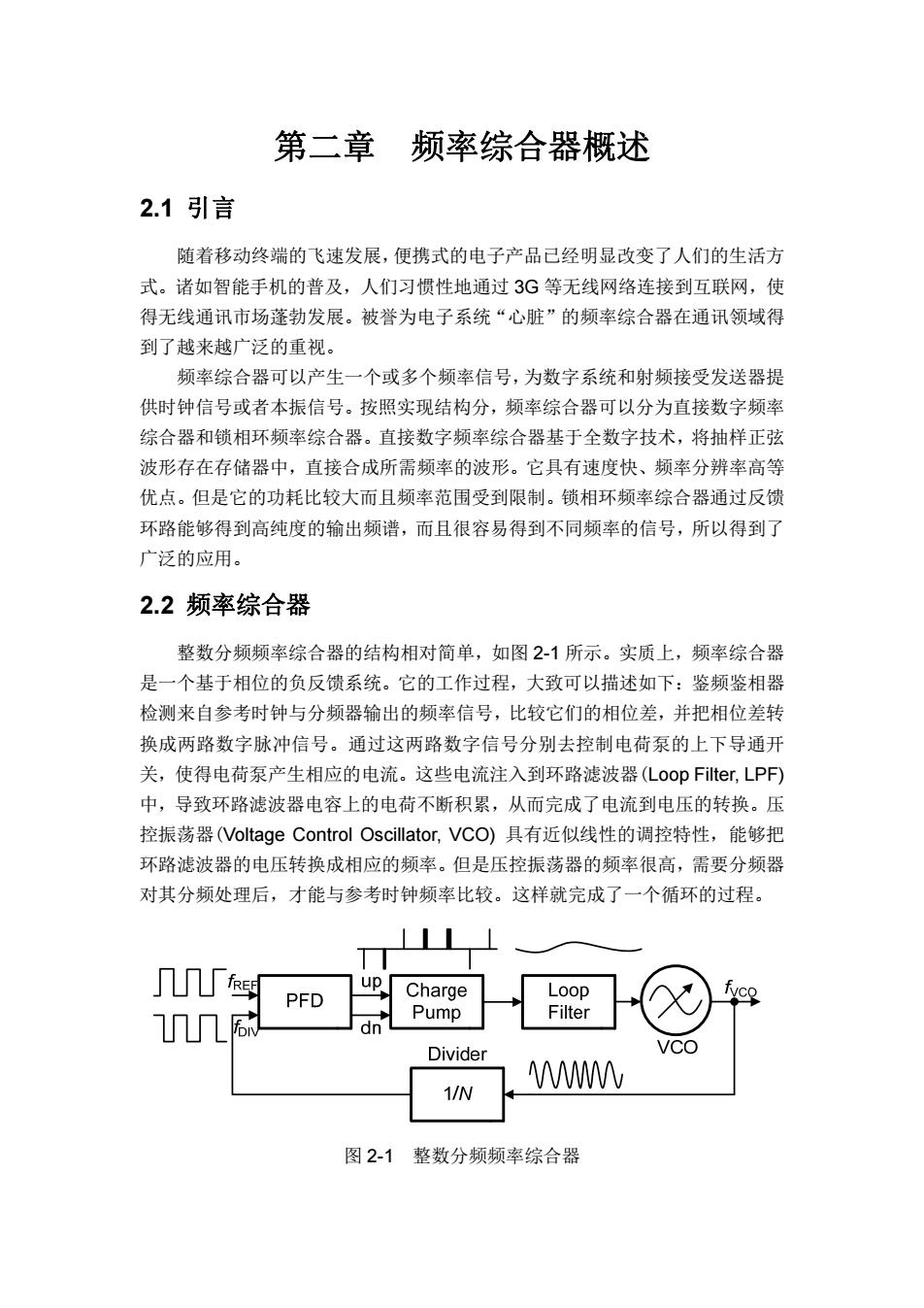

宽带分数分频频率综合器中电荷泵和分频器电路设计 6 分频器作用于频率综合器的反馈环路上,分频比为 1/N。就如同运放中的反 馈系数 β,放大倍数为反馈系数的倒数 1/β。在这里,压控振荡器的输出频率 fVCO 为参考时钟频率 fREF 的 N 倍 f Nf VCO REF (2.1) 然而,整数分频频率综合器的性能受到参考频率 fREF的限制。一方面,fREF 决定了频率综合器能够达到的最小精度,fREF 不能选得太大;另一方面,fREF 也 决定了环路的带宽(fBW< fREF /10),fREF不能选得太小。因为,环路带宽太小会减 慢环路的锁定时间,而且对抑制压控振荡器在环路中贡献的噪声不是很理想[5]。 考虑到上述问题,工程中应用的更多的是分数分频频率综合器,其结构如图 2-2 所示。 图 2-2 分数分频频率综合器 与整数分频频率综合器采用整数分频比不同,分数分频频率综合器在环路锁 定之后,fDIV的边沿不是严格对齐 fREF的边沿,而是时而超前,时而滞后。只是 fDIV边沿的平均值与 fREF的边沿对齐。所以,分数分频实现的是一种动态的锁定。 但这又引入了另外一个问题“分数毛刺”。当相位差增加到一个不可忽略的值时, 低通滤波器输出的幅值也变得相当大,使得分数毛刺的幅值仅仅比载波信号低 20~30dB[7] 为了解决上述问题,在分数分频频率综合器的设计中应用到了 ∆Σ 调制器, 它在对输入信号过采样的同时,将低频的量化噪声搬移到较高的频率,通过对量 化噪声整形,可以进一步提高带内的信噪比,如下图 2-3 所示。 ∆Σ 调制器[6]输出整数序列 y[n],在信号 fDIV 的协调下,控制多模分频器的 分频比 N+y[n]。输入信号 α 介于 0 和 1 之间,在锁相环锁定之后,y[n]长时间的 平均值即为 α。于是我们得到输出频率 fVCO为参考时钟频率 fREF 的 N+α 倍 VCO REF REF 1 1 n k f N yk f N α f n (2.2)

第二章频率综合器 △E Modulator fREF TREF 图2-3△Σ调制器对噪声的整形 需要注意的是,如果环路中各个模块的非线性表现得比较明显,△Σ调制器 对噪声的整形也将被恶化。带外的量化高频噪声将会被折叠到低频的带内,增加 带内的相位噪声和毛刺成分[8]。 2.3重要参数 频率综合器的设计需要考虑很多影响系统性能的因素,并且它们之间相互影 响,使得设计变得复杂。于是,我们有必要对这些因素进行简要说明,在理解它 们的基础上为后面几个章节的电路分析和设计提供指导。本小节我们主要介绍几 个重要的品质因素:相位噪声(Phase Noise)、毛刺(Spurious Emissions)和锁定 时间(Lock Time[9]。 2.3.1相位噪声 接收机的本振输出包含相位噪声,则通过互易混频使得很强的临近干扰信号 也同时被变换到有用信道中,造成信号频谱的阻塞,降低了信道中的信噪比,如 图2-4()所示。即使中频滤波器能够滤除强干扰中频信号,强干扰中频信号的噪 声边带仍然淹没了有用信号,使接收机无法接收到弱小信号,如图2-4(b)所示。 Interferer Wanted Signal. Interferer Wanted Downconverte Signal Signals W1 2 7

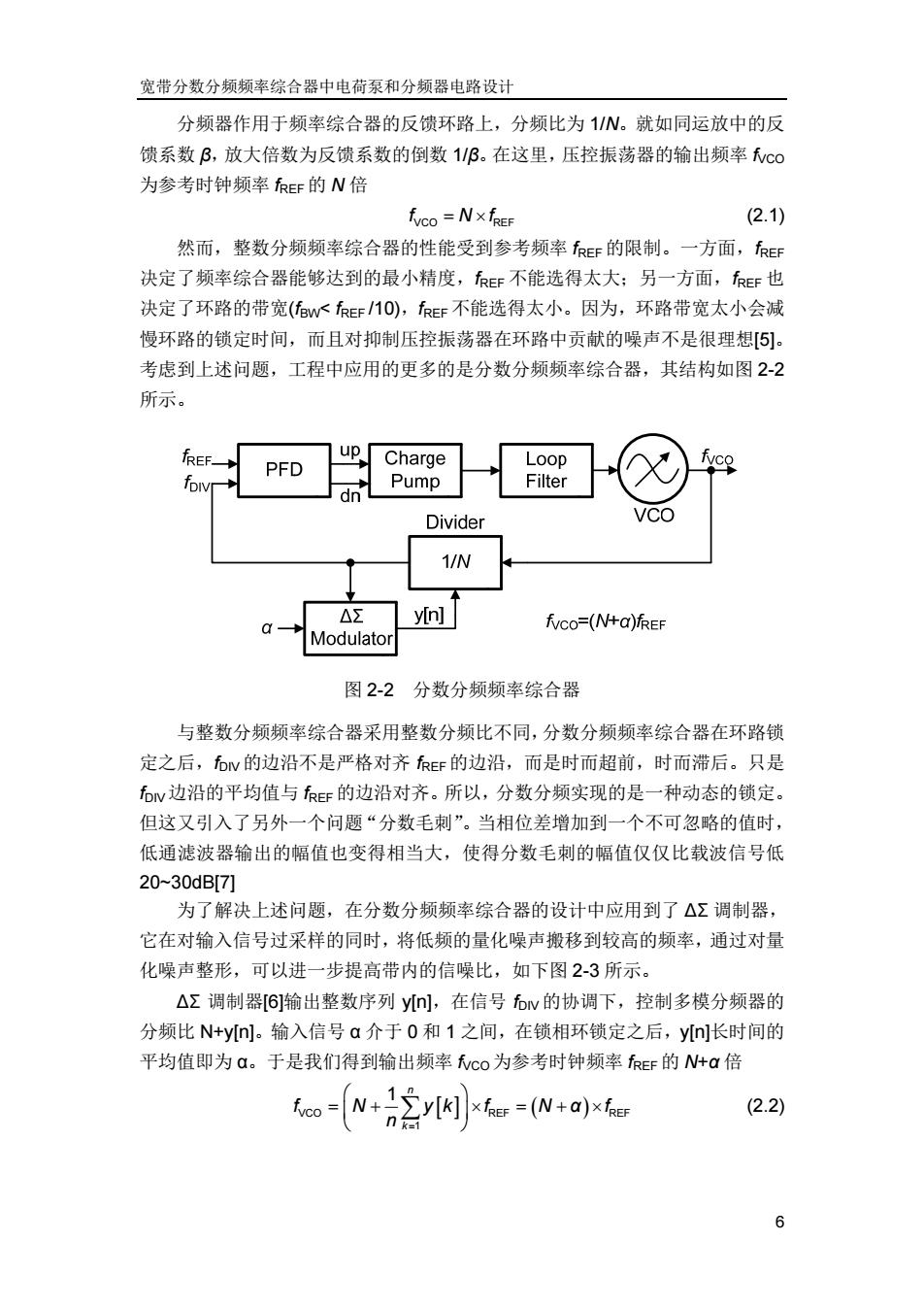

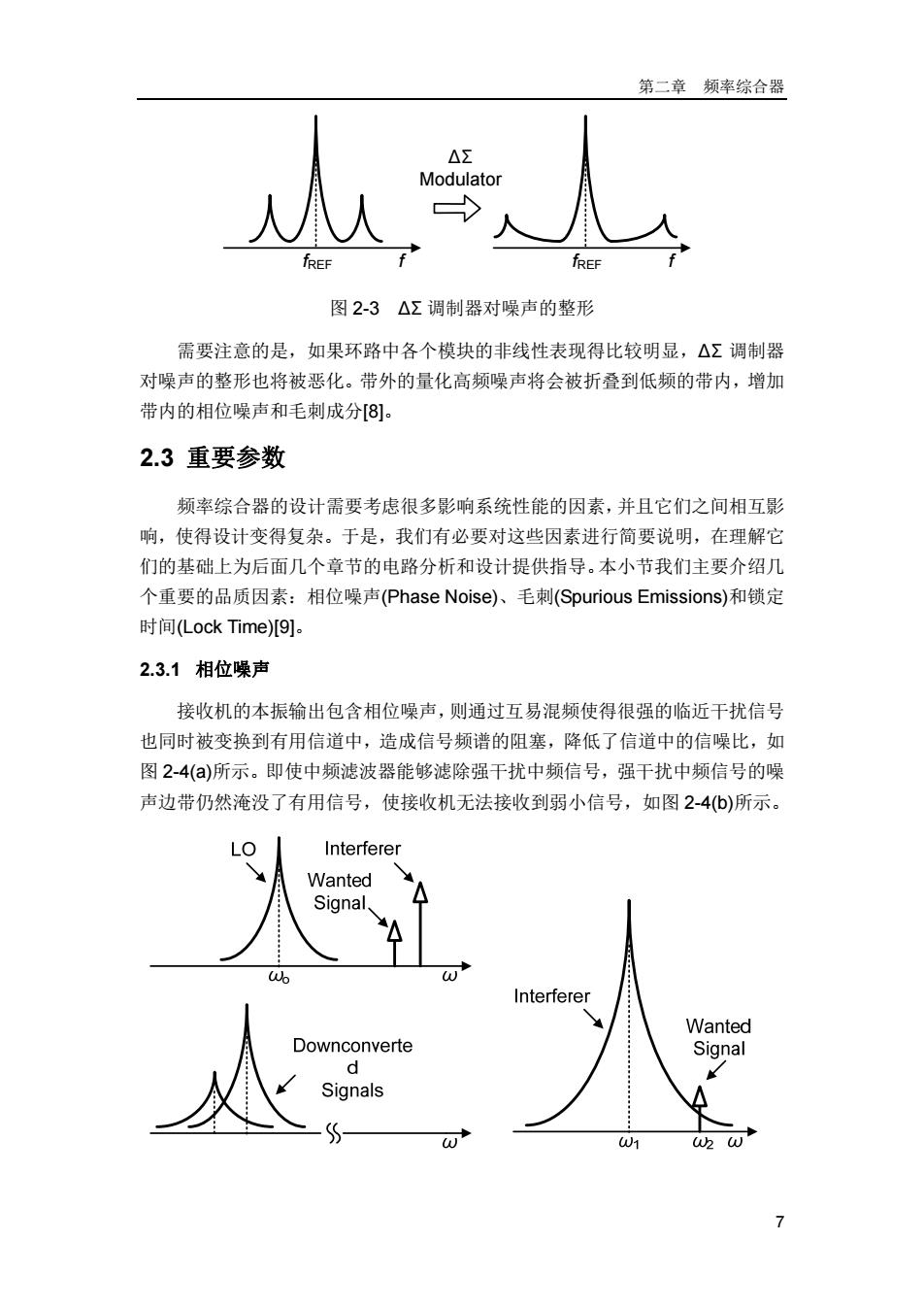

第二章 频率综合器 7 fREF f fREF f ∆Σ Modulator 图 2-3 ∆Σ 调制器对噪声的整形 需要注意的是,如果环路中各个模块的非线性表现得比较明显,∆Σ 调制器 对噪声的整形也将被恶化。带外的量化高频噪声将会被折叠到低频的带内,增加 带内的相位噪声和毛刺成分[8]。 2.3 重要参数 频率综合器的设计需要考虑很多影响系统性能的因素,并且它们之间相互影 响,使得设计变得复杂。于是,我们有必要对这些因素进行简要说明,在理解它 们的基础上为后面几个章节的电路分析和设计提供指导。本小节我们主要介绍几 个重要的品质因素:相位噪声(Phase Noise)、毛刺(Spurious Emissions)和锁定 时间(Lock Time)[9]。 2.3.1 相位噪声 接收机的本振输出包含相位噪声,则通过互易混频使得很强的临近干扰信号 也同时被变换到有用信道中,造成信号频谱的阻塞,降低了信道中的信噪比,如 图 2-4(a)所示。即使中频滤波器能够滤除强干扰中频信号,强干扰中频信号的噪 声边带仍然淹没了有用信号,使接收机无法接收到弱小信号,如图 2-4(b)所示