第二章分频器的研究 置数过程占用较多的时间,该种分频器难以实现很高的速度,适合于低频应用。 2.1.2 Pulse-Swallow型可编程分频器 图2-2是一种比较常用的可编程分频器,它由M/M+1双模预分频器(Dul Modulus Prescaler)、可编程计数器(P counter)和吞计数器(S Counter)三部 分组成。双模预分频器负责将VCO频率降低到数字电路可以接受的程度,它可以进 行M+1分频和M分频两种操作,由控制信号mod决定,当mod=”1”时,进行M+1分 频,当mod=”O”时,进行M分频。P计数器和S计数器的时钟输入是经过预分频器降 频后的信号,工作频率较低,可以采用2.1.1节介绍的可预置数的可编程分频器。 fvco Prescaler clki Program Tdiv M/M+1 Counter“P” LD mod Swallow Counter“S” 图2-2 Pulse-Swallow型可编程分频器 它的工作原理是:当分频器开始工作时,od=”1”,预分频器工作在M+1分频模 式,可编程计数器和吞咽计数器同时开始计数。当计数完S个脉冲后,S计数器停止 计数,发出改变分频模式的控制信号od,使预分频器工作在M分频模式,P计数器 继续计数,当计满P个脉冲后,发出置位信号,开始新一轮的计数,以此循环。计 数操作可以采用递增计数或者递减计数,递减计数可以采用2.1.1节介绍的可预置数 的可编程分频器。可以看到,在一次循环中总共进行了P次计数,其中有S次计数 预分频器工作在M+1分频模式,其余的PS次计数预分频器工作在M分频模式,因 此分频器的分频比是: N-(M+1)-S.To+M-(P-S).T (3.1) =M.P+S 由于采用了双模预分频器对VCO信号进行降频,该种类型的可编程分频器可以 工作在较高的频率。分频器能够实现的分频范围与P和S的实现方式有关,一般情 况下能够实现的分频比范围是M2到无穷大,将在第三章详细介绍。 5

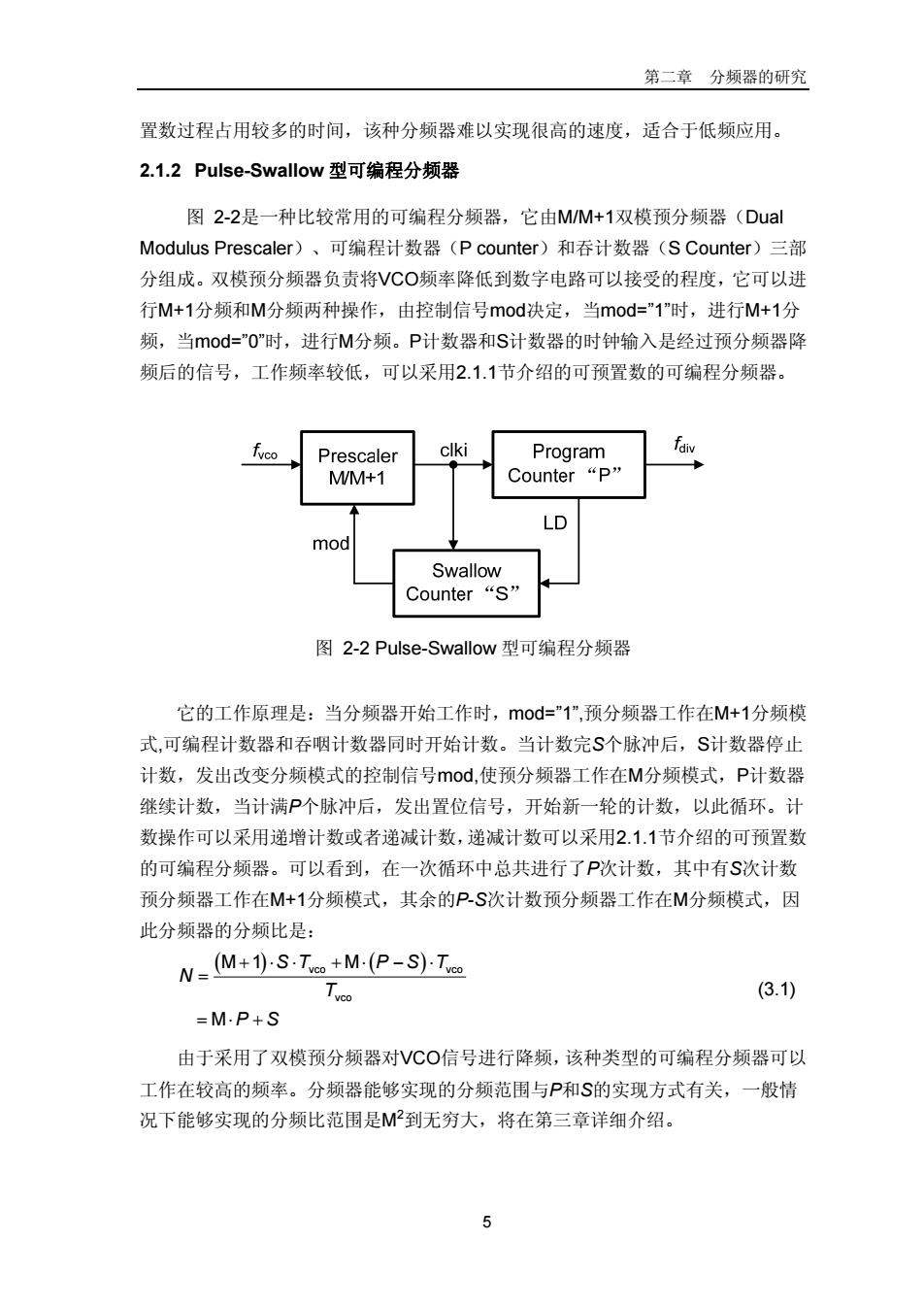

第二章 分频器的研究 置数过程占用较多的时间,该种分频器难以实现很高的速度,适合于低频应用。 2.1.2 Pulse-Swallow 型可编程分频器 图 2-2是一种比较常用的可编程分频器,它由M/M+1双模预分频器(Dual Modulus Prescaler)、可编程计数器(P counter)和吞计数器(S Counter)三部 分组成。双模预分频器负责将VCO频率降低到数字电路可以接受的程度,它可以进 行M+1分频和M分频两种操作,由控制信号mod决定,当mod=”1”时,进行M+1分 频,当mod=”0”时,进行M分频。P计数器和S计数器的时钟输入是经过预分频器降 频后的信号,工作频率较低,可以采用2.1.1节介绍的可预置数的可编程分频器。 图 2-2 Pulse-Swallow 型可编程分频器 它的工作原理是:当分频器开始工作时,mod=”1”,预分频器工作在M+1分频模 式,可编程计数器和吞咽计数器同时开始计数。当计数完S个脉冲后,S计数器停止 计数,发出改变分频模式的控制信号mod,使预分频器工作在M分频模式,P计数器 继续计数,当计满P个脉冲后,发出置位信号,开始新一轮的计数,以此循环。计 数操作可以采用递增计数或者递减计数,递减计数可以采用2.1.1节介绍的可预置数 的可编程分频器。可以看到,在一次循环中总共进行了P次计数,其中有S次计数 预分频器工作在M+1分频模式,其余的P-S次计数预分频器工作在M分频模式,因 此分频器的分频比是: () ( ) vco vco vco M1 M M ST P S T N T P S +⋅⋅ +⋅ − ⋅ = =⋅+ (3.1) 由于采用了双模预分频器对VCO信号进行降频,该种类型的可编程分频器可以 工作在较高的频率。分频器能够实现的分频范围与P和S的实现方式有关,一般情 况下能够实现的分频比范围是M2 到无穷大,将在第三章详细介绍。 5

频率综合器中分频器的研究与设计 2.1.3基于23分频单元的多模可编程分频器 基于23分频单元的多模可编程分频器也是一种常用的结构,如图2-3所示 [15]。该分频器由基本23分频单元级联组成,每一级单元的逻辑结构相同,每一级 的输入时钟是前一级的分频输出时钟,每一级的输出控制信号反馈回前一级,连接 成类似于行波计数器的结构。 2/3 2/3 02 2/3 FOn-1 2/3 cel cell cell cell mod mod2 2 modn-1 n-1 mod, Po Fout Pn-2 Pn-1 图2-3基于23分频单元的多模可编程分频器 图23所示的多模可编程分频器按照如下方式工作:在每一个分频周期,分频器 串中处于最后一级的双模预分频器产生模式信号modn-1,然后这个信号沿着分频器 串向上传播,在每一级23单元处都被那一级的输入时钟所同步。如果编程输入位 (图2-3中的po,p1,,pn1)为“1”,处于高电平的mod信号将使23分频单元工作 在3分频模式。在一个分频周期中每个23分频单元最多经历一次3分频模式,在分 频周期的其它时间都工作在二分频模式,因此,除3操作使得23基本单元的输出信 号只增加了一个额外的输入信号周期。 分频器的输出周期为[15]: Tout =20.Tin +2m1.TinPri+202.TinPn2++2.Tin+Tinpo (3.2) =(2"+21.pn1+2m2.p2+…+2P,+Po)Tm 该类分频器所能实现的分频比范围较小,为2到2+11,最大分频比大概是最 小分频比的两倍,但通过结构上的修改,可以扩展分频比的范围[15]。该分频器具 有模块化的优点,有利于版图的设计,各级信号工作在不同的频率,有利于对功耗 进行优化。 2.2预分频器 双模预分频器主要有三种结构,它们分别是: 2.2.1同步预分频器 该种类型的分频器能够实现2“2k+1类型的双模预分频器。根据实现的基本逻辑 的不同,它又可以分为基于与非门的实现和基于或非门的实现两种基本类型。下面

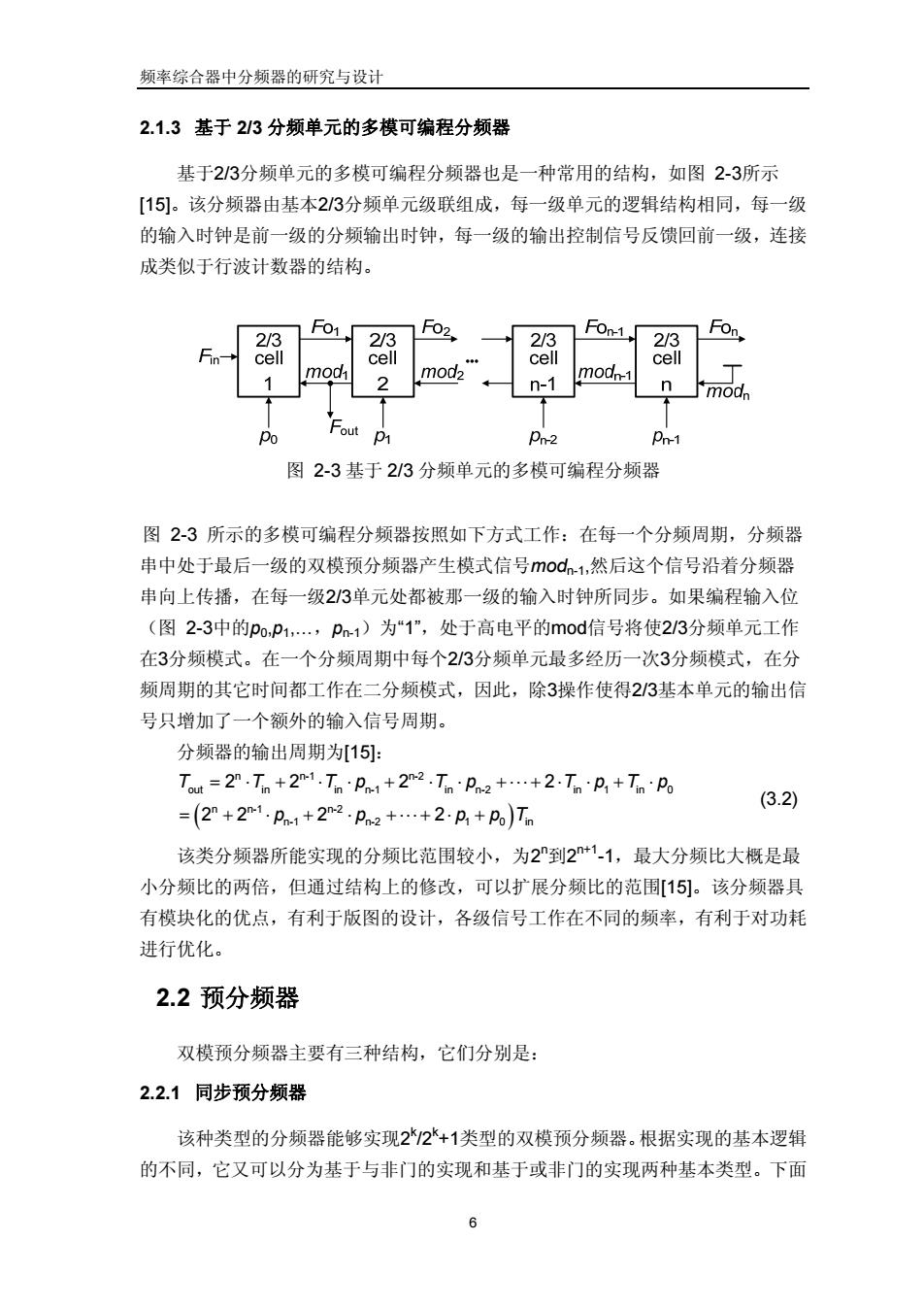

频率综合器中分频器的研究与设计 2.1.3 基于 2/3 分频单元的多模可编程分频器 基于2/3分频单元的多模可编程分频器也是一种常用的结构,如图 2-3所示 [15]。该分频器由基本2/3分频单元级联组成,每一级单元的逻辑结构相同,每一级 的输入时钟是前一级的分频输出时钟,每一级的输出控制信号反馈回前一级,连接 成类似于行波计数器的结构。 图 2-3 基于 2/3 分频单元的多模可编程分频器 图 2-3 所示的多模可编程分频器按照如下方式工作:在每一个分频周期,分频器 串中处于最后一级的双模预分频器产生模式信号modn-1,然后这个信号沿着分频器 串向上传播,在每一级2/3单元处都被那一级的输入时钟所同步。如果编程输入位 (图 2-3中的p0,p1,…,pn-1)为“1”,处于高电平的mod信号将使2/3分频单元工作 在3分频模式。在一个分频周期中每个2/3分频单元最多经历一次3分频模式,在分 频周期的其它时间都工作在二分频模式,因此,除3操作使得2/3基本单元的输出信 号只增加了一个额外的输入信号周期。 分频器的输出周期为[15]: ( ) n n-1 n-2 out in in n-1 in n-2 in 1 in 0 n n-1 n-2 n-1 n-2 1 0 in 22 2 2 22 2 2 T T Tp Tp TpTp p p p pT = ⋅ + ⋅ ⋅ + ⋅ ⋅ +⋅⋅⋅+ ⋅ ⋅ + ⋅ = + ⋅ + ⋅ +⋅⋅⋅+ ⋅ + (3.2) 该类分频器所能实现的分频比范围较小,为2n 到2n+1-1,最大分频比大概是最 小分频比的两倍,但通过结构上的修改,可以扩展分频比的范围[15]。该分频器具 有模块化的优点,有利于版图的设计,各级信号工作在不同的频率,有利于对功耗 进行优化。 2.2 预分频器 双模预分频器主要有三种结构,它们分别是: 2.2.1 同步预分频器 该种类型的分频器能够实现2k /2k +1类型的双模预分频器。根据实现的基本逻辑 的不同,它又可以分为基于与非门的实现和基于或非门的实现两种基本类型。下面 6

第二章分频器的研究 以与非逻辑的实现为例进行说明。与非门的特点是,只要有一个输入为”0”,它的输 出必定为”1”,只有两个输入均为”1”时,它的输出才为”0”。图2-4是基于与非逻辑 的22+1双模预分频器逻辑框图,图中的mod是分频模式控制信号。预分频器的基 本原理是:当mod=”0”时,第k+1个寄存器无效,前k个寄存器构成扭环形计数器, 可以实现输出占空比为50%的2分频:当od=”1”时,第k+1个寄存器工作,它的作 用是对第k个寄存器的输出Qk实现1个输入时钟周期的延时,由于与非逻辑的特点, 当Qk为”0”时,D1的输出为“1”,Qk+1对与D1没有影响,只有当Qk从"0”变为”1”时,Qk 的”1”状态和Qk延时一个输入时钟周期的Q+1的”0”状态相作用,使得D1多出一个高 电平的输入时钟周期,从而实现2k+1分频。当mod=”1时的工作过程如图2-5所示。 k+ mod 图2-4基于与非逻辑的22+1双模预分频器 将图2-4的两个与非门用或非门替换,并将od信号反相,就能得到基于或非 逻辑的实现,当mod=”1”时,Qk的”0”状态和Qk延时一个输入时钟周期的Qk+1的”1” 状态相作用,使得D1多出一个低电平的输入时钟周期。 2* 2 Q :100… 0 1 1 1 …11 0 0 Qk+1:110 0 0 1 0 D1:0111 0 00 011 图2-5mod=1时双模预分频器的工作过程 该种类型的预分频器由于逻辑简单,所以应用非常广泛,它也常用来构建异步 双模预分频器。该类型结构的缺点是,与非门(或非门)处在电路的关键路径上, 7

第二章 分频器的研究 以与非逻辑的实现为例进行说明。与非门的特点是,只要有一个输入为”0”,它的输 出必定为”1”,只有两个输入均为”1”时,它的输出才为”0”。图 2-4是基于与非逻辑 的2k /2k +1双模预分频器逻辑框图,图中的mod是分频模式控制信号。预分频器的基 本原理是:当mod=”0”时,第k+1个寄存器无效,前k个寄存器构成扭环形计数器, 可以实现输出占空比为50%的2k 分频;当mod=”1”时,第k+1个寄存器工作,它的作 用是对第k个寄存器的输出Qk实现1个输入时钟周期的延时,由于与非逻辑的特点, 当Qk为”0”时,D1的输出为“1”,Qk+1对与D1没有影响,只有当Qk从”0”变为”1”时,Qk 的”1”状态和Qk延时一个输入时钟周期的Qk+1的”0”状态相作用,使得D1多出一个高 电平的输入时钟周期,从而实现2k+1分频。当mod=”1”时的工作过程如图 2-5所示。 D Q Q Qk Dk+1 mod fin D1 Q1 fout Qk+1 12 k k+1 D Q Q D Q Q D Q Q 图 2-4 基于与非逻辑的 2k /2k +1 双模预分频器 将图 2-4的两个与非门用或非门替换,并将mod信号反相,就能得到基于或非 逻辑的实现,当mod=”1”时,Qk的”0”状态和Qk延时一个输入时钟周期的Qk+1的”1” 状态相作用,使得D1多出一个低电平的输入时钟周期。 图 2-5 mod=1 时双模预分频器的工作过程 该种类型的预分频器由于逻辑简单,所以应用非常广泛,它也常用来构建异步 双模预分频器。该类型结构的缺点是,与非门(或非门)处在电路的关键路径上, 7

频率综合器中分频器的研究与设计 降低了电路能够达到的最大频率,并且,所有的触发器都工作在最高工作频率,会 消耗非常大的功耗。还有,当k增大后,电路的冗余状态可能会形成不正常的循环, 使电路产生逻辑错误,因而该类电路适合实现较小的分频比,要实现更大分频比的 双模预分频器,一般采用异步电路。 2.2.2异步逻辑的预分频器 图2-6是异步电路构成的MM+1双模预分频器的一般结构,它由双模PP+1预分 频器,行波计数器和模式控制逻辑组成。PP+1双模预分频器的输出Fout1是行波计 数器的时钟输入。模式控制逻辑控制着PP+1双模预分频器的工作模式,它的输入 是外部输入模式控制信号mod和行波计数器的输出.M/M+1双模预分频器的工作原 理是:当mod为“1”(或“0”)时,模式控制逻辑的输出始终为“0”,因此双模预分频 器始终工作在P分频模式(这里假设od1=“0"时,PP+1双模预分频器工作在P分 频模式),因而实现的是M分频,这里M=2×P;而当od=“0”(或“1)时,在一个输 出周期内,模式控制逻辑使得PP+1双模预分频器有且仅有一个周期进行P+1分频, 而在其它周期都进行P分频,从而使输出周期多出了一个输入时钟周期,实现M+1 分频。该种结构也可以实现MM-1分频,进行M分频时,PP+1双模预分频器始终 工作在P+1分频模式:进行M-1分频时,在一个输出周期内,PP+1双模预分频器 有且仅有一个周期工作在P分频模式,使得输出周期少了一个输入时钟周期,从而 实现M-1分频。 Fvco mod1 mod mod P/P+1 control go 91 On-1 图2-6异步M/M+1双模预分频器 由上述分析可见,异步分频器的根本思想是,进行M+1(或M-1)分频时,找 到一个控制逻辑,使得在一个输出周期内,它的输出有且仅有一个输入时钟周期与 其它周期不同。行波计数器的各级输出构成的最大乘积项或者最小求和项恰好具有 8

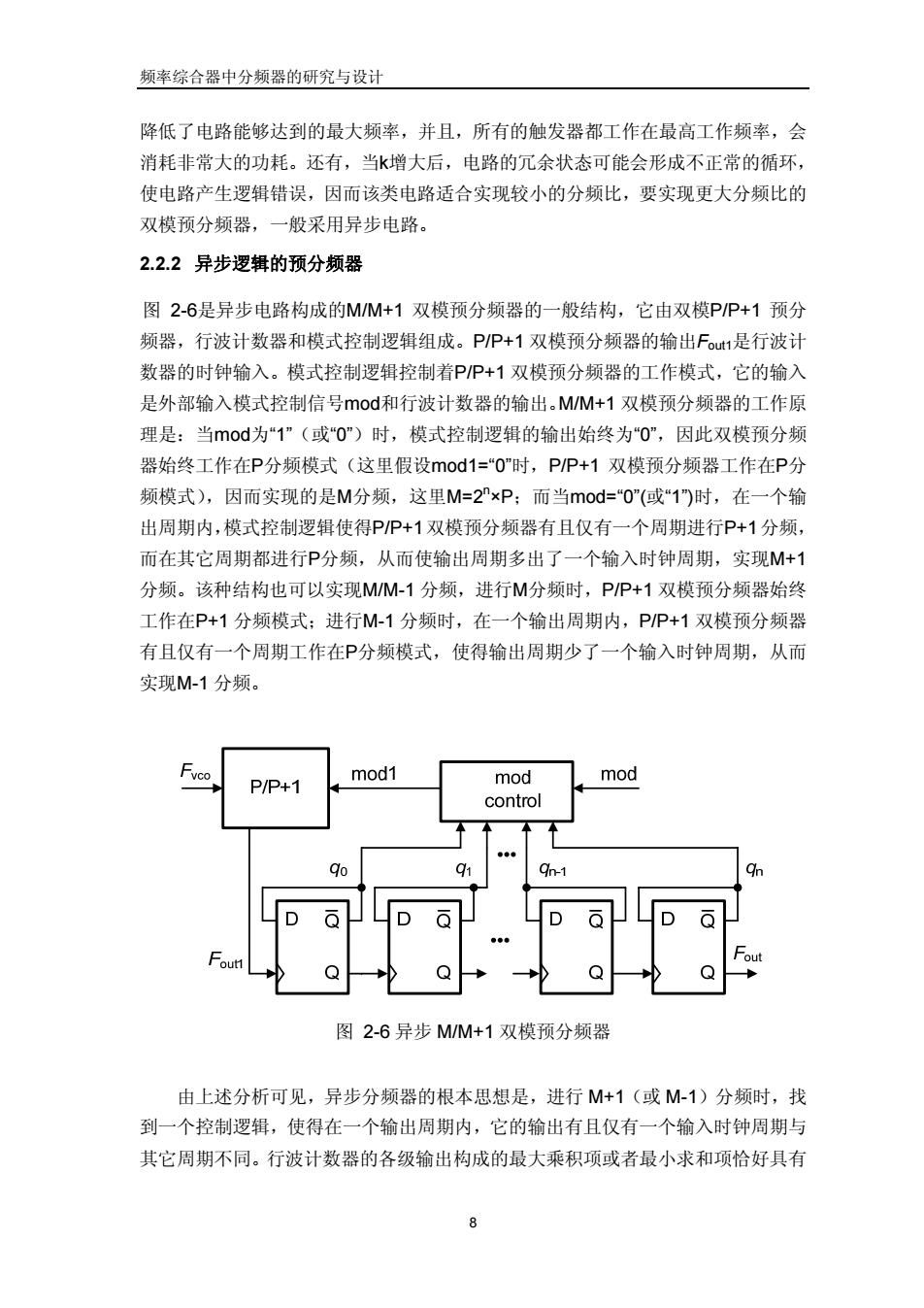

频率综合器中分频器的研究与设计 降低了电路能够达到的最大频率,并且,所有的触发器都工作在最高工作频率,会 消耗非常大的功耗。还有,当k增大后,电路的冗余状态可能会形成不正常的循环, 使电路产生逻辑错误,因而该类电路适合实现较小的分频比,要实现更大分频比的 双模预分频器,一般采用异步电路。 2.2.2 异步逻辑的预分频器 图 2-6是异步电路构成的M/M+1 双模预分频器的一般结构,它由双模P/P+1 预分 频器,行波计数器和模式控制逻辑组成。P/P+1 双模预分频器的输出Fout1是行波计 数器的时钟输入。模式控制逻辑控制着P/P+1 双模预分频器的工作模式,它的输入 是外部输入模式控制信号mod和行波计数器的输出。M/M+1 双模预分频器的工作原 理是:当mod为“1”(或“0”)时,模式控制逻辑的输出始终为“0”,因此双模预分频 器始终工作在P分频模式(这里假设mod1=“0”时,P/P+1 双模预分频器工作在P分 频模式),因而实现的是M分频,这里M=2n ×P;而当mod=“0”(或“1”)时,在一个输 出周期内,模式控制逻辑使得P/P+1双模预分频器有且仅有一个周期进行P+1分频, 而在其它周期都进行P分频,从而使输出周期多出了一个输入时钟周期,实现M+1 分频。该种结构也可以实现M/M-1 分频,进行M分频时,P/P+1 双模预分频器始终 工作在P+1 分频模式;进行M-1 分频时,在一个输出周期内,P/P+1 双模预分频器 有且仅有一个周期工作在P分频模式,使得输出周期少了一个输入时钟周期,从而 实现M-1 分频。 图 2-6 异步 M/M+1 双模预分频器 由上述分析可见,异步分频器的根本思想是,进行 M+1(或 M-1)分频时,找 到一个控制逻辑,使得在一个输出周期内,它的输出有且仅有一个输入时钟周期与 其它周期不同。行波计数器的各级输出构成的最大乘积项或者最小求和项恰好具有 8

第二章分频器的研究 这个特点,因此可以当作控制逻辑,再通过外部模式输入od的控制,便可以实 现所需要的双模预分频器。 2.2.3相位开关型预分频器16] 0° 90° ÷2 ÷2 180 ÷2 270° Feedback logic Mode 图2-7相位开关型16/17双模预分频器 图2-7是相位开关型16/17双模预分频器的结构,它由两级除2电路,除4电路,相 位选择电路和反馈控制电路构成。Mode是模式选择信号,当Mode="O”时,反馈控 制电路不起作用,相位选择电路恒定的选择某一路信号,整个电路的行为就像一个 普通的异步除16行波计数器。当Mode=”1”时,每隔8个输入周期,相位开关电路选 择延时90度的另一路信号作为输出,使输出信号多出了一个额外的输入时钟周期, 从而实现17分频,这个过程如图2-8所示。将图2-7的最后一级异步4分频器改成 其它异步分频器,可以实现其它分频比的双模预分频器。 fff DIV4(I) DIV4(Q) fswitch fout 图2-8相位开关电路时序 9

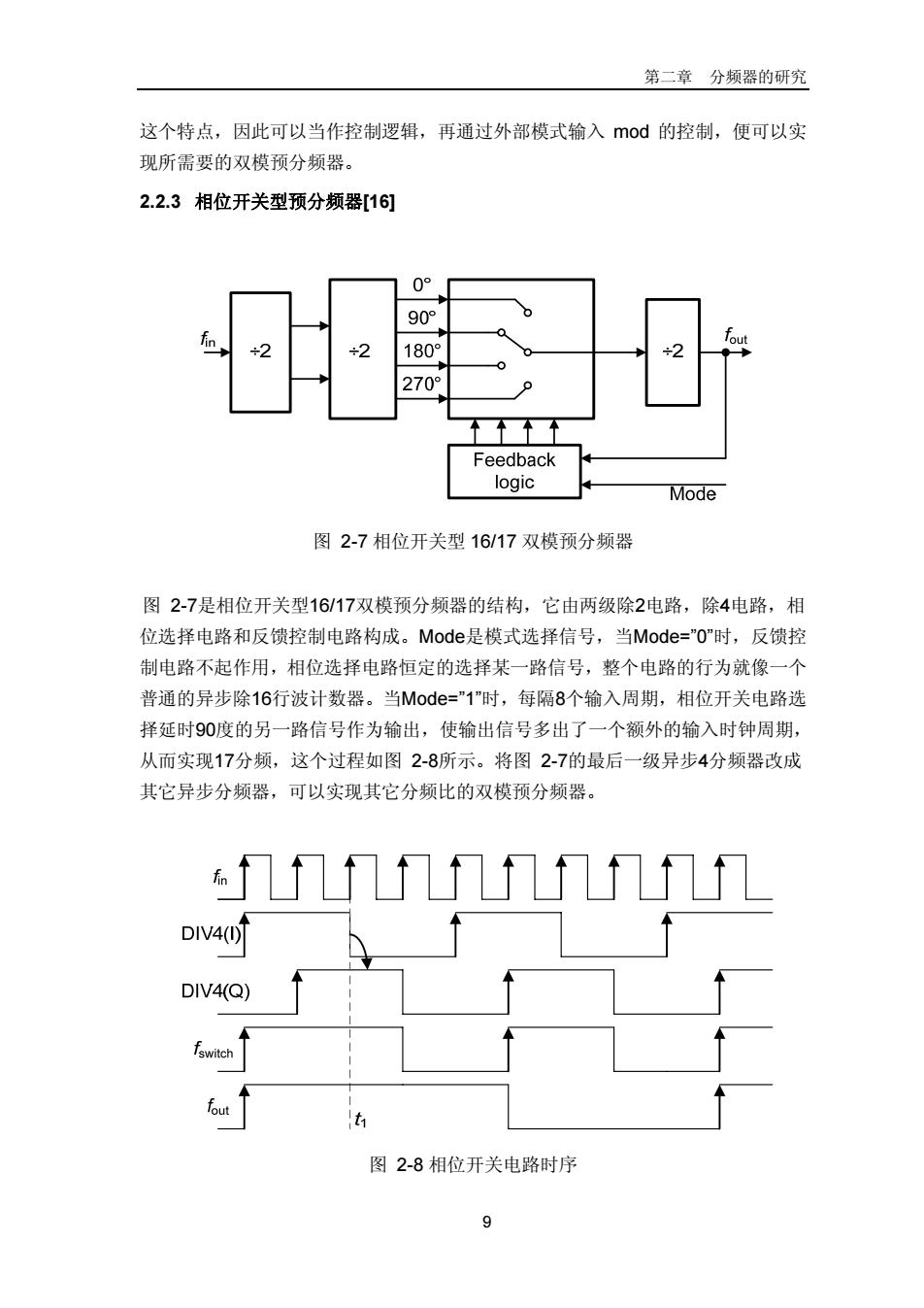

第二章 分频器的研究 这个特点,因此可以当作控制逻辑,再通过外部模式输入 mod 的控制,便可以实 现所需要的双模预分频器。 2.2.3 相位开关型预分频器[16] 图 2-7 相位开关型 16/17 双模预分频器 图 2-7是相位开关型16/17双模预分频器的结构,它由两级除2电路,除4电路,相 位选择电路和反馈控制电路构成。Mode是模式选择信号,当Mode=”0”时,反馈控 制电路不起作用,相位选择电路恒定的选择某一路信号,整个电路的行为就像一个 普通的异步除16行波计数器。当Mode=”1”时,每隔8个输入周期,相位开关电路选 择延时90度的另一路信号作为输出,使输出信号多出了一个额外的输入时钟周期, 从而实现17分频,这个过程如图 2-8所示。将图 2-7的最后一级异步4分频器改成 其它异步分频器,可以实现其它分频比的双模预分频器。 图 2-8 相位开关电路时序 9