signals is less than 1.14 degree,when the output frequency is 750MHz.When the divider is cascaded with the frequency synthesizer,the measurement result shows that,every time it is divided by 2,the phase noise performance of the output signal improves by about 6dB Key words:frequency synthesizer,divider,4/4.5 prescaler,programmable divider,quadrature signal

signals is less than 1.14 degree, when the output frequency is 750MHz. When the divider is cascaded with the frequency synthesizer, the measurement result shows that, every time it is divided by 2, the phase noise performance of the output signal improves by about 6dB. Key words: frequency synthesizer, divider, 4/4.5 prescaler, programmable divider, quadrature signal V

第一章绪论 第一章绪论 1.1研究背景 随着无线通信市场的繁荣,无线收发机己经变的无处不在。基于锁相环 (Phase-Locked Loop,PLL)的频率综合器是无线收发机的关键模块,用来产生 精细可调的本振信号,实现精确的频道选择。近年来,无线通信技术取得了突飞 猛进的发展,许多针对不同应用的无线技术标准如雨后春笋般涌现。新标准的出 现要求频率综合器能应用到多个系统和标准上,这给频率综合器的设计带来了挑 战。首先,频率综合器要能工作在更宽的频率范围,以覆盖不同频段的标准;其 次,要有更加精确的频率分辨率,以实现更小的频道间隔。有些标准即使频带相 似,也有着不同的中心频率和频带宽度,因此要求频率综合器具有更加精确的频 率分辨率。例如,HiperLAN1/HiperLAN2和802.1la标准,它们都工作在5-6GHz 频段内,频带相近,但却有着不同的中心频率和频带宽度。另外,相位噪声等其 它方面的性能要求也大都更加苛刻。 1.2频率综合器的结构 PED Charge Loop Pump Filter Divider ÷N 谷 Modulus selection 图1-1频率综合器的基本结构 图1-1是基于锁相环的频率综合器基本结构。它由鉴频鉴相器,电荷泵,低通环 路滤波器,压控振荡器(VCO),以及分频器组成。锁相环是一个负反馈系统,VCO 的输出信号被分频器进行降频处理,得到频率降低N倍的时钟信号,PFD检测分 频器输出时钟信号和参考时钟信号的相位差,然后由电荷泵将相位差转换成电压 信号,经过低通滤波器后作为VCO的输入控制电压,从而改变VCO的输出频率, 实现负反馈。系统稳定后,分频器输出时钟信号和参考时钟信号频率相等,相位 对齐,由VCO的输出可以得到稳定的高频信号。 1

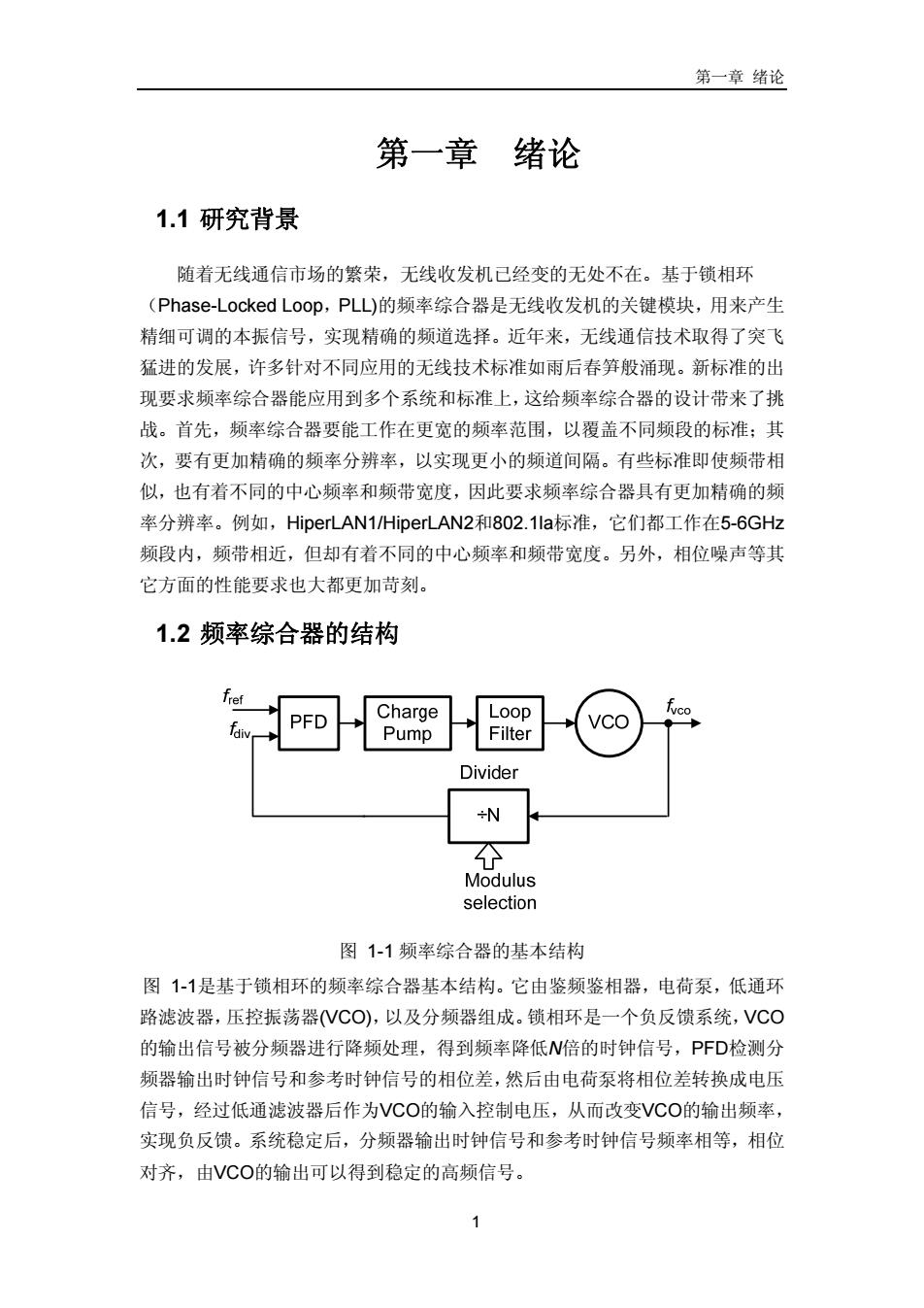

第一章 绪论 第一章 绪论 1.1 研究背景 随着无线通信市场的繁荣,无线收发机已经变的无处不在。基于锁相环 (Phase-Locked Loop,PLL)的频率综合器是无线收发机的关键模块,用来产生 精细可调的本振信号,实现精确的频道选择。近年来,无线通信技术取得了突飞 猛进的发展,许多针对不同应用的无线技术标准如雨后春笋般涌现。新标准的出 现要求频率综合器能应用到多个系统和标准上,这给频率综合器的设计带来了挑 战。首先,频率综合器要能工作在更宽的频率范围,以覆盖不同频段的标准;其 次,要有更加精确的频率分辨率,以实现更小的频道间隔。有些标准即使频带相 似,也有着不同的中心频率和频带宽度,因此要求频率综合器具有更加精确的频 率分辨率。例如,HiperLAN1/HiperLAN2和802.1la标准,它们都工作在5-6GHz 频段内,频带相近,但却有着不同的中心频率和频带宽度。另外,相位噪声等其 它方面的性能要求也大都更加苛刻。 1.2 频率综合器的结构 图 1-1 频率综合器的基本结构 图 1-1是基于锁相环的频率综合器基本结构。它由鉴频鉴相器,电荷泵,低通环 路滤波器,压控振荡器(VCO),以及分频器组成。锁相环是一个负反馈系统,VCO 的输出信号被分频器进行降频处理,得到频率降低N倍的时钟信号,PFD检测分 频器输出时钟信号和参考时钟信号的相位差,然后由电荷泵将相位差转换成电压 信号,经过低通滤波器后作为VCO的输入控制电压,从而改变VCO的输出频率, 实现负反馈。系统稳定后,分频器输出时钟信号和参考时钟信号频率相等,相位 对齐,由VCO的输出可以得到稳定的高频信号。 1

频率综合器中分频器的研究与设计 根据上面的描述,频率综合器产生如下形式的输出频率: fout =N.fret (2.1) 即锁相环把参考时钟频率放大了N倍,N是分频器的分频比。不同的频道 由它的中心频率来表征,因此,改变频道就是改变频率综合器的分频比,从而改 变输出频率。 根据分频比的形式,频率综合器分为三种基本结构:整数型频率综合器,分 数型频率综合器,以及由∑△调制器(简称SDM)实现的分数型频率综合器[1]~[4]。 整数型频率综合器的输出频率是参考频率的整数倍,因而信道间隔就等于参考频 率,如果要得到更精确的频率分辨率,必须减小参考频率。然而,减小参考频率 会带来很多坏处:它减小最大可能的环路带宽,增加锁相环的建立时间,并且增 加VCO所贡献的相位噪声[5]。分数型频率综合器可以实现参考频率分数倍的输 出频率,可以在提供窄信道间隔的同时采用大的环路带宽,可以同时实现低相位 噪声,低参考输入杂散和快速的锁定时间[⑤]。分数分频的实现方式,是动态地改 变分频器的分频比,使它们的平均值为分数,根据动态分频比的实现方式,分数 型频率综合器又分为一般的分数型频率综合器和基于∑△调制器的分数型频率综 合器。在分数型频率综合器中,在每个参考时钟周期,分频器的输出信号与参考 信号不是始终对齐,而是时而超前,时而滞后,实现的是动态锁定。这种动态锁 定会产生量化噪声,进而会在输出载波附近引起分数杂散。对于低的分数频率, 这些分数杂散很容易落入带内,从而降低相位噪声性能[6]。采用∑△调制器实现 的分数型频率综合器,可以将量化噪声的能量整形到高频,进而用低通滤波器滤 除,但量化噪声仍然影响带外的相位噪声性能。 1.3分频器在频率综合器的作用 分频器在频率综合器中占有非常重要的地位,频率综合器的三种结构本质上 是根据分频器的种类进行区分的。它应用于频率综合器的反馈支路,参考时钟频 率确定后,它的分频比决定频率综合器的输出频率。频率综合器进行信道的选择, 实际上是改变分频器的分频比,因此要求分频器的分频比可编程,分频比的可编 程范围影响频率综合器的工作频率范围。即使对于同一信道,为了实现小数分频 也必须实时的改变分频器的分频比,同样要求分频比可编程的分频器,也称为多 模分频器。分频器接收的是VCO的输出信号,工作在最高工作频率,因此它消耗 非常大的功耗,它的速度决定着频率综合器的速度。另外,分频器还影响频率综 合器的相位噪声性能,除了分频器自身的相位噪声贡献外,频率综合器中其它模 块对相位噪声的贡献也与分频器有关,因为分频器的分频比影响着各模块到输出 的传输函数[7]。SDM的量化噪声会影响带外的相位噪声性能,分频器的实现方 2

频率综合器中分频器的研究与设计 根据上面的描述,频率综合器产生如下形式的输出频率: (2.1) out ref f Nf = ⋅ 即锁相环把参考时钟频率放大了 N 倍,N 是分频器的分频比。不同的频道 由它的中心频率来表征,因此,改变频道就是改变频率综合器的分频比,从而改 变输出频率。 根据分频比的形式,频率综合器分为三种基本结构:整数型频率综合器,分 数型频率综合器,以及由∑∆调制器(简称SDM)实现的分数型频率综合器[1]~ [4]。 整数型频率综合器的输出频率是参考频率的整数倍,因而信道间隔就等于参考频 率,如果要得到更精确的频率分辨率,必须减小参考频率。然而,减小参考频率 会带来很多坏处:它减小最大可能的环路带宽,增加锁相环的建立时间,并且增 加VCO所贡献的相位噪声[5]。分数型频率综合器可以实现参考频率分数倍的输 出频率,可以在提供窄信道间隔的同时采用大的环路带宽,可以同时实现低相位 噪声,低参考输入杂散和快速的锁定时间[5]。分数分频的实现方式,是动态地改 变分频器的分频比,使它们的平均值为分数,根据动态分频比的实现方式,分数 型频率综合器又分为一般的分数型频率综合器和基于∑∆调制器的分数型频率综 合器。在分数型频率综合器中,在每个参考时钟周期,分频器的输出信号与参考 信号不是始终对齐,而是时而超前,时而滞后,实现的是动态锁定。这种动态锁 定会产生量化噪声,进而会在输出载波附近引起分数杂散。对于低的分数频率, 这些分数杂散很容易落入带内,从而降低相位噪声性能[6]。采用∑∆调制器实现 的分数型频率综合器,可以将量化噪声的能量整形到高频,进而用低通滤波器滤 除,但量化噪声仍然影响带外的相位噪声性能。 1.3 分频器在频率综合器的作用 分频器在频率综合器中占有非常重要的地位,频率综合器的三种结构本质上 是根据分频器的种类进行区分的。它应用于频率综合器的反馈支路,参考时钟频 率确定后,它的分频比决定频率综合器的输出频率。频率综合器进行信道的选择, 实际上是改变分频器的分频比,因此要求分频器的分频比可编程,分频比的可编 程范围影响频率综合器的工作频率范围。即使对于同一信道,为了实现小数分频 也必须实时的改变分频器的分频比,同样要求分频比可编程的分频器,也称为多 模分频器。分频器接收的是VCO的输出信号,工作在最高工作频率,因此它消耗 非常大的功耗,它的速度决定着频率综合器的速度。另外,分频器还影响频率综 合器的相位噪声性能,除了分频器自身的相位噪声贡献外,频率综合器中其它模 块对相位噪声的贡献也与分频器有关,因为分频器的分频比影响着各模块到输出 的传输函数[7]。SDM的量化噪声会影响带外的相位噪声性能,分频器的实现方 2

第一章绪论 式影响着量化噪声对相位噪声的贡献[7][8][9]。 另外,分频器还有一个非常重要的应用,它常被接在频率综合器之后,用以 扩展频率范围10[11][12]或者实现正交信号引13]。 1.4研究内容及贡献 在科研工作及论文写作过程中,阅读了大量分频器相关的文献与资料,对信 号分频技术做了比较全面的分析与总结,具体的工作如下: 1.以频率综合器的应用背景为基础,介绍了锁相环型频率综合器的基本原理及 分频器在频率综合器中的作用; 2.按从大到小的顺序分析研究了频率综合器中各种分频器的结构,包括多模可 编程分频器,双模预分频器,和分频器基本实现单元的结构,比较了它们性能上 的优劣。 3.提出异步4/4.5型双模预分频器结构,具有较少的晶体管数目,可以节省面积 和降低功耗。 4.提出了一种新型的S计数器结构,可以很好的与检测“2”结束状态的P计数器相 配合,正确实现多模可编程分频器的功能,达到较高的速度。 5.在SMIC0.18 um CMOS工艺下,设计并实现了一款低相位噪声,高正交相位 精度的正交分频器,完成了芯片的测试工作。 1.5论文的组织结构 本论文对分频器在频率综合器中的应用进行了系统的分析和研究,论文共分 为六个部分,具体组织结构如下: 第一章是绪论,介绍了本论文的研究背景和本论文的主要工作。 第二章介绍了频率综合器中各类分频器的原理和结构,比较了它们性能上的 优劣。 第三章详细分析了基于双模预分频器的多模可编程分频器。提出并分析了异 步4/4.5双模预分频器结构。指出检测“2”结束状态的P计数器在速度上的优势,以 及它引起的S计数器难以实现S=1的问题,分析问题的原因,提出新型的S计数 器结构来解决这个问题,使电路达到较高的速度。 第四章设计实现一款低相位噪声,高正交相位精度的正交分频器。分析了二 分频电路的动态特性,给出了电路的设计考虑。 第五章给出了正交分频器的测试结果,并对测试结果进行了分析。 第六章对论文进行总结,并对今后的工作进行了展望。 3

第一章 绪论 式影响着量化噪声对相位噪声的贡献[7] [8][9]。 另外,分频器还有一个非常重要的应用,它常被接在频率综合器之后,用以 扩展频率范围[10][11][12]或者实现正交信号[13]。 1.4 研究内容及贡献 在科研工作及论文写作过程中,阅读了大量分频器相关的文献与资料,对信 号分频技术做了比较全面的分析与总结,具体的工作如下: 1.以频率综合器的应用背景为基础,介绍了锁相环型频率综合器的基本原理及 分频器在频率综合器中的作用; 2.按从大到小的顺序分析研究了频率综合器中各种分频器的结构,包括多模可 编程分频器,双模预分频器,和分频器基本实现单元的结构,比较了它们性能上 的优劣。 3.提出异步4/4.5型双模预分频器结构,具有较少的晶体管数目,可以节省面积 和降低功耗。 4.提出了一种新型的S计数器结构,可以很好的与检测“2”结束状态的P计数器相 配合,正确实现多模可编程分频器的功能,达到较高的速度。 5.在SMIC 0.18μm CMOS工艺下,设计并实现了一款低相位噪声,高正交相位 精度的正交分频器,完成了芯片的测试工作。 1.5 论文的组织结构 本论文对分频器在频率综合器中的应用进行了系统的分析和研究,论文共分 为六个部分,具体组织结构如下: 第一章是绪论,介绍了本论文的研究背景和本论文的主要工作。 第二章介绍了频率综合器中各类分频器的原理和结构,比较了它们性能上的 优劣。 第三章详细分析了基于双模预分频器的多模可编程分频器。提出并分析了异 步4/4.5双模预分频器结构。指出检测“2”结束状态的P计数器在速度上的优势,以 及它引起的S计数器难以实现S=1的问题,分析问题的原因,提出新型的S计数 器结构来解决这个问题,使电路达到较高的速度。 第四章设计实现一款低相位噪声,高正交相位精度的正交分频器。分析了二 分频电路的动态特性,给出了电路的设计考虑。 第五章给出了正交分频器的测试结果,并对测试结果进行了分析。 第六章对论文进行总结,并对今后的工作进行了展望。 3

频率综合器中分频器的研究与设计 第二章分频器的研究 2.1多模可编程分频器 分频器最常见的应用是作为锁相环的反馈支路,它需要采用多模的可编程分频 器,以实现频道的切换以及实现小数分频。下面介绍三种常用的多模可编程分频器 结构。 2.1.1可预置数的可编程分频器 这种可编程分频器由计数逻辑和计数结束逻辑(End Of Count Logic,简称 E0C)组成[14J,如图2-1所示。计数逻辑基于可预置数的二分频器,各级二分频 器连接成行波计数器的形式。分频器的工作周期可分为两个阶段,即正常计数阶段 和置数阶段,由置数信号LD控制。正常计数期间,LD信号为低电平,EOC检测电 路的输出状态,当检测到结束状态(比如全零状态)后,将LD信号置为高电平,电 路进入置数阶段,各基本单元开始进行置数,置数完成后,EOC检测到输出不再是 结束状态,因此LD信号又变为低电平,电路再一次进入计数状态,在下一个时钟上 升沿到来时,将从所置之数开始进行递减计数,以此循环。LD信号同时也是输出信 号,因为它的输出周期与输入信号的周期之比就等于所置之数。改变所预设的值就 改变了分频器的分频比,实现分频比的可编程。 EOC LD 92 qi go P3 9P2 P1 Po PD D PI bitcell bitcell bitcell bitcell CLK >clk clk >clk clk LD LD LD LD 图2-1基于可置数单元的可编程分频器 该种类型的可编程分频器能够实现的分频范围是最大的,它的最小分频比是 2(在这里分频比为0没有定义),最大分频比与级数有关,假设分频器的级数为M, 则最大分频比是2“一1。通过选取级数,理论上可实现的分频比是无穷大。由于预

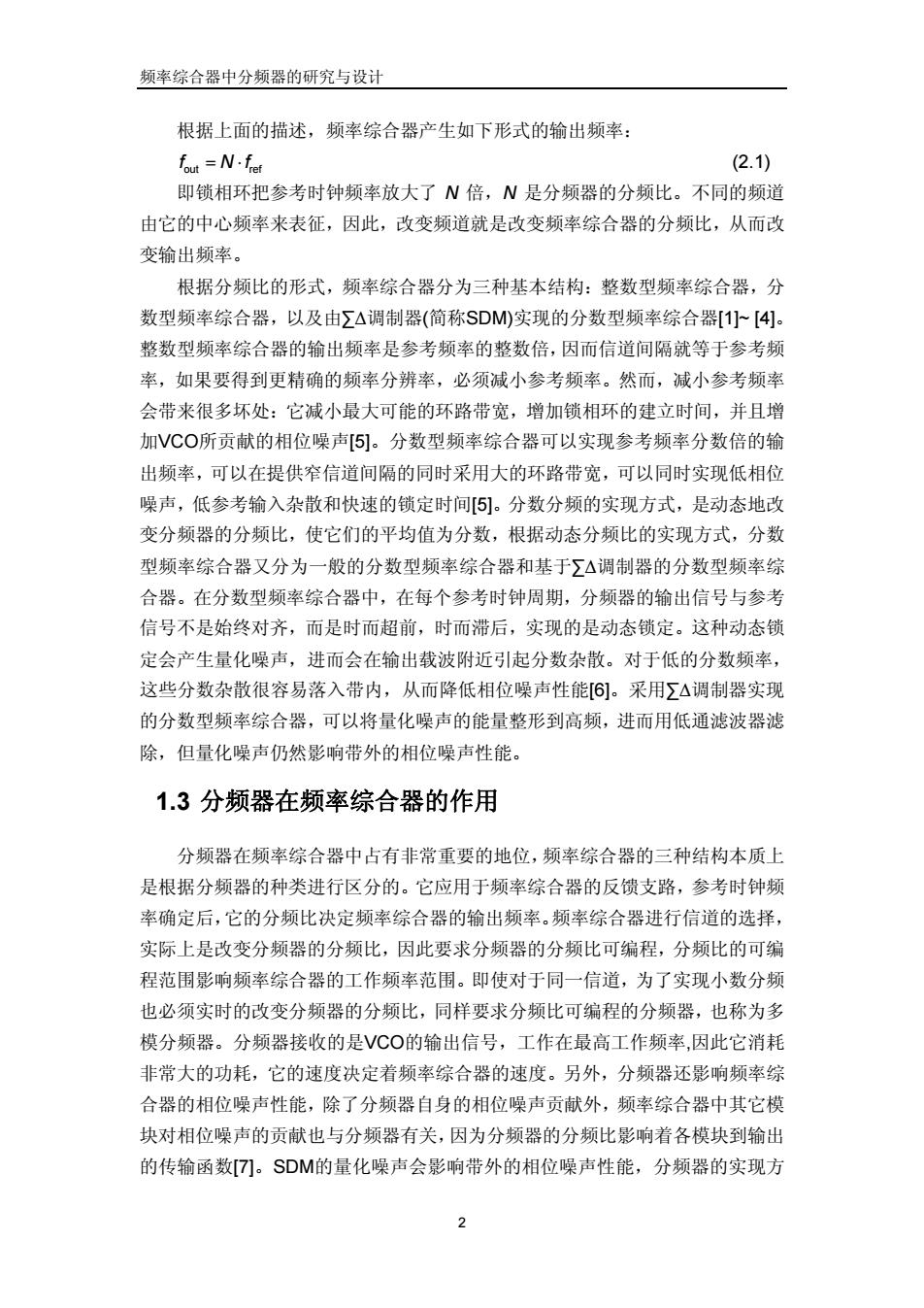

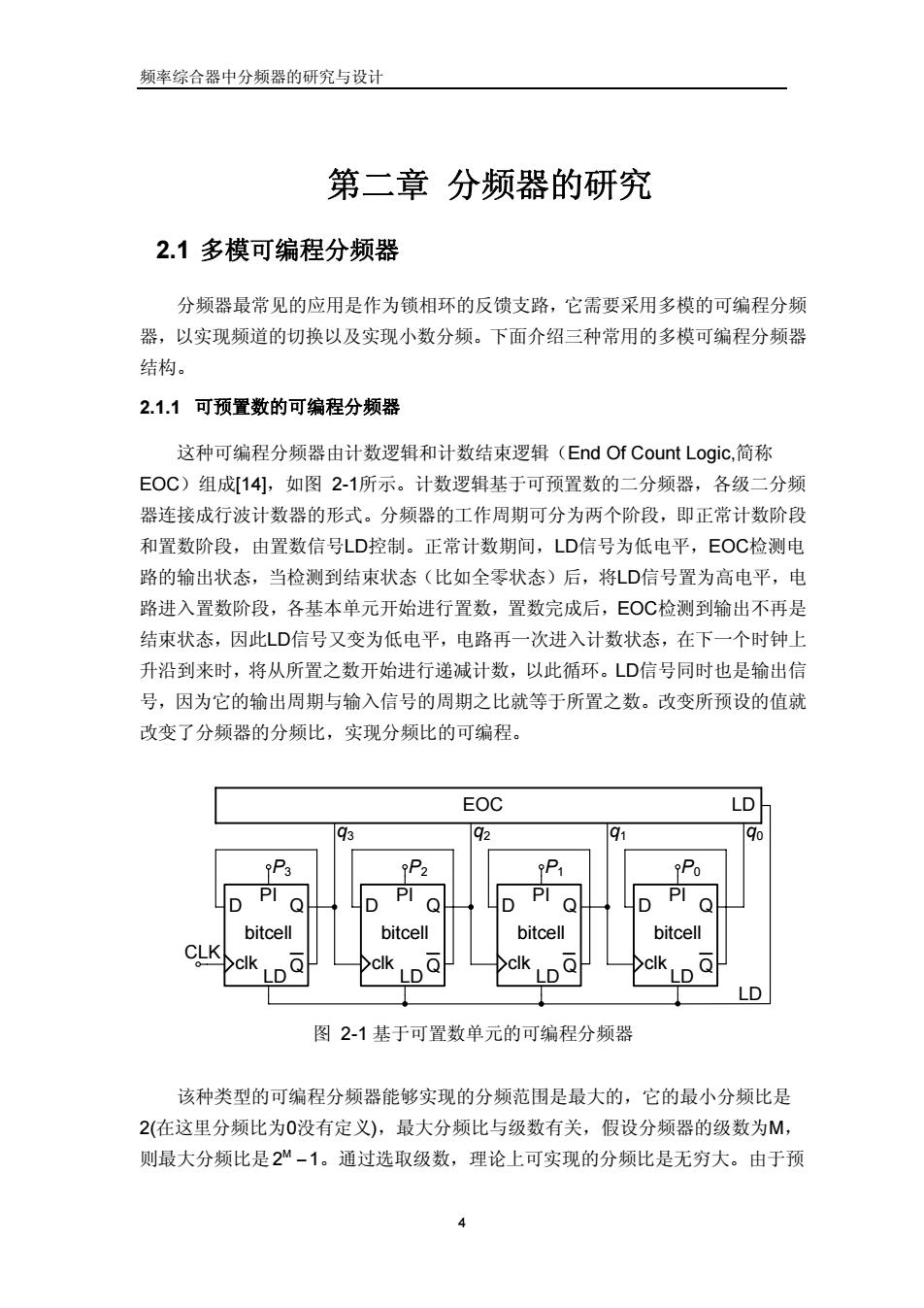

频率综合器中分频器的研究与设计 第二章 分频器的研究 2.1 多模可编程分频器 分频器最常见的应用是作为锁相环的反馈支路,它需要采用多模的可编程分频 器,以实现频道的切换以及实现小数分频。下面介绍三种常用的多模可编程分频器 结构。 2.1.1 可预置数的可编程分频器 这种可编程分频器由计数逻辑和计数结束逻辑(End Of Count Logic,简称 EOC)组成[14],如图 2-1所示。计数逻辑基于可预置数的二分频器,各级二分频 器连接成行波计数器的形式。分频器的工作周期可分为两个阶段,即正常计数阶段 和置数阶段,由置数信号LD控制。正常计数期间,LD信号为低电平,EOC检测电 路的输出状态,当检测到结束状态(比如全零状态)后,将LD信号置为高电平,电 路进入置数阶段,各基本单元开始进行置数,置数完成后,EOC检测到输出不再是 结束状态,因此LD信号又变为低电平,电路再一次进入计数状态,在下一个时钟上 升沿到来时,将从所置之数开始进行递减计数,以此循环。LD信号同时也是输出信 号,因为它的输出周期与输入信号的周期之比就等于所置之数。改变所预设的值就 改变了分频器的分频比,实现分频比的可编程。 PI clk D Q Q LD PI clk D Q Q LD PI clk D Q Q LD PI clk D Q Q LD q3 q2 q1 q0 P3 P2 P1 P0 CLK LD bitcell bitcell bitcell bitcell EOC LD 图 2-1 基于可置数单元的可编程分频器 该种类型的可编程分频器能够实现的分频范围是最大的,它的最小分频比是 2(在这里分频比为0没有定义),最大分频比与级数有关,假设分频器的级数为M, 则最大分频比是 。通过选取级数,理论上可实现的分频比是无穷大。由于预 M2 −1 4