频率综合器中分频器的研究与设计 与2.2.1和2.2.2节介绍的预分频器相比,相位开关型双模预分频器没有额外的 逻辑门存在于预分频器的关键路径上,所以它能实现更高的速度,但是它存在相位 选择电路,实现比较复杂。相位开关电路还存在毛刺问题[16],毛刺消除电路进一 步增加了电路的复杂性。 2.3高速电路结构 同CO一样,预分频器是频率综合器中工作频率最高的模块,它们的实现需要 采用高速的电路结构。再生型模拟分频器和注入锁定分频器等模拟结构,可以达到 非常高的速度,而且注入锁定分频器在高速工作的同时还消耗非常低的功耗。但模 拟结构占用很大的面积,而且只能实现单模分频器,因此本文不再讨论。由2.2节 的分析可知,触发器是构建双模预分频器的关键模块,采用CMOS逻辑的触发器或 锁存器,具有逻辑简单,没有静态功耗等优点。但随着频率的升高,cos逻辑的 动态功耗将急剧增大,而且,由于晶体管数目大,需要满摆幅工作,它难以达到很 高的速度。高速锁存器或触发器,常常采用真单相时钟(True Single Phase Clock, 简称TSPC)和电流模式逻辑(Current Mode Logic,简称CML)结构。 2.3.1TSPC电路 TSPC电路最早出现在80年代末17][18]。由于采用单相位时钟,并减少了晶体 管的个数,因此TSPC可以达到较高的速度。九十年代末以来,TSPC得到了越来 越广泛的应用。它的结构也在不断的改进,比如出现了E-TSPC(The Extended True Single Phase Clock)结构19]。 VDD S QB glitch -- 图2-9真单相位时钟结构和时序 图2-9左图是最基本的TSPC触发器结构18]。它基于预充电逻辑,其中第二级 是预充电电路,当时钟为低电平时,第一级对输入数据进行采样,第二级被预充电 10

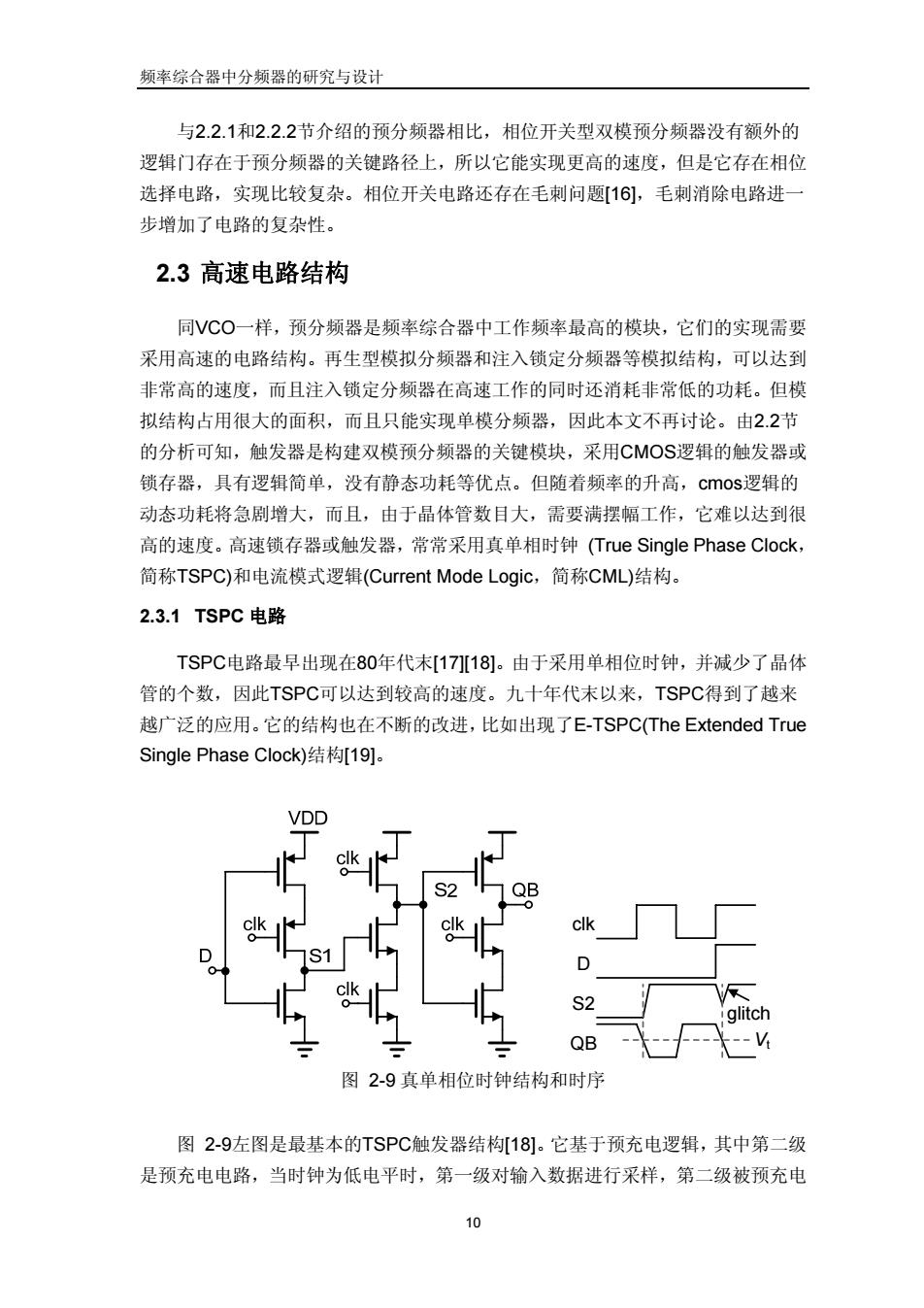

频率综合器中分频器的研究与设计 与2.2.1和2.2.2节介绍的预分频器相比,相位开关型双模预分频器没有额外的 逻辑门存在于预分频器的关键路径上,所以它能实现更高的速度,但是它存在相位 选择电路,实现比较复杂。相位开关电路还存在毛刺问题[16],毛刺消除电路进一 步增加了电路的复杂性。 2.3 高速电路结构 同VCO一样,预分频器是频率综合器中工作频率最高的模块,它们的实现需要 采用高速的电路结构。再生型模拟分频器和注入锁定分频器等模拟结构,可以达到 非常高的速度,而且注入锁定分频器在高速工作的同时还消耗非常低的功耗。但模 拟结构占用很大的面积,而且只能实现单模分频器,因此本文不再讨论。由2.2节 的分析可知,触发器是构建双模预分频器的关键模块,采用CMOS逻辑的触发器或 锁存器,具有逻辑简单,没有静态功耗等优点。但随着频率的升高,cmos逻辑的 动态功耗将急剧增大,而且,由于晶体管数目大,需要满摆幅工作,它难以达到很 高的速度。高速锁存器或触发器,常常采用真单相时钟 (True Single Phase Clock, 简称TSPC)和电流模式逻辑(Current Mode Logic,简称CML)结构。 2.3.1 TSPC 电路 TSPC电路最早出现在80年代末[17][18]。由于采用单相位时钟,并减少了晶体 管的个数,因此TSPC可以达到较高的速度。九十年代末以来,TSPC得到了越来 越广泛的应用。它的结构也在不断的改进,比如出现了E-TSPC(The Extended True Single Phase Clock)结构[19]。 clk D S2 QB Vt glitch 图 2-9 真单相位时钟结构和时序 图 2-9左图是最基本的TSPC触发器结构[18]。它基于预充电逻辑,其中第二级 是预充电电路,当时钟为低电平时,第一级对输入数据进行采样,第二级被预充电 10

第二章分频器的研究 至高电平,从而使第三级处于高阻状态,由寄生电容保持电路的状态:当时钟为高 电平时,第一级在前一阶段采样的数据开始向输出传递,根据采样到的数据的不同, 会通过不同的传输路径。如果S1节点的数据为“1”,则发生S1→S2→QB的传递: 如果S1节点的数据为“0”,则发生S2→QB的传递,因为S2节点在前一阶段被预 充电为“1”,所以它直接打开第三级的下拉路径,将QB节点下拉到0”。 图2-9左图的电路存在着竞争冒险。当D节点数据连续两个输入时钟周期为 “0”时,可能在输出端产生“毛刺”,如图2-9右图所示。因为,第一个输入时钟周期 结束后QB被置为“1”,第二个时钟的低电平时,S2被预充电为“1”,QB动态保持在 “1”状态:当第二个时钟的高电平到来后,S2开始从“1”到“0”变化,在它降到低于 第三级的阈值电压(图2-9右图中的M)之前,第三级的下拉路径开启,使得QB 从“1”向“0”变化,直到S2节点电压低于第三级的阈值电压之后,QB点电压再变回 “1”。如果第二级的下拉不够快,则毛刺可能会使后续电路发生错误的翻转。图2-10 给出了解决了这个问题的电路结构。第三级的下拉路径多出一个晶体管,因而降低 了电路的速度。 VDD 图2-10消除毛刺的TSPC结构20] 图2-11E-TSPC结构21] 11

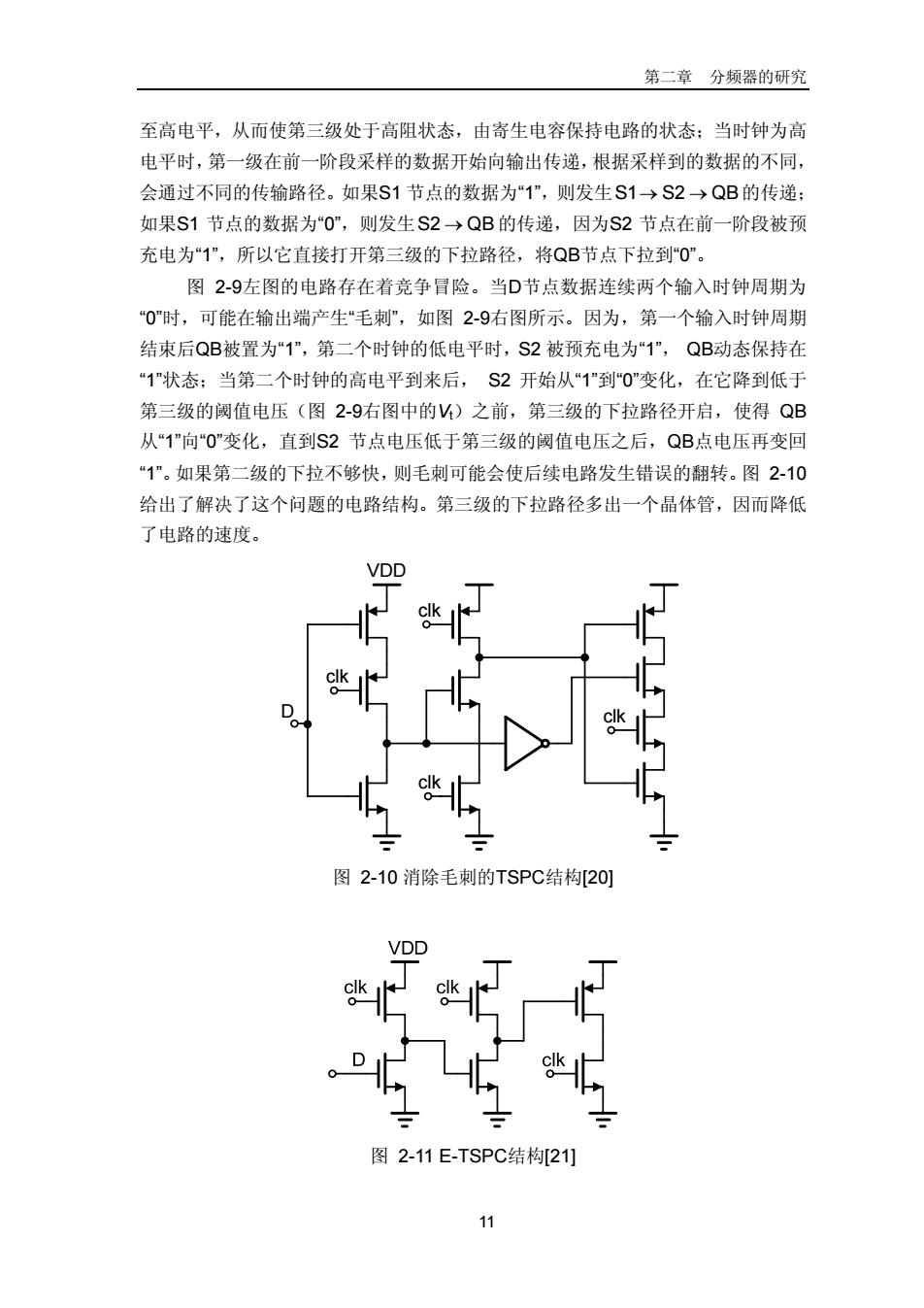

第二章 分频器的研究 至高电平,从而使第三级处于高阻状态,由寄生电容保持电路的状态;当时钟为高 电平时,第一级在前一阶段采样的数据开始向输出传递,根据采样到的数据的不同, 会通过不同的传输路径。如果S1 节点的数据为“1”,则发生 的传递; 如果S1 节点的数据为“0”,则发生S2 的传递,因为S2 节点在前一阶段被预 充电为“1”,所以它直接打开第三级的下拉路径,将QB节点下拉到“0”。 S1 S2 QB → → → QB 图 2-9左图的电路存在着竞争冒险。当D节点数据连续两个输入时钟周期为 “0”时,可能在输出端产生“毛刺”,如图 2-9右图所示。因为,第一个输入时钟周期 结束后QB被置为“1”,第二个时钟的低电平时,S2 被预充电为“1”, QB动态保持在 “1”状态;当第二个时钟的高电平到来后, S2 开始从“1”到“0”变化,在它降到低于 第三级的阈值电压(图 2-9右图中的Vt)之前,第三级的下拉路径开启,使得 QB 从“1”向“0”变化,直到S2 节点电压低于第三级的阈值电压之后,QB点电压再变回 “1”。如果第二级的下拉不够快,则毛刺可能会使后续电路发生错误的翻转。图 2-10 给出了解决了这个问题的电路结构。第三级的下拉路径多出一个晶体管,因而降低 了电路的速度。 D clk clk clk clk VDD 图 2-10 消除毛刺的TSPC结构[20] 图 2-11 E-TSPC结构[21] 11

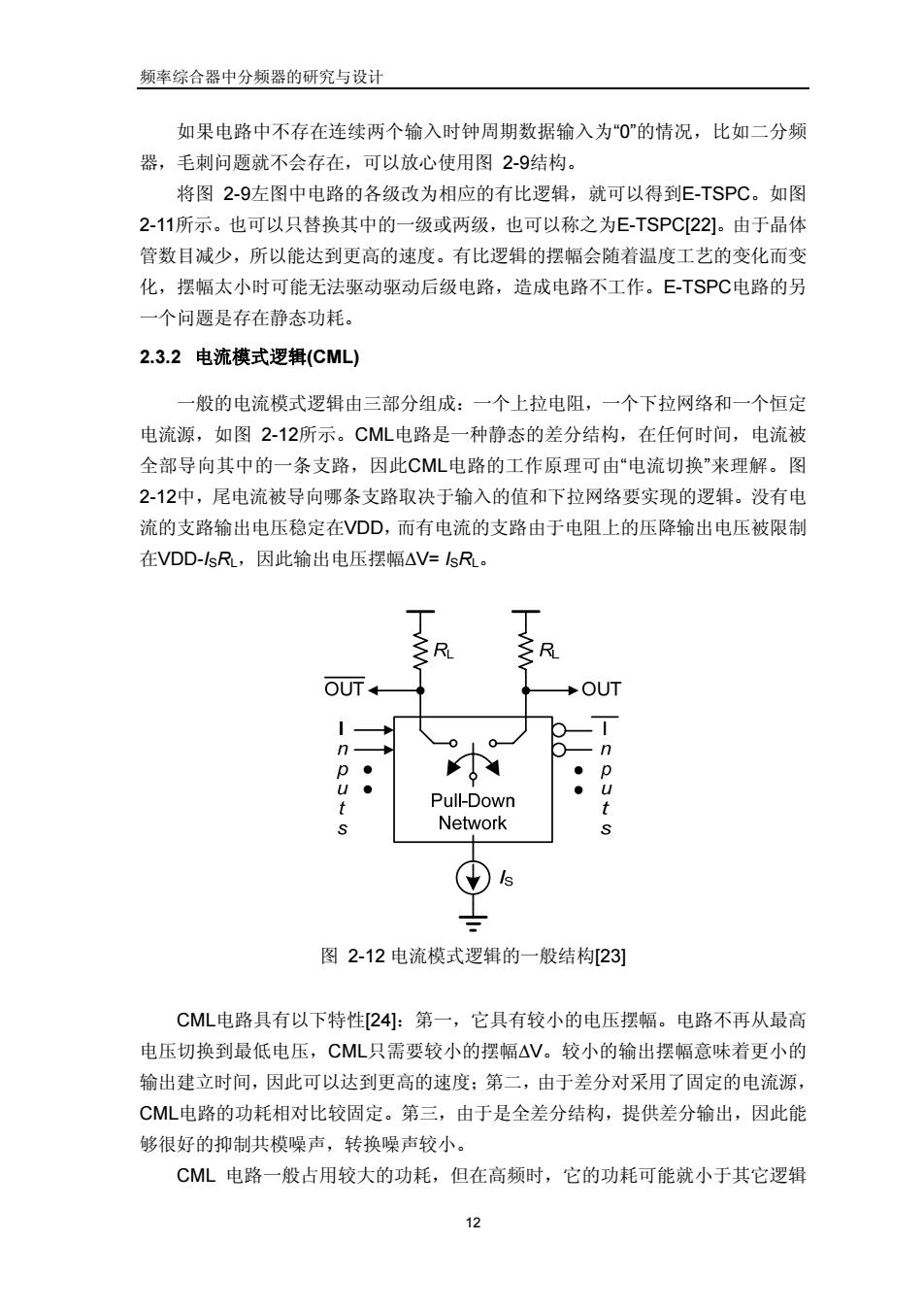

频率综合器中分频器的研究与设计 如果电路中不存在连续两个输入时钟周期数据输入为“0”的情况,比如二分频 器,毛刺问题就不会存在,可以放心使用图2-9结构。 将图2-9左图中电路的各级改为相应的有比逻辑,就可以得到E-TSPC。如图 2-11所示。也可以只替换其中的一级或两级,也可以称之为E-TSPC22]。由于晶体 管数目减少,所以能达到更高的速度。有比逻辑的摆幅会随着温度工艺的变化而变 化,摆幅太小时可能无法驱动驱动后级电路,造成电路不工作。E-TSPC电路的另 一个问题是存在静态功耗。 2.3.2电流模式逻辑(CML) 一般的电流模式逻辑由三部分组成:一个上拉电阻,一个下拉网络和一个恒定 电流源,如图2-12所示。CML电路是一种静态的差分结构,在任何时间,电流被 全部导向其中的一条支路,因此CML电路的工作原理可由“电流切换”来理解。图 2-12中,尾电流被导向哪条支路取决于输入的值和下拉网络要实现的逻辑。没有电 流的支路输出电压稳定在VDD,而有电流的支路由于电阻上的压降输出电压被限制 在VDD-sR,因此输出电压摆幅△V=sR。 OUT OUT n -n Pull-Down ● Network 5 图2-12电流模式逻辑的一般结构23] CML电路具有以下特性24小:第一,它具有较小的电压摆幅。电路不再从最高 电压切换到最低电压,CML只需要较小的摆幅△V。较小的输出摆幅意味着更小的 输出建立时间,因此可以达到更高的速度:第二,由于差分对采用了固定的电流源, CML电路的功耗相对比较固定。第三,由于是全差分结构,提供差分输出,因此能 够很好的抑制共模噪声,转换噪声较小。 CML电路一般占用较大的功耗,但在高频时,它的功耗可能就小于其它逻辑 12

频率综合器中分频器的研究与设计 如果电路中不存在连续两个输入时钟周期数据输入为“0”的情况,比如二分频 器,毛刺问题就不会存在,可以放心使用图 2-9结构。 将图 2-9左图中电路的各级改为相应的有比逻辑,就可以得到E-TSPC。如图 2-11所示。也可以只替换其中的一级或两级,也可以称之为E-TSPC[22]。由于晶体 管数目减少,所以能达到更高的速度。有比逻辑的摆幅会随着温度工艺的变化而变 化,摆幅太小时可能无法驱动驱动后级电路,造成电路不工作。E-TSPC电路的另 一个问题是存在静态功耗。 2.3.2 电流模式逻辑(CML) 一般的电流模式逻辑由三部分组成:一个上拉电阻,一个下拉网络和一个恒定 电流源,如图 2-12所示。CML电路是一种静态的差分结构,在任何时间,电流被 全部导向其中的一条支路,因此CML电路的工作原理可由“电流切换”来理解。图 2-12中,尾电流被导向哪条支路取决于输入的值和下拉网络要实现的逻辑。没有电 流的支路输出电压稳定在VDD,而有电流的支路由于电阻上的压降输出电压被限制 在VDD-ISRL,因此输出电压摆幅∆V= ISRL。 图 2-12 电流模式逻辑的一般结构[23] CML电路具有以下特性[24]:第一,它具有较小的电压摆幅。电路不再从最高 电压切换到最低电压,CML只需要较小的摆幅∆V。较小的输出摆幅意味着更小的 输出建立时间,因此可以达到更高的速度;第二,由于差分对采用了固定的电流源, CML电路的功耗相对比较固定。第三,由于是全差分结构,提供差分输出,因此能 够很好的抑制共模噪声,转换噪声较小。 CML 电路一般占用较大的功耗,但在高频时,它的功耗可能就小于其它逻辑 12

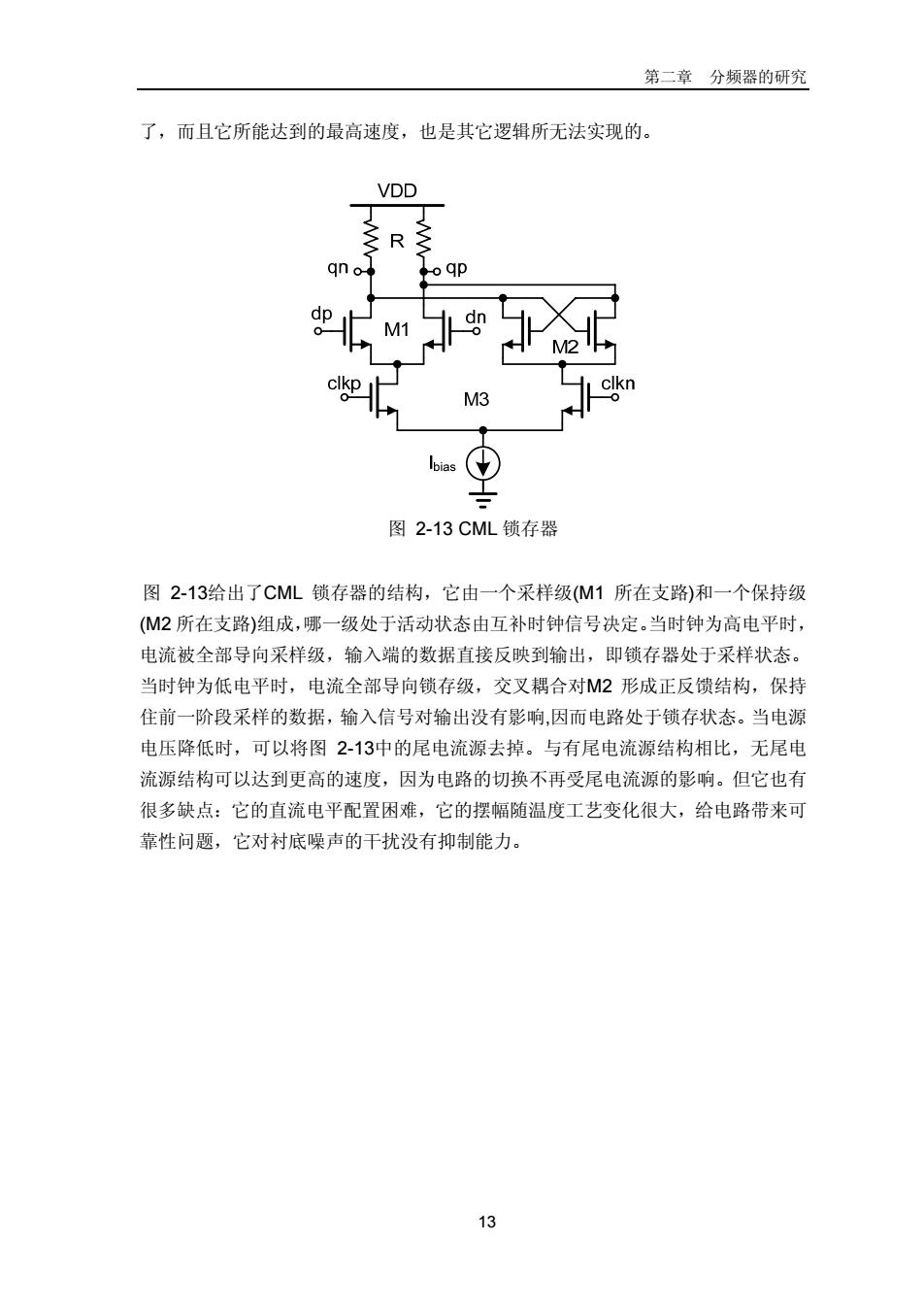

第二章分频器的研究 了,而且它所能达到的最高速度,也是其它逻辑所无法实现的。 VDD R oqp dp M1 M3 cn 图2-13CML锁存器 图2-13给出了CML锁存器的结构,它由一个采样级(M1所在支路)和一个保持级 (M2所在支路)组成,哪一级处于活动状态由互补时钟信号决定。当时钟为高电平时, 电流被全部导向采样级,输入端的数据直接反映到输出,即锁存器处于采样状态。 当时钟为低电平时,电流全部导向锁存级,交叉耦合对M2形成正反馈结构,保持 住前一阶段采样的数据,输入信号对输出没有影响,因而电路处于锁存状态。当电源 电压降低时,可以将图2-13中的尾电流源去掉。与有尾电流源结构相比,无尾电 流源结构可以达到更高的速度,因为电路的切换不再受尾电流源的影响。但它也有 很多缺点:它的直流电平配置困难,它的摆幅随温度工艺变化很大,给电路带来可 靠性问题,它对衬底噪声的干扰没有抑制能力。 13

第二章 分频器的研究 了,而且它所能达到的最高速度,也是其它逻辑所无法实现的。 图 2-13 CML 锁存器 图 2-13给出了CML 锁存器的结构,它由一个采样级(M1 所在支路)和一个保持级 (M2 所在支路)组成,哪一级处于活动状态由互补时钟信号决定。当时钟为高电平时, 电流被全部导向采样级,输入端的数据直接反映到输出,即锁存器处于采样状态。 当时钟为低电平时,电流全部导向锁存级,交叉耦合对M2 形成正反馈结构,保持 住前一阶段采样的数据,输入信号对输出没有影响,因而电路处于锁存状态。当电源 电压降低时,可以将图 2-13中的尾电流源去掉。与有尾电流源结构相比,无尾电 流源结构可以达到更高的速度,因为电路的切换不再受尾电流源的影响。但它也有 很多缺点:它的直流电平配置困难,它的摆幅随温度工艺变化很大,给电路带来可 靠性问题,它对衬底噪声的干扰没有抑制能力。 13

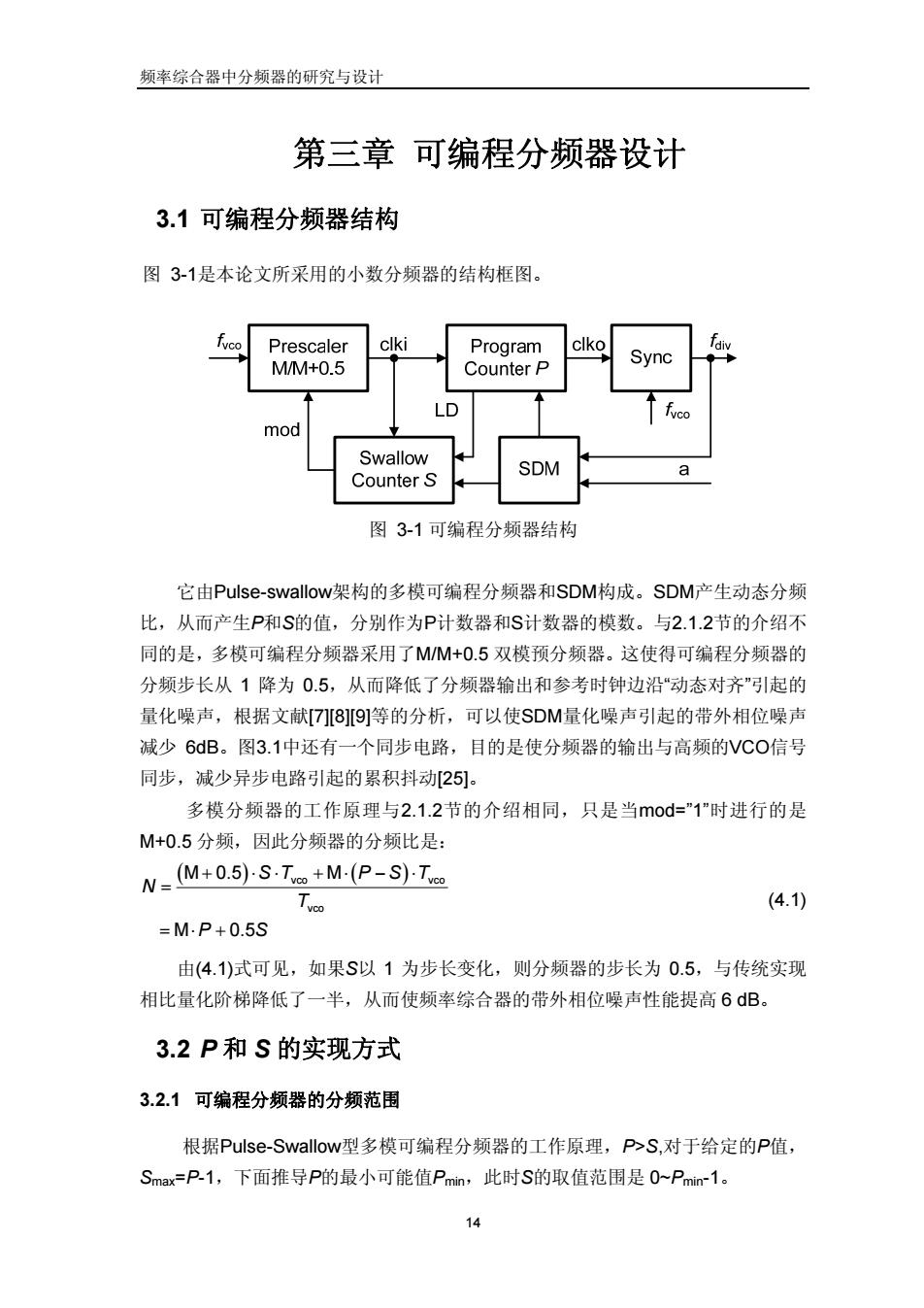

频率综合器中分频器的研究与设计 第三章可编程分频器设计 3.1可编程分频器结构 图3-1是本论文所采用的小数分频器的结构框图。 fvco Prescaler clki Program clko M/M+0.5 Counter P Sync LD mod Swallow SDM Counter S a 图3-1可编程分频器结构 它由Pulse-swallow架构的多模可编程分频器和SDM构成。SDM产生动态分频 比,从而产生P和S的值,分别作为P计数器和S计数器的模数。与2.1.2节的介绍不 同的是,多模可编程分频器采用了MM+0.5双模预分频器。这使得可编程分频器的 分频步长从1降为0.5,从而降低了分频器输出和参考时钟边沿“动态对齐”引起的 量化噪声,根据文献[7][8][9]等的分析,可以使SDM量化噪声引起的带外相位噪声 减少6dB。图3.1中还有一个同步电路,目的是使分频器的输出与高频的VCO信号 同步,减少异步电路引起的累积抖动25]。 多模分频器的工作原理与2.1.2节的介绍相同,只是当mod=”1”时进行的是 M+0.5分频,因此分频器的分频比是: N-(M+0.5)-S-Tw+M-(P-S)-T (4.1) =M.P+0.5S 由(4.1)式可见,如果S以1为步长变化,则分频器的步长为0.5,与传统实现 相比量化阶梯降低了一半,从而使频率综合器的带外相位噪声性能提高6dB。 3.2P和S的实现方式 3.2.1可编程分频器的分频范围 根据Pulse-Swallow型多模可编程分频器的工作原理,P>S,对于给定的P值, Smax=P.1,下面推导P的最小可能值Pmin,此时S的取值范围是0~Pmin-1。 人

频率综合器中分频器的研究与设计 第三章 可编程分频器设计 3.1 可编程分频器结构 图 3-1是本论文所采用的小数分频器的结构框图。 图 3-1 可编程分频器结构 它由Pulse-swallow架构的多模可编程分频器和SDM构成。SDM产生动态分频 比,从而产生P和S的值,分别作为P计数器和S计数器的模数。与2.1.2节的介绍不 同的是,多模可编程分频器采用了M/M+0.5 双模预分频器。这使得可编程分频器的 分频步长从 1 降为 0.5,从而降低了分频器输出和参考时钟边沿“动态对齐”引起的 量化噪声,根据文献[7][8][9]等的分析,可以使SDM量化噪声引起的带外相位噪声 减少 6dB。图3.1中还有一个同步电路,目的是使分频器的输出与高频的VCO信号 同步,减少异步电路引起的累积抖动[25]。 多模分频器的工作原理与2.1.2节的介绍相同,只是当mod=”1”时进行的是 M+0.5 分频,因此分频器的分频比是: ( ) () vco vco vco M 0.5 M M 0.5 ST P S T N T P S + ⋅⋅ +⋅ − ⋅ = =⋅+ (4.1) 由(4.1)式可见,如果S以 1 为步长变化,则分频器的步长为 0.5,与传统实现 相比量化阶梯降低了一半,从而使频率综合器的带外相位噪声性能提高 6 dB。 3.2 P 和 S 的实现方式 3.2.1 可编程分频器的分频范围 根据Pulse-Swallow型多模可编程分频器的工作原理,P>S,对于给定的P值, Smax=P-1,下面推导P的最小可能值Pmin,此时S的取值范围是 0~Pmin-1。 14