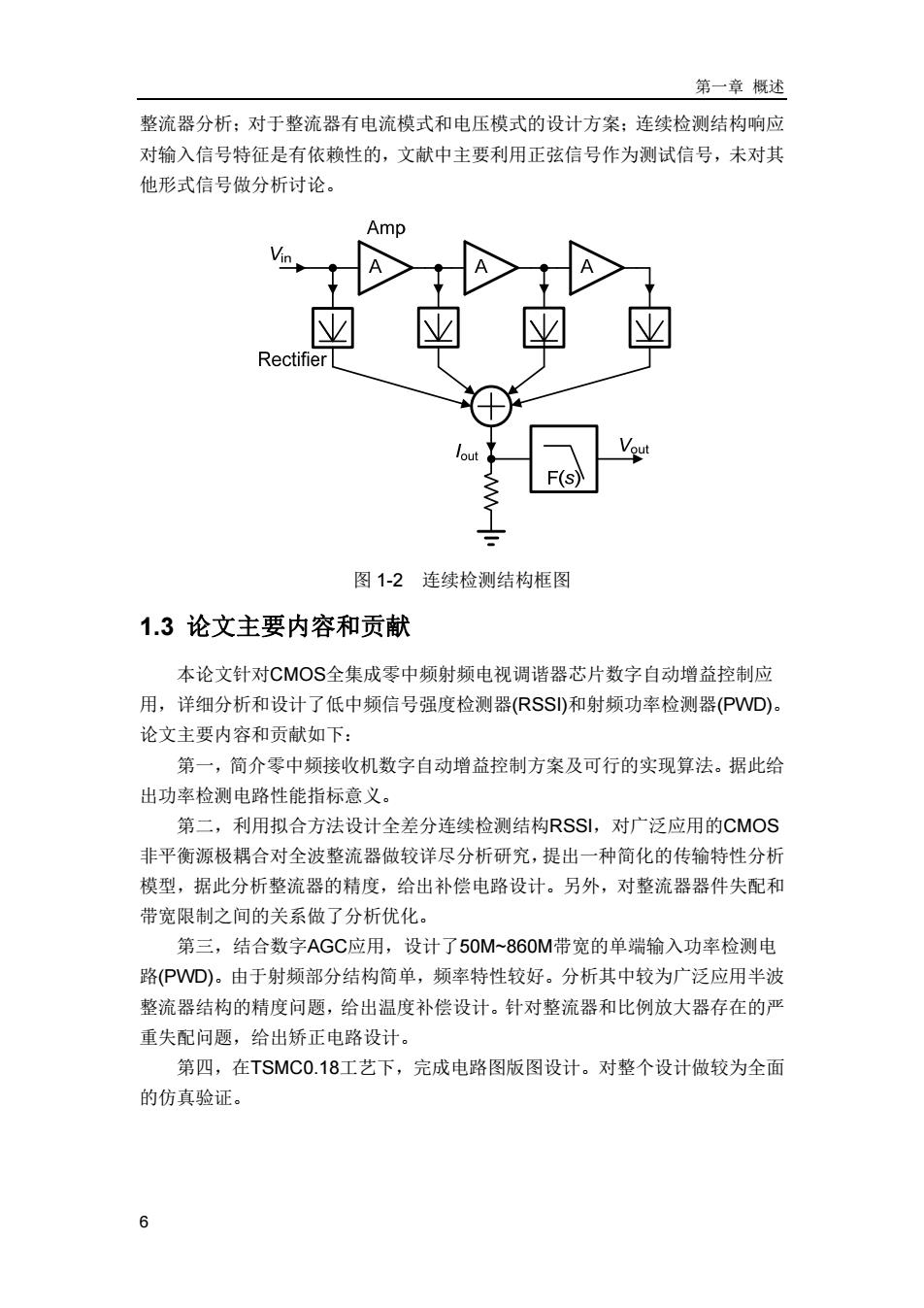

第一章概述 整流器分析;对于整流器有电流模式和电压模式的设计方案:连续检测结构响应 对输入信号特征是有依赖性的,文献中主要利用正弦信号作为测试信号,未对其 他形式信号做分析讨论。 Amp Rectifier Vout F(s) 图1-2连续检测结构框图 1.3论文主要内容和贡献 本论文针对CMOS全集成零中频射频电视调谐器芯片数字自动增益控制应 用,详细分析和设计了低中频信号强度检测器(RSS)和射频功率检测器(PWD)。 论文主要内容和贡献如下: 第一,简介零中频接收机数字自动增益控制方案及可行的实现算法。据此给 出功率检测电路性能指标意义。 第二,利用拟合方法设计全差分连续检测结构RSS,对广泛应用的CMOS 非平衡源极耦合对全波整流器做较详尽分析研究,提出一种简化的传输特性分析 模型,据此分析整流器的精度,给出补偿电路设计。另外,对整流器器件失配和 带宽限制之间的关系做了分析优化。 第三,结合数字AGC应用,设计了50M~860M带宽的单端输入功率检测电 路(PWD)。由于射频部分结构简单,频率特性较好。分析其中较为广泛应用半波 整流器结构的精度问题,给出温度补偿设计。针对整流器和比例放大器存在的严 重失配问题,给出矫正电路设计。 第四,在TSMC0.18工艺下,完成电路图版图设计。对整个设计做较为全面 的仿真验证。 6

第一章 概述 6 整流器分析;对于整流器有电流模式和电压模式的设计方案;连续检测结构响应 对输入信号特征是有依赖性的,文献中主要利用正弦信号作为测试信号,未对其 他形式信号做分析讨论。 图 1-2 连续检测结构框图 1.3 论文主要内容和贡献 本论文针对CMOS全集成零中频射频电视调谐器芯片数字自动增益控制应 用,详细分析和设计了低中频信号强度检测器(RSSI)和射频功率检测器(PWD)。 论文主要内容和贡献如下: 第一,简介零中频接收机数字自动增益控制方案及可行的实现算法。据此给 出功率检测电路性能指标意义。 第二,利用拟合方法设计全差分连续检测结构RSSI,对广泛应用的CMOS 非平衡源极耦合对全波整流器做较详尽分析研究,提出一种简化的传输特性分析 模型,据此分析整流器的精度,给出补偿电路设计。另外,对整流器器件失配和 带宽限制之间的关系做了分析优化。 第三,结合数字AGC应用,设计了50M~860M带宽的单端输入功率检测电 路(PWD)。由于射频部分结构简单,频率特性较好。分析其中较为广泛应用半波 整流器结构的精度问题,给出温度补偿设计。针对整流器和比例放大器存在的严 重失配问题,给出矫正电路设计。 第四,在TSMC0.18工艺下,完成电路图版图设计。对整个设计做较为全面 的仿真验证

第一章概述 1.4论文组织结构 本论文根据CMOS全集成直接变频结构数字电视调谐器数字功率型自动增 益控制需求,设计了不同应用条件和性能要求的功率检测电路,并简要介绍了 AGC的相关内容。本论文具体结构如下: 第二章简介零中频接收机增益控制的一种方案及其意义,同时介绍可行的数 字算法实现。由此引入功率检测电路的性能参数和设计指标。 第三章介绍低中频RSS电路设计。设计采用了连续检测结构,给出系统设 计方法。较为详细分析了电路各个单元对检测精度影响。针对工艺、温度、器件 失配问题做了补偿优化。最后讨论了电路对信号特性的依赖性。 第四章介绍射频PWD电路设计。充分利用数字自动增益控制应用条件,采 用数字控制预放大器加整流器结构,实现了射频宽带功率检测电路设计。文中同 样分析了电路各单元对检测精度的影响。文中对直流失调问题采用6 bit DAC做 预矫正。在spectre仿真环境下,实现直流失调预矫正后性能仿真。 第五章对本文的分析设计做总结,给出存在的问题,对将来的工作做展望。 1

第一章 概述 7 1.4 论文组织结构 本论文根据 CMOS 全集成直接变频结构数字电视调谐器数字功率型自动增 益控制需求,设计了不同应用条件和性能要求的功率检测电路,并简要介绍了 AGC 的相关内容。本论文具体结构如下: 第二章简介零中频接收机增益控制的一种方案及其意义,同时介绍可行的数 字算法实现。由此引入功率检测电路的性能参数和设计指标。 第三章介绍低中频 RSSI 电路设计。设计采用了连续检测结构,给出系统设 计方法。较为详细分析了电路各个单元对检测精度影响。针对工艺、温度、器件 失配问题做了补偿优化。最后讨论了电路对信号特性的依赖性。 第四章介绍射频 PWD 电路设计。充分利用数字自动增益控制应用条件,采 用数字控制预放大器加整流器结构,实现了射频宽带功率检测电路设计。文中同 样分析了电路各单元对检测精度的影响。文中对直流失调问题采用 6bit DAC 做 预矫正。在 spectre 仿真环境下,实现直流失调预矫正后性能仿真。 第五章对本文的分析设计做总结,给出存在的问题,对将来的工作做展望

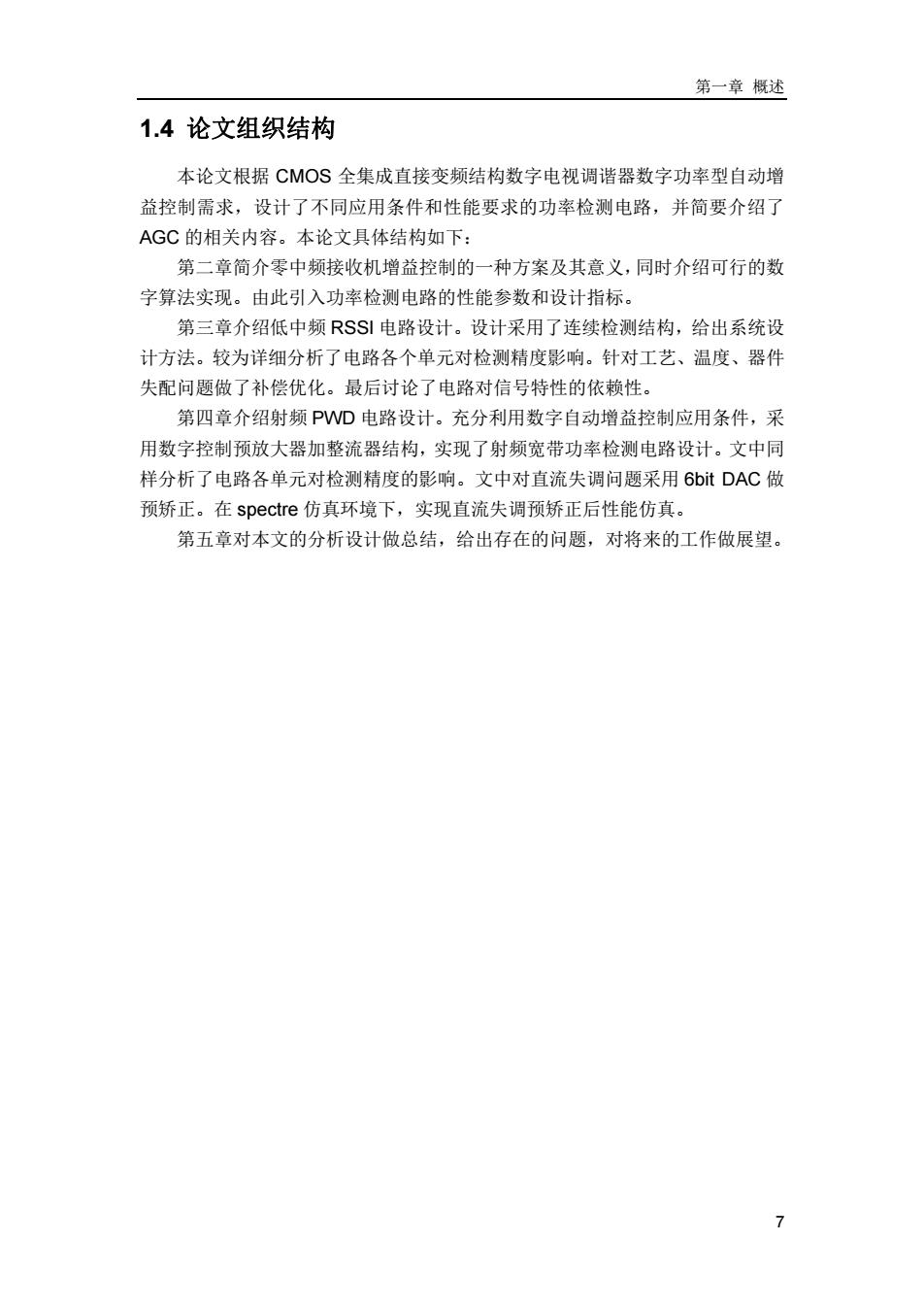

第二章数字自动增益控制简介 第二章 数字自动增益控制简介 2.1零中频接收机自动增益控制 接受机的设计往往要在噪声非线性-功耗之间做折中。同时考虑噪声,非线 性引入的杂散分量,可以引入信号噪声失真比(SNDR),用做描述接受机中信号 质量的指标7]。这样,使接收机每一模块输出趋向最大的SNDR可以成为自动 增益控制的目标。以零中频接受机为例,也是本文设计的应用构架,来简介这一 自动增益控制方案。为简化, 图2-1为零中频接受机单一支路框图(通常为/Q两路),同时包含了功率检 测电路。 AALPF VGLNA S-D Gm MIxer PGA PD] RSSI RSSI 图21连续检测结构框图 2.1.1自动增益控制基本问题 最大化SNDR为目标设计自动增益控制接收机系统时需考虑如下基本问题: 带内、带外干扰强弱,接管点如何设定,可变增益模块设计时线性度和噪声系数 如何随增益变化。 a)带内、带外千扰 非线性对信号引入的干扰主要考虑带内及带外干扰[1]。带内干扰指的是接受 频道内各子带间交调产生的杂散分量:带外干扰指接受频道外不同频道间交调产 生的杂散分量,也即为邻道干扰。带内干扰主要考虑复合三阶差拍(CTBs)失真 [7],带外干扰主要考虑三阶交调量(M3)[8],图2-2显示了两种干扰的产生。 自动增益控制设计时要适宜地考虑两种杂散分量的强弱。对于射频前端 (LNA,Mixe)整个信道内的信号均作为输入,此时有可能带内干扰占主导,也有 可能带外干扰占主导,为理论计算杂散强度,应该根据信号特征和应用环境作出 评判。如果不考虑实际应用条件,相同输入功率下,在最坏情形下,CTBs功率 要大于M3功率。 对于 图2-1所示零中频结构,信号混频输出后,由于混频器3dB带宽为10M左 9

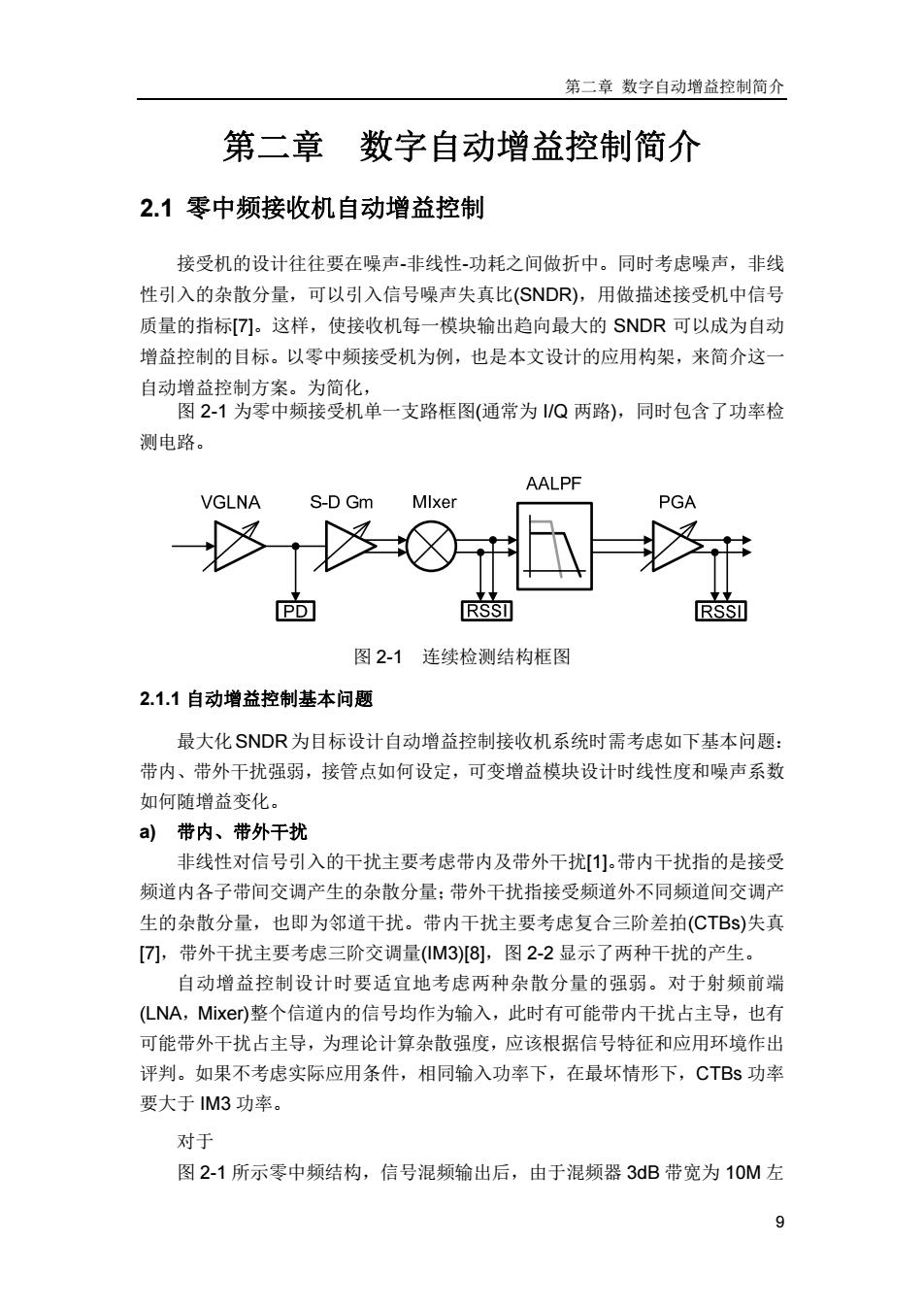

第二章 数字自动增益控制简介 9 第二章 数字自动增益控制简介 2.1 零中频接收机自动增益控制 接受机的设计往往要在噪声-非线性-功耗之间做折中。同时考虑噪声,非线 性引入的杂散分量,可以引入信号噪声失真比(SNDR),用做描述接受机中信号 质量的指标[7]。这样,使接收机每一模块输出趋向最大的 SNDR 可以成为自动 增益控制的目标。以零中频接受机为例,也是本文设计的应用构架,来简介这一 自动增益控制方案。为简化, 图 2-1 为零中频接受机单一支路框图(通常为 I/Q 两路),同时包含了功率检 测电路。 图 2-1 连续检测结构框图 2.1.1 自动增益控制基本问题 最大化SNDR为目标设计自动增益控制接收机系统时需考虑如下基本问题: 带内、带外干扰强弱,接管点如何设定,可变增益模块设计时线性度和噪声系数 如何随增益变化。 a) 带内、带外干扰 非线性对信号引入的干扰主要考虑带内及带外干扰[1]。带内干扰指的是接受 频道内各子带间交调产生的杂散分量;带外干扰指接受频道外不同频道间交调产 生的杂散分量,也即为邻道干扰。带内干扰主要考虑复合三阶差拍(CTBs)失真 [7],带外干扰主要考虑三阶交调量(IM3)[8],图 2-2 显示了两种干扰的产生。 自动增益控制设计时要适宜地考虑两种杂散分量的强弱。对于射频前端 (LNA,Mixer)整个信道内的信号均作为输入,此时有可能带内干扰占主导,也有 可能带外干扰占主导,为理论计算杂散强度,应该根据信号特征和应用环境作出 评判。如果不考虑实际应用条件,相同输入功率下,在最坏情形下,CTBs 功率 要大于 IM3 功率。 对于 图 2-1 所示零中频结构,信号混频输出后,由于混频器 3dB 带宽为 10M 左

第二章数字自动增益控制简介 右,带外干扰被抑制,此时混频器之后的模拟部分的杂散分量可以认为只存在带 内干扰。功率检测电路带宽以及增益控制的一些理论计算设计考虑也就依据干扰 的特点给出。在 图2-1中,要求PWD可以检测输入信号总带宽内的信号,要求RSSI可以 检测单一频道内功率即可。 Pin IM3 CTBs NN+2 N+4 f Out band interference In band interference 图2-2干扰的两种主要情况 b)接管点(take-over point) 对于接收机中可变增益模块如/GLNA,自动增益控制工作的基本结果是使 得其输出维持在一个恒定的功率值。也就是说当输入功率较小时,增益提高,输 入功率较大时,减小增益,甚至衰减。在这一过程中增益开始减小的输入功率值 称为接管点(P),此时输出恒定的功率值为目标功率。 对于给定的模块,如果输入噪声不变,则存在最优输入功率使得其输出 SWDR最大[7]。以带外干扰为例,如果输入干扰强度很大,考虑最坏情形,在 DVB-T协议中,带外干扰强度高于带内信号45dB,最小输入信号功率-90dBm. 此时可以认为总输入功率P与干扰信号功率相等,不影响M3计算。另外当信号 足够大时,带内信号变化率与输入信号变化率一致[1]。用公式表示为: P2 Pn-48(Pn≥-42dBm) (2.1) -90 (P <-42dBm) 图2-3显示输出信号中带内信号Psg、M3、噪声随输入信号增大的变化情况。 设M3与噪底相等的输入功率为Pop。当输入功率小于Po时,干扰以噪声为主, 噪声保持不变:当输入功率超过Pop时干扰以IM3为主,M3以三次方形式增长。 图中表明当输入功率为Pop时,可以获得最大的SNDR。对于带内干扰很强时也 作类似的分析。 根据上述分析,自动增益模块设定其目标功率为后级模块最优输入功率,可 以使得后级模块得到最大SNDR。这时可变增益模块的输入为最优接管点。根据 这一原则,可以得出接收机链路中关键节点处的接管点。 10

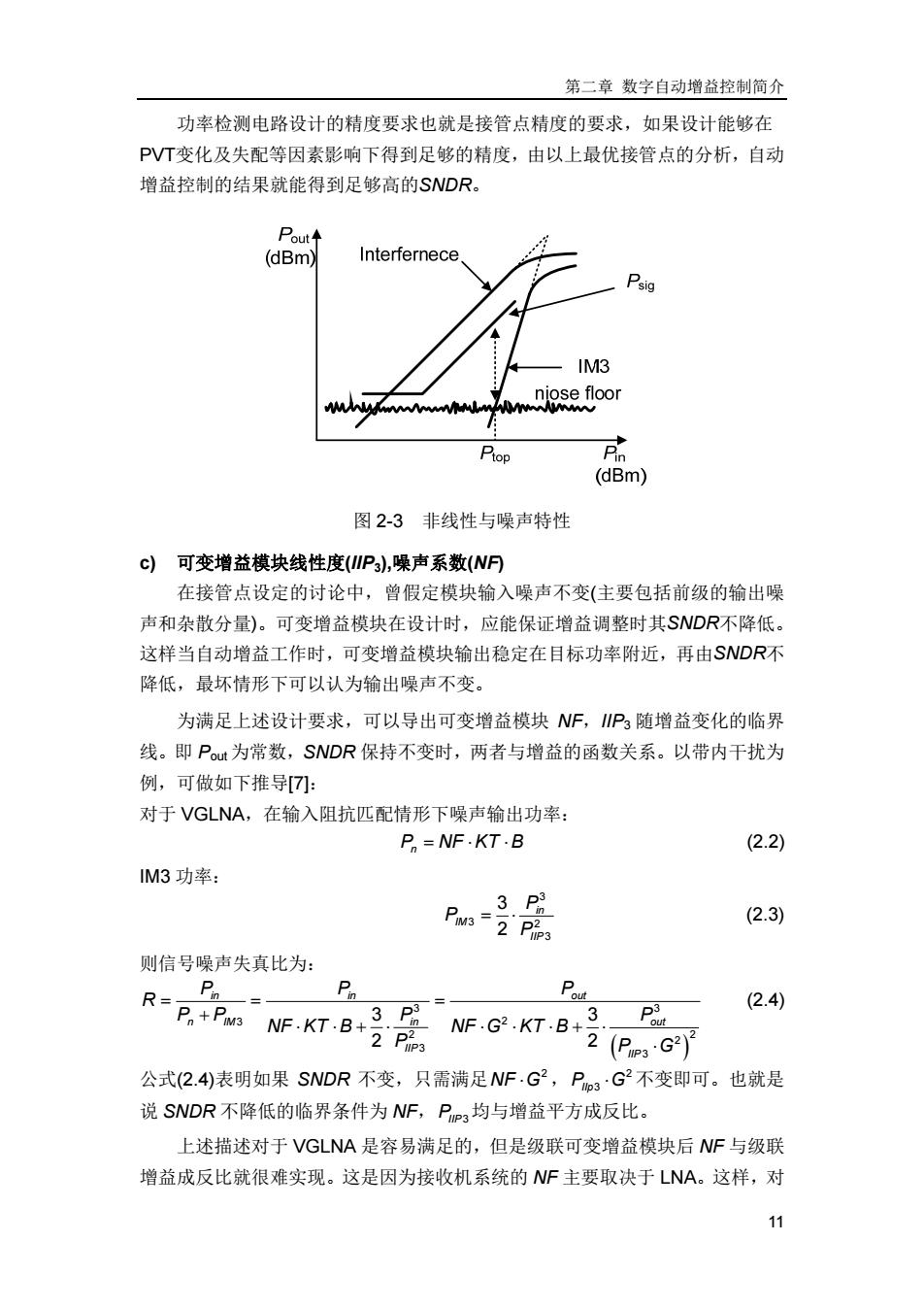

第二章 数字自动增益控制简介 10 右,带外干扰被抑制,此时混频器之后的模拟部分的杂散分量可以认为只存在带 内干扰。功率检测电路带宽以及增益控制的一些理论计算设计考虑也就依据干扰 的特点给出。在 图 2-1 中,要求 PWD 可以检测输入信号总带宽内的信号,要求 RSSI 可以 检测单一频道内功率即可。 图 2-2 干扰的两种主要情况 b) 接管点(take-over point) 对于接收机中可变增益模块如VGLNA,自动增益控制工作的基本结果是使 得其输出维持在一个恒定的功率值。也就是说当输入功率较小时,增益提高,输 入功率较大时,减小增益,甚至衰减。在这一过程中增益开始减小的输入功率值 称为接管点(Ptop),此时输出恒定的功率值为目标功率。 对于给定的模块,如果输入噪声不变,则存在最优输入功率使得其输出 SNDR最大[7]。以带外干扰为例,如果输入干扰强度很大,考虑最坏情形,在 DVB-T协议中,带外干扰强度高于带内信号45dB,最小输入信号功率–90dBm。 此时可以认为总输入功率Pin与干扰信号功率相等,不影响IM3计算。另外当信号 足够大时,带内信号变化率与输入信号变化率一致[1]。用公式表示为: < 48 -42dBm 90 -42dBm in in sig in P P P P (2.1) 图2-3显示输出信号中带内信号Psig、IM3、噪声随输入信号增大的变化情况。 设IM3与噪底相等的输入功率为Ptop。当输入功率小于Ptop时,干扰以噪声为主, 噪声保持不变;当输入功率超过Ptop时干扰以IM3为主,IM3以三次方形式增长。 图中表明当输入功率为Ptop时,可以获得最大的SNDR。对于带内干扰很强时也 作类似的分析。 根据上述分析,自动增益模块设定其目标功率为后级模块最优输入功率,可 以使得后级模块得到最大SNDR。这时可变增益模块的输入为最优接管点。根据 这一原则,可以得出接收机链路中关键节点处的接管点

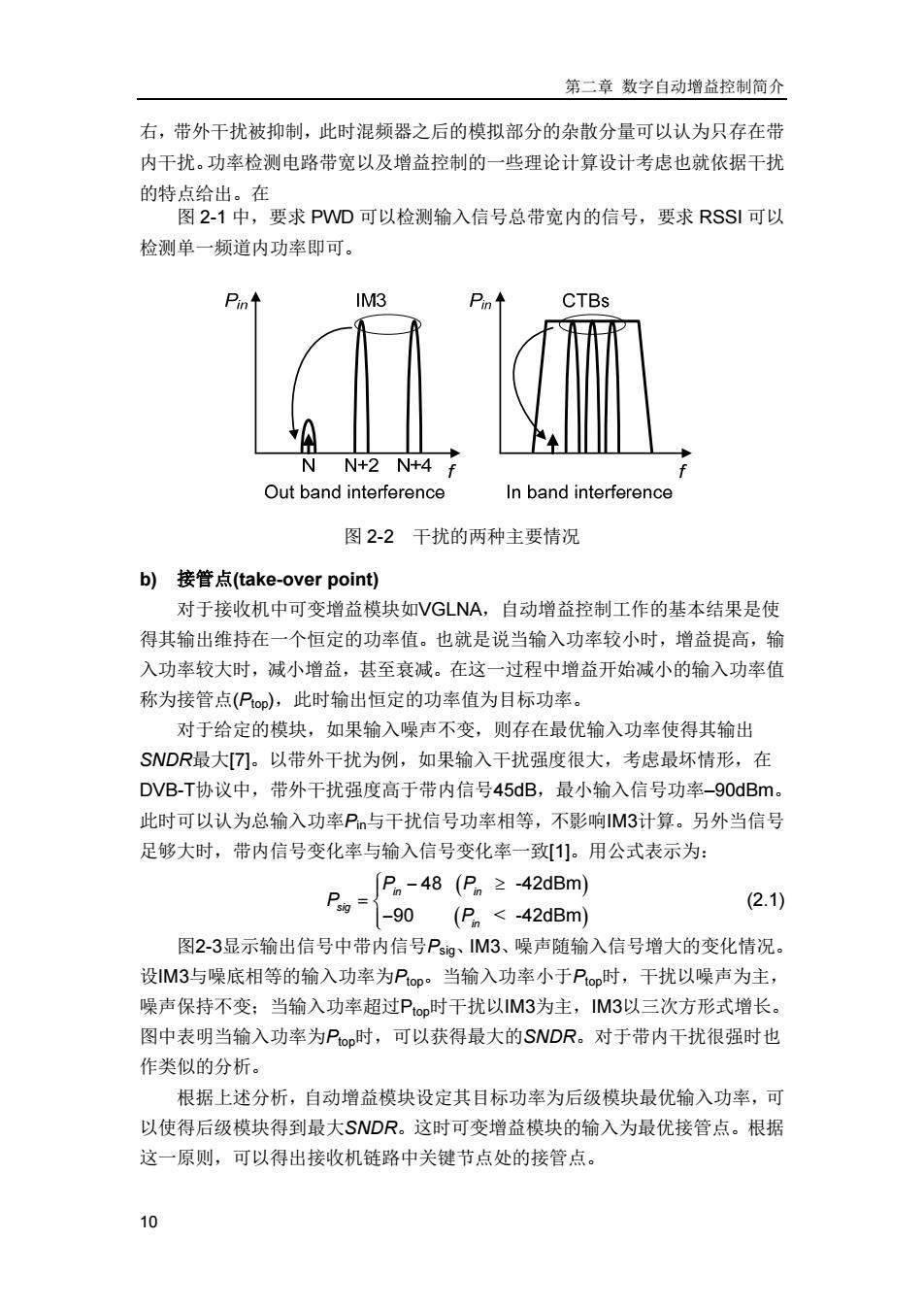

第二章数字自动增益控制简介 功率检测电路设计的精度要求也就是接管点精度的要求,如果设计能够在 PVT变化及失配等因素影响下得到足够的精度,由以上最优接管点的分析,自动 增益控制的结果就能得到足够高的SNDR。 Poutt (dBm) Interfernece. Psig IM3 niose floor Ptop (dBm) 图2-3非线性与噪声特性 c)可变增益模块线性度(P3),噪声系数(W 在接管点设定的讨论中,曾假定模块输入噪声不变(主要包括前级的输出噪 声和杂散分量)。可变增益模块在设计时,应能保证增益调整时其SWDR不降低。 这样当自动增益工作时,可变增益模块输出稳定在目标功率附近,再由SNDR不 降低,最坏情形下可以认为输出噪声不变。 为满足上述设计要求,可以导出可变增益模块NF,P3随增益变化的临界 线。即Pout为常数,SNDR保持不变时,两者与增益的函数关系。以带内干扰为 例,可做如下推导7]: 对于VGLNA,在输入阻抗匹配情形下噪声输出功率: P =NF.KT.B (2.2) IM3功率: 3.P PiMS= (2.3) 2P品闷 则信号噪声失真比为: R-- Pn Pout +PiM3 (2.4) NF-KT.B+3.P NF.G2.KT.B+ 2 Pie3 (PG27 2 公式(2.4)表明如果SNDR不变,只需满足NF.G2,P3G2不变即可。也就是 说SWDR不降低的临界条件为NF,P3均与增益平方成反比。 上述描述对于VGLNA是容易满足的,但是级联可变增益模块后NF与级联 增益成反比就很难实现。这是因为接收机系统的NF主要取决于LNA。这样,对 11

第二章 数字自动增益控制简介 11 功率检测电路设计的精度要求也就是接管点精度的要求,如果设计能够在 PVT变化及失配等因素影响下得到足够的精度,由以上最优接管点的分析,自动 增益控制的结果就能得到足够高的SNDR。 图 2-3 非线性与噪声特性 c) 可变增益模块线性度(IIP3),噪声系数(NF) 在接管点设定的讨论中,曾假定模块输入噪声不变(主要包括前级的输出噪 声和杂散分量)。可变增益模块在设计时,应能保证增益调整时其SNDR不降低。 这样当自动增益工作时,可变增益模块输出稳定在目标功率附近,再由SNDR不 降低,最坏情形下可以认为输出噪声不变。 为满足上述设计要求,可以导出可变增益模块 NF,IIP3 随增益变化的临界 线。即 Pout 为常数,SNDR 保持不变时,两者与增益的函数关系。以带内干扰为 例,可做如下推导[7]: 对于 VGLNA,在输入阻抗匹配情形下噪声输出功率: P NF KT B n (2.2) IM3 功率: 3 3 2 3 3 2 in IM IIP P P P (2.3) 则信号噪声失真比为: 3 3 3 2 2 2 2 3 3 3 3 2 2 in in out n IM in out IIP IIP P P P R P P P P NF KT B NF G KT B P P G (2.4) 公式(2.4)表明如果 SNDR 不变,只需满足 2 NF G , 2 P G IIp3 不变即可。也就是 说 SNDR 不降低的临界条件为 NF,PIIP3均与增益平方成反比。 上述描述对于 VGLNA 是容易满足的,但是级联可变增益模块后 NF 与级联 增益成反比就很难实现。这是因为接收机系统的 NF 主要取决于 LNA。这样,对