第一章概述 第一章概述 1.1研究动机 数字视频广播(Digital Video Broadcasting)对射频接收机信噪比有着较高的 要求。作为射频接收机中重要的一个模块,频率综合器为射频接收机提供本振, 因而频率综合器要具有低相位噪声的特点。除此之外,频率综合器中滤波器通常 占用芯片较大的面积,能够片上集成滤波器也是全集成接收机的关键技术之一。 频率综合器按结构可以分为整数分频和分数分频。在整数分频频率综合器 中,输出频率只能为参考时钟的整数倍。参考时钟的选取受到输出分辨率的限制, 如果分辨率较小,则参考时钟频率也会比较小。从环路稳定性的角度来考虑,一 般环路带宽小于参考时钟的十分之一。较小的环路带宽一方面不能抑制带外压控 振荡器的相位噪声,另一方面环路的建立时间也会受到影响。分数分频的频率综 合器很好的解决了上述问题。 在分数分频结构中[1)],△Σ(Delta Sigma Modulator.,简称DSM)调制器输出 的量化序列动态的调整着环路的分频比,因而可以实现分数分频。这样,输出频 率精度就为分频比的小数部分和参考时钟频率的乘积。小数部分越小,频率综合 器输出频率精度就越高。这样,频率综合器输出精度不再受限于参考时钟的大小。 换句话说,当参考时钟很大时,依然可以得到很小的输出分辨率。此时,在较大 的参考时钟下,就可以选取较大的环路带宽来加快锁相环环路的小信号建立速 度,同时更好的抑制来自于压控振荡器的相位噪声。 分数分频同样存在着一些问题。调制器输出的随机序列不可避免的引入了量 化噪声2]。这种噪声经过调制器噪声整形后,低频的噪声被量化到高频。如果频 率综合器环路对高频噪声抑制不够充分,则此部分量化噪声将会恶化频率综合器 高频相位噪声。为了充分抑制这一部分噪声,需要采用噪声消除技术或高阶的环 路滤波器3]。因此通过环路参数设计来优化频率综合器性能具有重要意义。另一 方面,量化噪声通过环路非线性(鉴频鉴相器和电荷泵)折叠到带内,严重恶化频 率综合器带内相位噪声性能。因此设计高线性度的电荷泵也是分数分频模式下获 得良好带内相位噪声的关键[4]。 其次,和单端调谐相比,全差分调谐的频率综合器具有更好的电源抑制比[5], 1

第一章 概述 1 第一章 概述 1.1 研究动机 数字视频广播(Digital Video Broadcasting)对射频接收机信噪比有着较高的 要求。作为射频接收机中重要的一个模块,频率综合器为射频接收机提供本振, 因而频率综合器要具有低相位噪声的特点。除此之外,频率综合器中滤波器通常 占用芯片较大的面积,能够片上集成滤波器也是全集成接收机的关键技术之一。 频率综合器按结构可以分为整数分频和分数分频。在整数分频频率综合器 中,输出频率只能为参考时钟的整数倍。参考时钟的选取受到输出分辨率的限制, 如果分辨率较小,则参考时钟频率也会比较小。从环路稳定性的角度来考虑,一 般环路带宽小于参考时钟的十分之一。较小的环路带宽一方面不能抑制带外压控 振荡器的相位噪声,另一方面环路的建立时间也会受到影响。分数分频的频率综 合器很好的解决了上述问题。 在分数分频结构中[1],∆Σ(Delta Sigma Modulator,简称 DSM)调制器输出 的量化序列动态的调整着环路的分频比,因而可以实现分数分频。这样,输出频 率精度就为分频比的小数部分和参考时钟频率的乘积。小数部分越小,频率综合 器输出频率精度就越高。这样,频率综合器输出精度不再受限于参考时钟的大小。 换句话说,当参考时钟很大时,依然可以得到很小的输出分辨率。此时,在较大 的参考时钟下,就可以选取较大的环路带宽来加快锁相环环路的小信号建立速 度,同时更好的抑制来自于压控振荡器的相位噪声。 分数分频同样存在着一些问题。调制器输出的随机序列不可避免的引入了量 化噪声[2]。这种噪声经过调制器噪声整形后,低频的噪声被量化到高频。如果频 率综合器环路对高频噪声抑制不够充分,则此部分量化噪声将会恶化频率综合器 高频相位噪声。为了充分抑制这一部分噪声,需要采用噪声消除技术或高阶的环 路滤波器[3]。因此通过环路参数设计来优化频率综合器性能具有重要意义。另一 方面,量化噪声通过环路非线性(鉴频鉴相器和电荷泵)折叠到带内,严重恶化频 率综合器带内相位噪声性能。因此设计高线性度的电荷泵也是分数分频模式下获 得良好带内相位噪声的关键[4]。 其次,和单端调谐相比,全差分调谐的频率综合器具有更好的电源抑制比[5]

2~2.4GHz分数分频频率综合器设计 但全差分的噪声模型一直以来并没有被详细分析。因此系统的分析差分调谐频率 综合器噪声特性对于相位噪声优化也具有重要的意义。 1.2论文研究内容及贡献 论文围绕频率综合器的分析和设计展开。首先针对频率综合器环路参数设计 和相位噪声优化展开了系统的分析,其次设计讨论了频率综合器关键模块的设计 细节和需要注意的问题。在此基础上,实现了一款分数分频频率综合器。论文的 主要贡献为: 详细比较了环路参数设计的两种方法,基于闭环的根轨迹法和基于开环的相 位裕度最大法。尽管两种分析方法出发点不一样,但却会得到完全相同的结论。 分析了差分调谐结构频率综合器的噪声模型,并和单端结构的噪声模型做出 比较,提出优化滤波器噪声的方法。 设计了基于MATLAB软件的图形设计界面,大大简化了频率综合器参数设 计过程。利用此图形界面可以方便的得到环路参数以及各种系统仿真结果: 设计了高线性度的差分电荷泵,消除了电荷泵常见的非理想因素。设计了同 步结构高速电流模预分频器,在不增加功耗的情况下减小了分频器设计难度。同 时,设计了全集成的压控振荡器,压控振荡器采用片上线性稳压器和尾电感电容 阵列优化相位噪声从而达到了低相位噪声性能。 1.3论文组织结构 本文论文阐述了频率综合器环路参数设计、噪声优化和关键电路模块设计, 然后在此基础上设计了一款应用在DVB-T数字电视调谐器中的分数分频频率综 合器。论文各部分内容如下: 第二章“环路参数与相位噪声分析”首先详细分析了环路参数的两种计算方 法,然后比较了差分调谐和单端调谐两种结构的噪声特性,并提出了减小差分结 构中滤波器噪声贡献的方法,然后简要分析了分数分频中调制器的一些问题。最 后利用MATLAB图形界面设计出了频率综合器环路参数。 第三章“电路设计”首先介绍了电荷泵中常见的非理想因素和抑制这些非理 想因素所采用的电路技术,并利用这些设计技术实现了高性能的全差分电荷泵。 其次,从小信号的角度定量的分析了预分频器的自激振荡频率,在此基础上设计 2

2~2.4 GHz 分数分频频率综合器设计 2 但全差分的噪声模型一直以来并没有被详细分析。因此系统的分析差分调谐频率 综合器噪声特性对于相位噪声优化也具有重要的意义。 1.2 论文研究内容及贡献 论文围绕频率综合器的分析和设计展开。首先针对频率综合器环路参数设计 和相位噪声优化展开了系统的分析,其次设计讨论了频率综合器关键模块的设计 细节和需要注意的问题。在此基础上,实现了一款分数分频频率综合器。论文的 主要贡献为: 详细比较了环路参数设计的两种方法,基于闭环的根轨迹法和基于开环的相 位裕度最大法。尽管两种分析方法出发点不一样,但却会得到完全相同的结论。 分析了差分调谐结构频率综合器的噪声模型,并和单端结构的噪声模型做出 比较,提出优化滤波器噪声的方法。 设计了基于 MATLAB 软件的图形设计界面,大大简化了频率综合器参数设 计过程。利用此图形界面可以方便的得到环路参数以及各种系统仿真结果。 设计了高线性度的差分电荷泵,消除了电荷泵常见的非理想因素。设计了同 步结构高速电流模预分频器,在不增加功耗的情况下减小了分频器设计难度。同 时,设计了全集成的压控振荡器,压控振荡器采用片上线性稳压器和尾电感电容 阵列优化相位噪声从而达到了低相位噪声性能。 1.3 论文组织结构 本文论文阐述了频率综合器环路参数设计、噪声优化和关键电路模块设计, 然后在此基础上设计了一款应用在 DVB-T 数字电视调谐器中的分数分频频率综 合器。论文各部分内容如下: 第二章“环路参数与相位噪声分析”首先详细分析了环路参数的两种计算方 法,然后比较了差分调谐和单端调谐两种结构的噪声特性,并提出了减小差分结 构中滤波器噪声贡献的方法,然后简要分析了分数分频中调制器的一些问题。最 后利用 MATLAB 图形界面设计出了频率综合器环路参数。 第三章“电路设计”首先介绍了电荷泵中常见的非理想因素和抑制这些非理 想因素所采用的电路技术,并利用这些设计技术实现了高性能的全差分电荷泵。 其次,从小信号的角度定量的分析了预分频器的自激振荡频率,在此基础上设计

第一章概述 了高速同步8/9预分频器电路。然后采用片上集成的线性稳压器给压控振荡器供 电,设计了多子带压控振荡器以降低其调谐增益。小的调谐增益不但减小了滤波 器面积,而且优化了环路的相位噪声性能。 第四章“芯片设计及测试”给出了芯片照片和测试结果。 第五章“总结与展望”对本文做出了总结,并对今后的工作做了简要的展望。 参考文献 [1]Tom A.D.Riley,Miles A.Copeland,TAD A.Kwasniewski,"Delta-Sigma Modulation in Fractional-N Frequency Synthesis,"IEEE J.Solid-State Circuits,vol.48,no.5,pp. 553-559,May1993. [2]Enrico Temporiti,Guido Albasini,Ivan Bietti,Rinaldo Castello,Matteo Colombo,"A 700-kHz Bandwidth Sigma-Delta Fractional Synthesizer With Spurs Compensation and Linearization Technique for WCDMA Applications,"IEEE J.Solid-State Circuits, vol.39,no.9,pp.1446-1454,Sep.2004. [3]Hamid R.Rategh,et al."A CMOS Frequency Synthesizer with an Injection-Locked Frequency Divider for a 5 GHz Wireless LAN Receiver,"IEEE J.of Solid-State Circuits,vol.35,no.5,pp.780-787,May 2000. [4]Bram De Muer,Michiel S.J.Steyaert,"On The Analysis of Sigma-Delta Fractional-N Frequency Synthesizers for High-Spectral Purity,"IEEE Transactions on Circuits and System,vol.50,no.11,pp.784-793,Nov.2003. [5]Brownlee,M.Hanumolu,P.K.Mayaram,K.;Un-Ku Moon,"A 0.5-GHz to 2.5-GHz PLL With Fully Differential Supply Regulated Tuning,"IEEE J.Solid-State Circuits vol.41,no.12,pp.2720-2728,Dec.2006. 3

第一章 概述 3 了高速同步 8/9 预分频器电路。然后采用片上集成的线性稳压器给压控振荡器供 电,设计了多子带压控振荡器以降低其调谐增益。小的调谐增益不但减小了滤波 器面积,而且优化了环路的相位噪声性能。 第四章“芯片设计及测试”给出了芯片照片和测试结果。 第五章“总结与展望”对本文做出了总结,并对今后的工作做了简要的展望。 参考文献 [1] Tom A. D. Riley, Miles A. Copeland, TAD A. Kwasniewski, “Delta-Sigma Modulation in Fractional-N Frequency Synthesis,” IEEE J. Solid-State Circuits, vol. 48, no. 5, pp. 553–559, May 1993. [2] Enrico Temporiti, Guido Albasini, Ivan Bietti, Rinaldo Castello, Matteo Colombo, ”A 700-kHz Bandwidth Sigma-Delta Fractional Synthesizer With Spurs Compensation and Linearization Technique for WCDMA Applications,” IEEE J. Solid-State Circuits, vol. 39, no. 9, pp. 1446–1454, Sep. 2004. [3] Hamid R. Rategh, et al. “A CMOS Frequency Synthesizer with an Injection-Locked Frequency Divider for a 5 GHz Wireless LAN Receiver,” IEEE J. of Solid-State Circuits, vol. 35, no. 5, pp. 780–787, May 2000. [4] Bram De Muer, Michiel S. J. Steyaert, “On The Analysis of Sigma-Delta Fractional-N Frequency Synthesizers for High-Spectral Purity,” IEEE Transactions on Circuits and System, vol. 50, no. 11, pp. 784–793, Nov. 2003. [5] Brownlee, M. ; Hanumolu, P.K. ; Mayaram, K. ; Un-Ku Moon,"A 0.5-GHz to 2.5-GHz PLL With Fully Differential Supply Regulated Tuning," IEEE J. Solid-State Circuits, vol. 41, no. 12, pp. 2720–2728, Dec. 2006

第二章环路参数与相位噪声分析 第二章 环路参数与相位噪声分析 2.1环路参数设计 锁相环(PLL)环路参数包括参考晶振时钟频率,电荷泵电流大小,滤波器电 容和电阻参数,压控振荡器调谐增益以及分频比。其中分频比由输出频率范围和 参考时钟频率共同决定。这些参数的选取在一定程度上直接决定了锁相环的性 能,也是电路设计之前首先考虑的问题。 环路参数设计可以用根轨迹法和相位裕度最大法1][2]。根轨迹形象的揭示 了开环增益,开环零极点和闭环零极点的之间的相互关系。开环增益取几何平均 值以取得最佳的环路稳定性,使得环路能够在工艺,电压和温度变化范围内依然 正常工作。相位裕度最大法以开环增益波特图出发,选取使当的环路参数使得开 环传输函数的相位裕度曲线在开环增益为1时达到最大。根轨迹方法比较直观, 但数学运算比较复杂,相位裕度最大法直接由相位裕度确定环路参数之间的关 系,因而计算起来比较简单。 2.1.1环路开环传输函数 PFD+CP LPF VCO cp Hpf(S) co no Divider 1 图2-1锁相环频率综合器系统框图 基于电荷泵的锁相环本质上是时变系统,精确的分析必须考虑电路的时变特 性。但这样分析起来相当复杂,而且不容易直观上把握。在大部分情况下,环路 带宽与参考时钟频率相比都很小,这样在参考时钟的每个周期内,环路内部状态 变化都非常小,研究每个参考时钟周期内环路的变化并没有太大意义。然而,我 们更多的是关心多个参考时钟周期内环路所表现的平均特性。这样的研究方法就 5

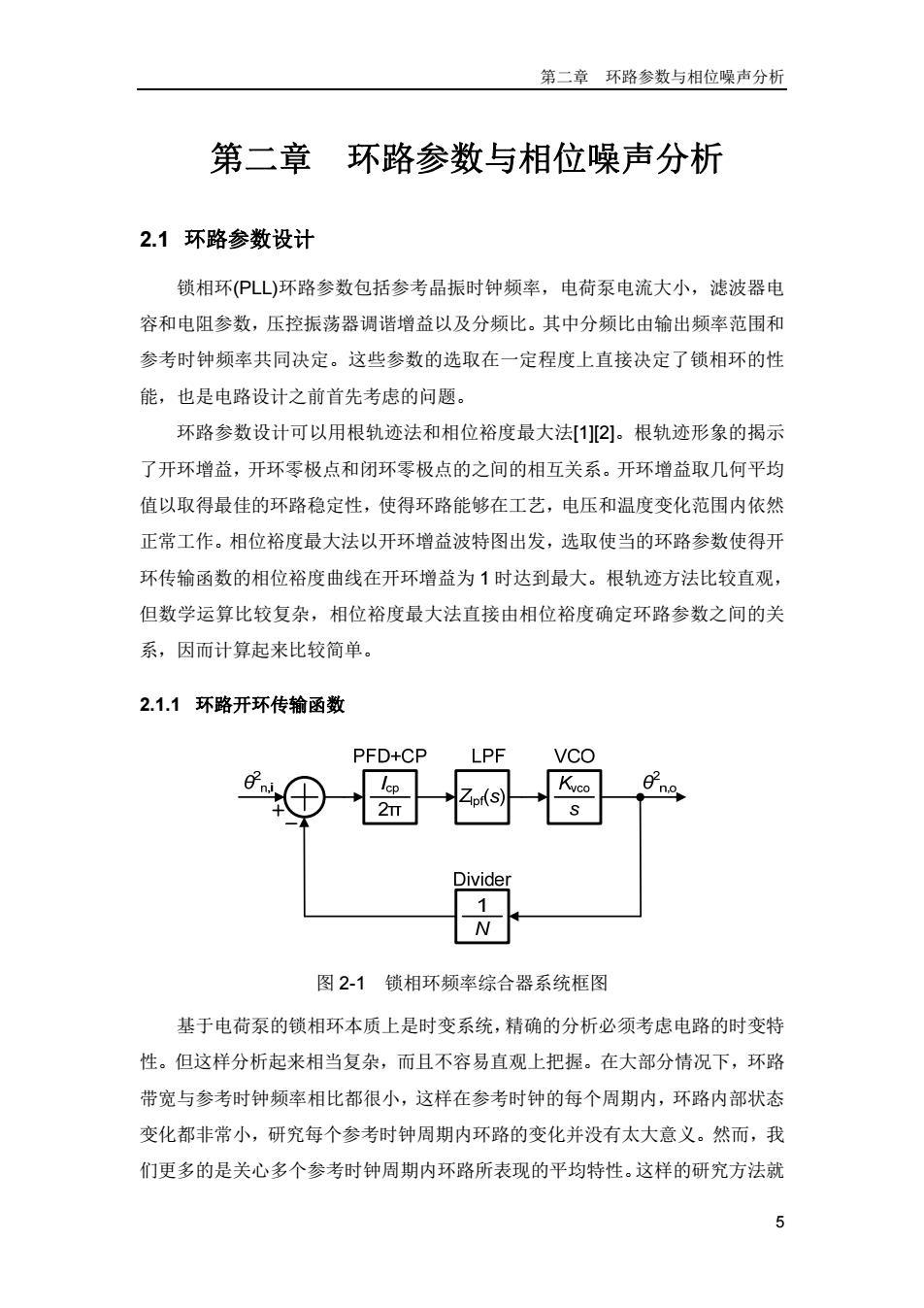

第二章 环路参数与相位噪声分析 5 第二章 环路参数与相位噪声分析 2.1 环路参数设计 锁相环(PLL)环路参数包括参考晶振时钟频率,电荷泵电流大小,滤波器电 容和电阻参数,压控振荡器调谐增益以及分频比。其中分频比由输出频率范围和 参考时钟频率共同决定。这些参数的选取在一定程度上直接决定了锁相环的性 能,也是电路设计之前首先考虑的问题。 环路参数设计可以用根轨迹法和相位裕度最大法[1][2]。根轨迹形象的揭示 了开环增益,开环零极点和闭环零极点的之间的相互关系。开环增益取几何平均 值以取得最佳的环路稳定性,使得环路能够在工艺,电压和温度变化范围内依然 正常工作。相位裕度最大法以开环增益波特图出发,选取使当的环路参数使得开 环传输函数的相位裕度曲线在开环增益为 1 时达到最大。根轨迹方法比较直观, 但数学运算比较复杂,相位裕度最大法直接由相位裕度确定环路参数之间的关 系,因而计算起来比较简单。 2.1.1 环路开环传输函数 图 2-1 锁相环频率综合器系统框图 基于电荷泵的锁相环本质上是时变系统,精确的分析必须考虑电路的时变特 性。但这样分析起来相当复杂,而且不容易直观上把握。在大部分情况下,环路 带宽与参考时钟频率相比都很小,这样在参考时钟的每个周期内,环路内部状态 变化都非常小,研究每个参考时钟周期内环路的变化并没有太大意义。然而,我 们更多的是关心多个参考时钟周期内环路所表现的平均特性。这样的研究方法就

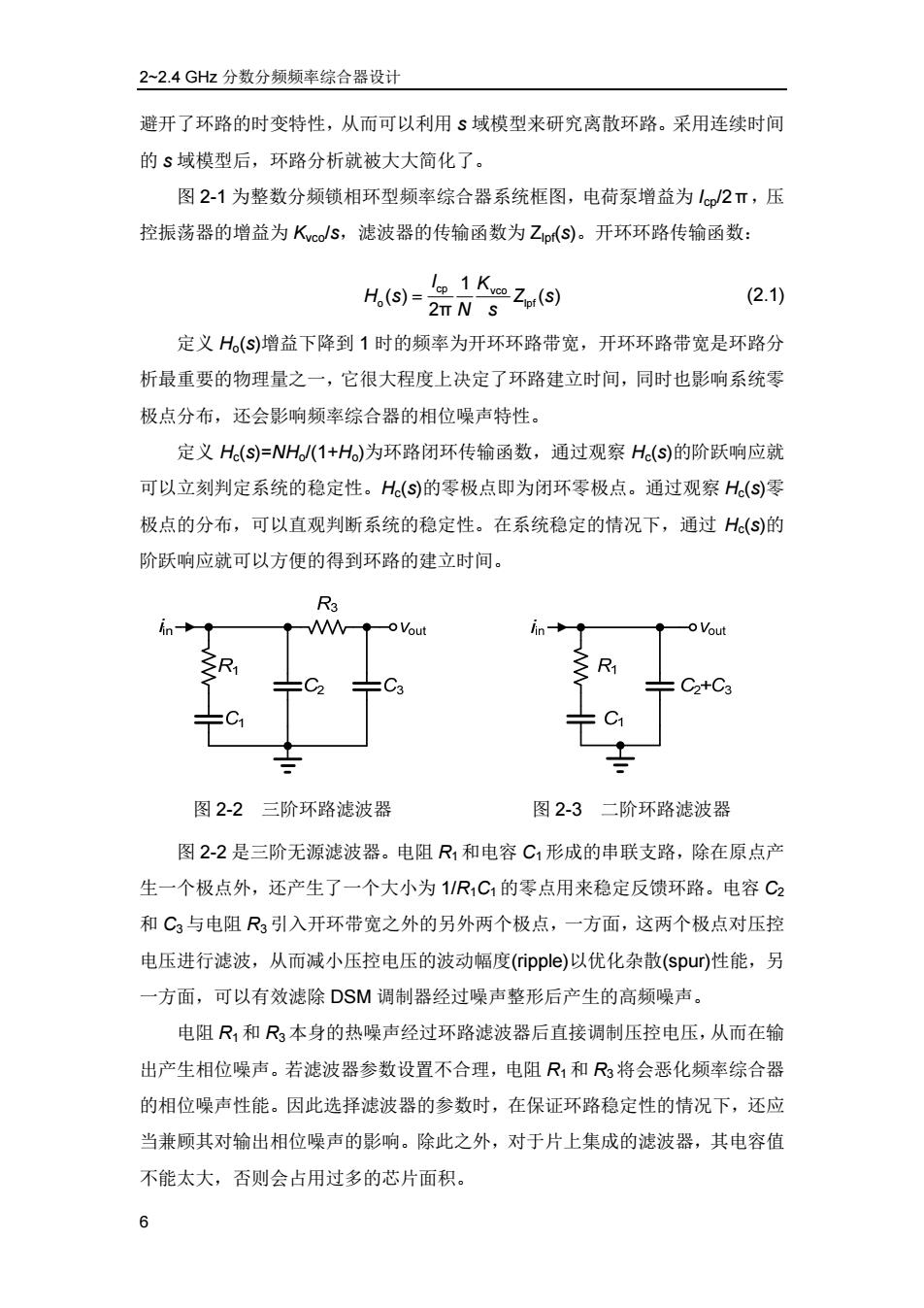

2~2.4GHz分数分频频率综合器设计 避开了环路的时变特性,从而可以利用S域模型来研究离散环路。采用连续时间 的S域模型后,环路分析就被大大简化了。 图2-1为整数分频锁相环型频率综合器系统框图,电荷泵增益为1cJ2T,压 控振荡器的增益为Kvco/S,滤波器的传输函数为Zp(S)。开环环路传输函数: 以=先1KZ肉 (2.1) 2TT N s 定义H(S)增益下降到1时的频率为开环环路带宽,开环环路带宽是环路分 析最重要的物理量之一,它很大程度上决定了环路建立时间,同时也影响系统零 极点分布,还会影响频率综合器的相位噪声特性。 定义Hc(S)=WHJ(1+H)为环路闭环传输函数,通过观察H(S)的阶跃响应就 可以立刻判定系统的稳定性。Hc(S)的零极点即为闭环零极点。通过观察Hc(S)零 极点的分布,可以直观判断系统的稳定性。在系统稳定的情况下,通过H(S)的 阶跃响应就可以方便的得到环路的建立时间。 R3 n Vou oVout R, C2+C3 图2-2三阶环路滤波器 图2-3二阶环路滤波器 图2-2是三阶无源滤波器。电阻R和电容C1形成的串联支路,除在原点产 生一个极点外,还产生了一个大小为11R1C1的零点用来稳定反馈环路。电容C2 和C3与电阻R3引入开环带宽之外的另外两个极点,一方面,这两个极点对压控 电压进行滤波,从而减小压控电压的波动幅度(ripple)以优化杂散(spur)性能,另 一方面,可以有效滤除DSM调制器经过噪声整形后产生的高频噪声。 电阻R和R3本身的热噪声经过环路滤波器后直接调制压控电压,从而在输 出产生相位噪声。若滤波器参数设置不合理,电阻R1和R3将会恶化频率综合器 的相位噪声性能。因此选择滤波器的参数时,在保证环路稳定性的情况下,还应 当兼顾其对输出相位噪声的影响。除此之外,对于片上集成的滤波器,其电容值 不能太大,否则会占用过多的芯片面积。 6

2~2.4 GHz 分数分频频率综合器设计 6 避开了环路的时变特性,从而可以利用 s 域模型来研究离散环路。采用连续时间 的 s 域模型后,环路分析就被大大简化了。 图 2-1 为整数分频锁相环型频率综合器系统框图,电荷泵增益为 Icp/2π,压 控振荡器的增益为 Kvco/s,滤波器的传输函数为 Zlpf(s)。开环环路传输函数: cp vco o lpf 1 () () 2π I K Hs Z s N s (2.1) 定义 Ho(s)增益下降到 1 时的频率为开环环路带宽,开环环路带宽是环路分 析最重要的物理量之一,它很大程度上决定了环路建立时间,同时也影响系统零 极点分布,还会影响频率综合器的相位噪声特性。 定义 Hc(s)=NHo/(1+Ho)为环路闭环传输函数,通过观察 Hc(s)的阶跃响应就 可以立刻判定系统的稳定性。Hc(s)的零极点即为闭环零极点。通过观察 Hc(s)零 极点的分布,可以直观判断系统的稳定性。在系统稳定的情况下,通过 Hc(s)的 阶跃响应就可以方便的得到环路的建立时间。 图 2-2 三阶环路滤波器 图 2-3 二阶环路滤波器 图 2-2 是三阶无源滤波器。电阻 R1和电容 C1 形成的串联支路,除在原点产 生一个极点外,还产生了一个大小为 1/R1C1 的零点用来稳定反馈环路。电容 C2 和 C3与电阻 R3引入开环带宽之外的另外两个极点,一方面,这两个极点对压控 电压进行滤波,从而减小压控电压的波动幅度(ripple)以优化杂散(spur)性能,另 一方面,可以有效滤除 DSM 调制器经过噪声整形后产生的高频噪声。 电阻 R1和 R3本身的热噪声经过环路滤波器后直接调制压控电压,从而在输 出产生相位噪声。若滤波器参数设置不合理,电阻 R1和 R3将会恶化频率综合器 的相位噪声性能。因此选择滤波器的参数时,在保证环路稳定性的情况下,还应 当兼顾其对输出相位噪声的影响。除此之外,对于片上集成的滤波器,其电容值 不能太大,否则会占用过多的芯片面积