第二章带隙基准电压源电路设计 如使用数字电路控制一些开关,改变接入电路的某种元件的数目。该方法实现 简单,无需增加外部控制硬件,控制信号可以由系统内部已有的数字电路产生。 本文采用数字电路控制接入电路的PNP晶体管数目,调节输出参考电压,得 到较为精确的参考电压。 2.2电路结构及性能分析 VDD 0 M9 可t ☑O VREF R13 R2 Vss 图2-4带隙基准电压源电路原理图 本文选用的带隙基准电压源电路原理图如图2-4所示,使用数字辅助控制 Q1包含的PNP双极型晶体管数目。Q2管为1个PNP晶体管,Q1管为M个 PNP晶体管。使用高增益的运算放大器实现节点1和节点2电压相等,V1=V2 设置三路电流均为I,则流过Q1中每个PNP晶体管的电流为WM。由上述条 件得: V=V2 Va:-V.n(2) s2 由各节点电压关系得: V=VEB+IR V2=VEB2 VREF VEB2 +IR2 综上条件,带隙基准电压源输出参考电压的为: 11

第二章 带隙基准电压源电路设计 11 如使用数字电路控制一些开关,改变接入电路的某种元件的数目。该方法实现 简单,无需增加外部控制硬件,控制信号可以由系统内部已有的数字电路产生。 本文采用数字电路控制接入电路的 PNP 晶体管数目,调节输出参考电压,得 到较为精确的参考电压。 2.2 电路结构及性能分析 图 2-4 带隙基准电压源电路原理图 本文选用的带隙基准电压源电路原理图如图 2-4 所示,使用数字辅助控制 Q1 包含的 PNP 双极型晶体管数目。Q2 管为 1 个 PNP 晶体管,Q1 管为 M 个 PNP 晶体管。使用高增益的运算放大器实现节点 1 和节点 2 电压相等,V1=V2。 设置三路电流均为 I,则流过 Q1 中每个 PNP 晶体管的电流为 I/M。由上述条 件得: 1 2 C1 EB1 T T S1 S1 EB2 T S2 / ln( ) ln( ) 2 ln( ) V V I I M VV V I I I V V I = = = = 由各节点电压关系得: 1 EB1 1 2 EB2 REF EB2 2 V V IR V V V V IR = + = = + 综上条件,带隙基准电压源输出参考电压的为:

基准电压源和线性稳压器的设计 Vier =V+n(2M)V R (2.10) 改变R2和R1的比值,或改变PNP晶体管个数M值均可以改变输出参考电压 的值,实现对输出参考电压的调整。从2.5小节噪声分析可以看到,R2和R1 的比值较小时,噪声性能较好,所以本文采用改变M值改变输出参考电压,实 现软修正,得到较为精确的参考电压。 oS1 ME 10 oS2 M9 Ao 3-8 oS3 Bo oS4 Co Encoder oS5 oS6 oS7 O VREF 1R2 Basic unit ·S Q10 M /ss 图2-5数字控制带隙基准电压源原理图 通过数字信号控制开关,改变PNP双极型晶体管Q1的数目M的原理如 图2-5所示。数字信号A、B和C来自内部数字单元。三个数字信号通过译码 器产生七个控制信号S1~S7,控制“开关"改变M值.M值可变范围为109~186, 以步长11进行变化。传统的带隙基准电路,双极型晶体管Q2与Q1比值通常 取得较小,本文使用的晶体管Q2与Q1的比值较大,可实现低噪声的输出参 考电压,具体分析见2.5小节噪声分析。使用11作为PNP晶体管切换步长可 以实现输出参考电压以4V左右的步长进行调整。输出参考电压的可变压范 围为-16mV~+18mV,共8个值。 Q1管用Q10~Q17管实现,其中Q10管包含109个PNP晶体管,Q11~Q17 管每组包含11个PNP晶体管。Q11~Q17管的导通/关断通过开关控制。每个 开关和PNP晶体管组构成一个基本单元,如图2-6所示。开关由PMOS管和 NMOS管反相器实现,当数字控制信号S为高电平时,NMOS管导通,PMOS 管关断,晶体管Q的基极电位被拉到Vss,晶体管导通:当数字控制信号S为 低电平时,NMOS管关断,PMOS管导通,晶体管Q的基极电位被拉到VbD, 晶体管截止。数字控制信号S1~S7由3-8译码器产生,译码器输入来自内部的 数字单元。这样就实现了对输出参考电压的软修正。 12

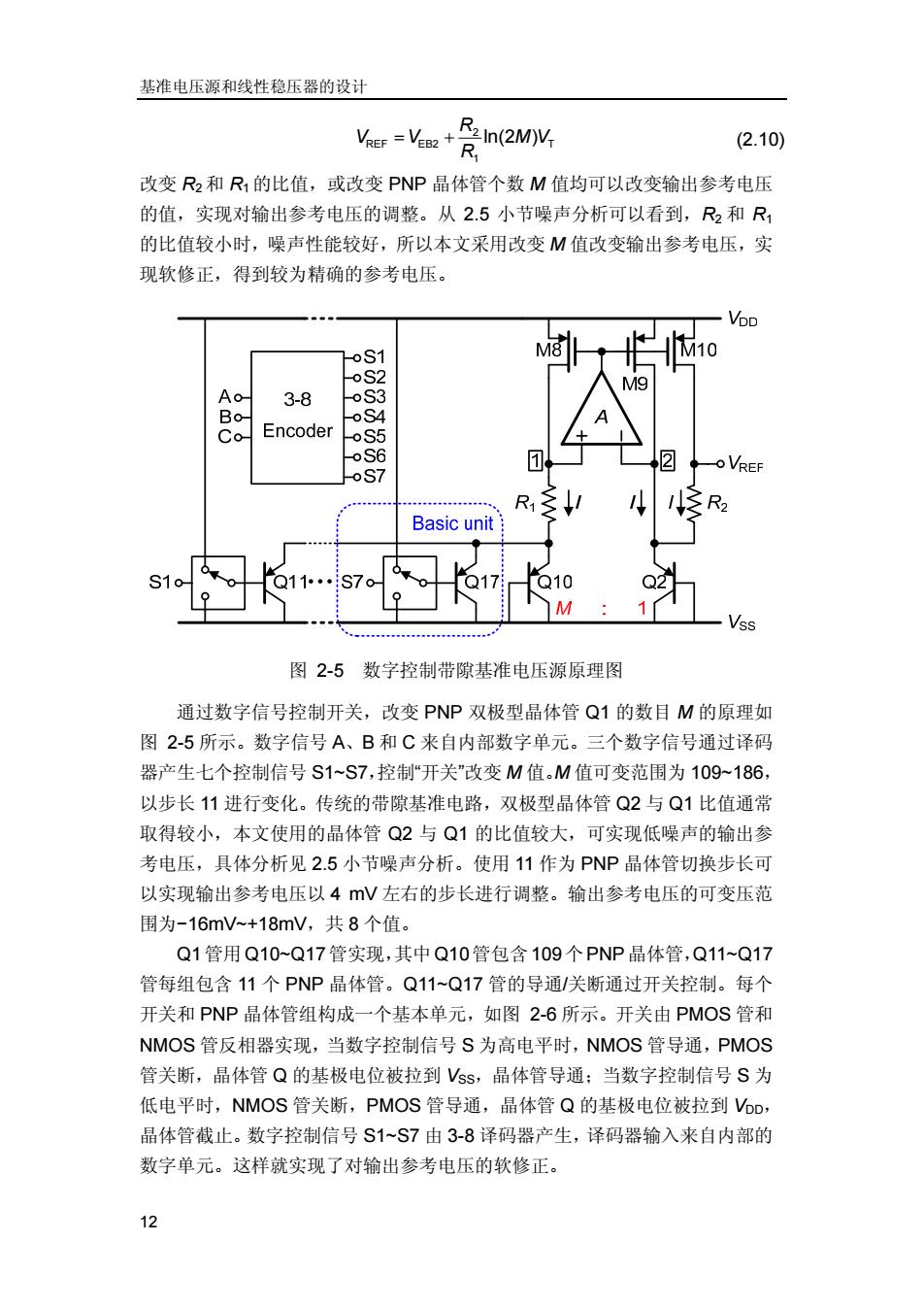

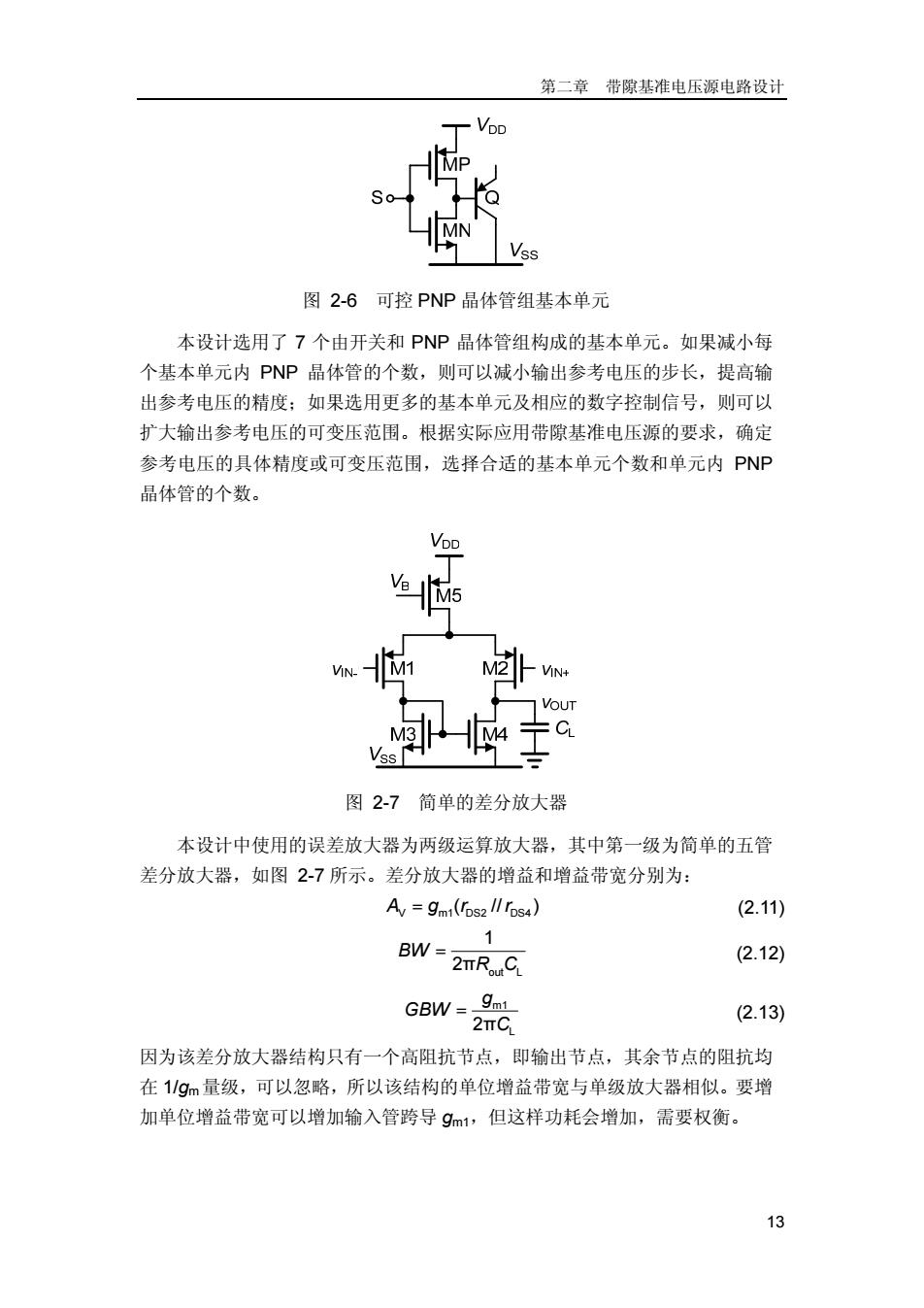

基准电压源和线性稳压器的设计 12 2 REF EB2 T 1 ln(2 ) R V V MV R = + (2.10) 改变 R2和 R1的比值,或改变 PNP 晶体管个数 M 值均可以改变输出参考电压 的值,实现对输出参考电压的调整。从 2.5 小节噪声分析可以看到,R2 和 R1 的比值较小时,噪声性能较好,所以本文采用改变 M 值改变输出参考电压,实 现软修正,得到较为精确的参考电压。 图 2-5 数字控制带隙基准电压源原理图 通过数字信号控制开关,改变 PNP 双极型晶体管 Q1 的数目 M 的原理如 图 2-5 所示。数字信号 A、B 和 C 来自内部数字单元。三个数字信号通过译码 器产生七个控制信号 S1~S7,控制“开关”改变 M 值。M 值可变范围为 109~186, 以步长 11 进行变化。传统的带隙基准电路,双极型晶体管 Q2 与 Q1 比值通常 取得较小,本文使用的晶体管 Q2 与 Q1 的比值较大,可实现低噪声的输出参 考电压,具体分析见 2.5 小节噪声分析。使用 11 作为 PNP 晶体管切换步长可 以实现输出参考电压以 4 mV 左右的步长进行调整。输出参考电压的可变压范 围为−16mV~+18mV,共 8 个值。 Q1管用Q10~Q17管实现,其中Q10管包含109个PNP晶体管,Q11~Q17 管每组包含 11 个 PNP 晶体管。Q11~Q17 管的导通/关断通过开关控制。每个 开关和 PNP 晶体管组构成一个基本单元,如图 2-6 所示。开关由 PMOS 管和 NMOS 管反相器实现,当数字控制信号 S 为高电平时,NMOS 管导通,PMOS 管关断,晶体管 Q 的基极电位被拉到 VSS,晶体管导通;当数字控制信号 S 为 低电平时,NMOS 管关断,PMOS 管导通,晶体管 Q 的基极电位被拉到 VDD, 晶体管截止。数字控制信号 S1~S7 由 3-8 译码器产生,译码器输入来自内部的 数字单元。这样就实现了对输出参考电压的软修正

第二章带隙基准电压源电路设计 ME 图2-6可控PNP晶体管组基本单元 本设计选用了7个由开关和PNP晶体管组构成的基本单元。如果减小每 个基本单元内PNP晶体管的个数,则可以减小输出参考电压的步长,提高输 出参考电压的精度:如果选用更多的基本单元及相应的数字控制信号,则可以 扩大输出参考电压的可变压范围。根据实际应用带隙基准电压源的要求,确定 参考电压的具体精度或可变压范围,选择合适的基本单元个数和单元内PNP 晶体管的个数。 M2 VOUT 图2-7简单的差分放大器 本设计中使用的误差放大器为两级运算放大器,其中第一级为简单的五管 差分放大器,如图27所示。差分放大器的增益和增益带宽分别为: Ay =gm(ros2 l ros4) (2.11) BW= 7 2TRouCL (2.12) GBW=_9mL 2TTC (2.13) 因为该差分放大器结构只有一个高阻抗节点,即输出节点,其余节点的阻抗均 在1/gm量级,可以忽略,所以该结构的单位增益带宽与单级放大器相似。要增 加单位增益带宽可以增加输入管跨导9m1,但这样功耗会增加,需要权衡。 13

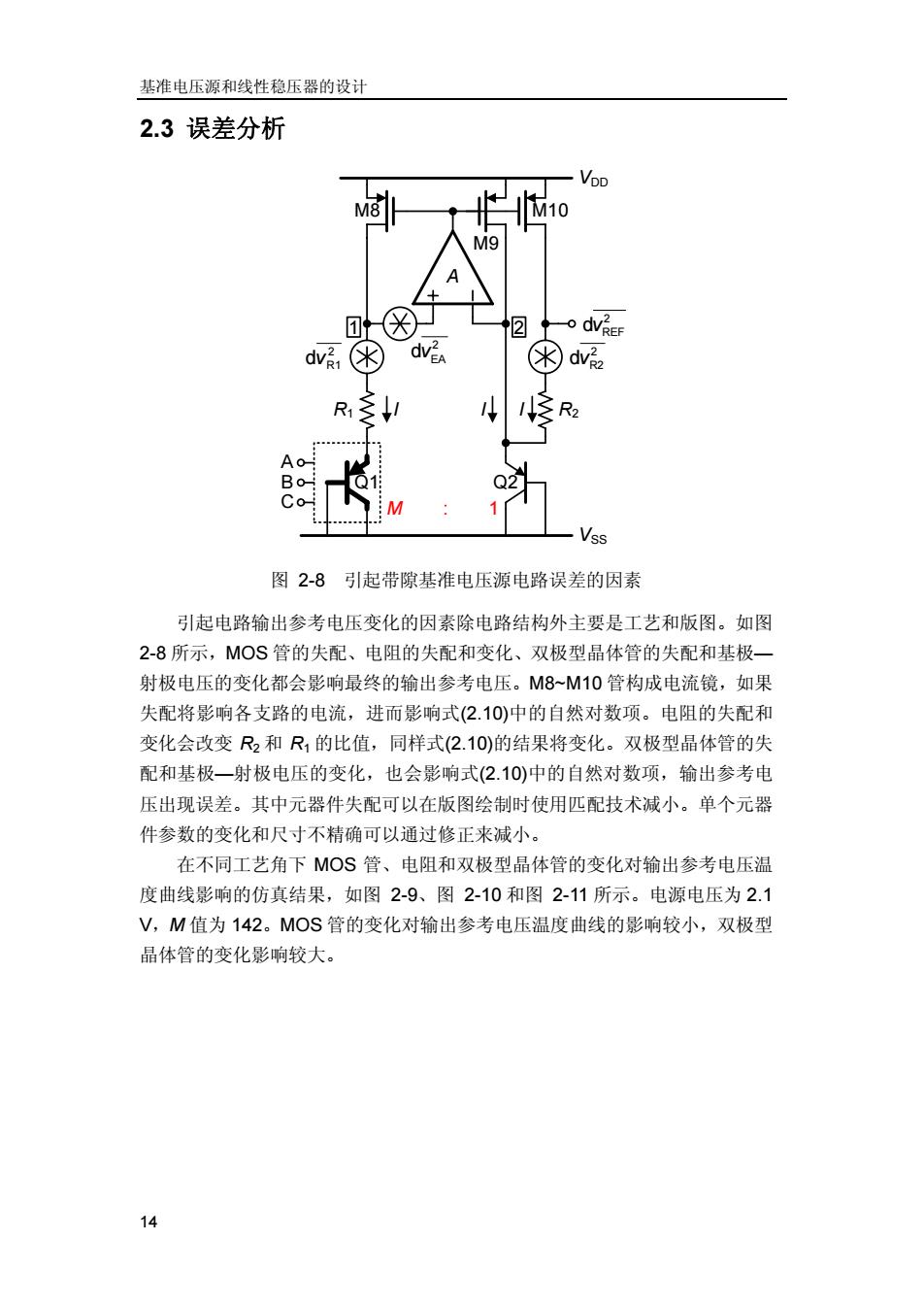

第二章 带隙基准电压源电路设计 13 图 2-6 可控 PNP 晶体管组基本单元 本设计选用了 7 个由开关和 PNP 晶体管组构成的基本单元。如果减小每 个基本单元内 PNP 晶体管的个数,则可以减小输出参考电压的步长,提高输 出参考电压的精度;如果选用更多的基本单元及相应的数字控制信号,则可以 扩大输出参考电压的可变压范围。根据实际应用带隙基准电压源的要求,确定 参考电压的具体精度或可变压范围,选择合适的基本单元个数和单元内 PNP 晶体管的个数。 图 2-7 简单的差分放大器 本设计中使用的误差放大器为两级运算放大器,其中第一级为简单的五管 差分放大器,如图 2-7 所示。差分放大器的增益和增益带宽分别为: A gr r V m1 DS2 DS4 = ( // ) (2.11) out L 1 2π BW R C = (2.12) m1 2π L g GBW C = (2.13) 因为该差分放大器结构只有一个高阻抗节点,即输出节点,其余节点的阻抗均 在 1/gm量级,可以忽略,所以该结构的单位增益带宽与单级放大器相似。要增 加单位增益带宽可以增加输入管跨导 gm1,但这样功耗会增加,需要权衡

基准电压源和线性稳压器的设计 2.3误差分析 E10 M9 2 dv d Ao C Vss 图2-8引起带隙基准电压源电路误差的因素 引起电路输出参考电压变化的因素除电路结构外主要是工艺和版图。如图 2-8所示,M○S管的失配、电阻的失配和变化、双极型晶体管的失配和基极一 射极电压的变化都会影响最终的输出参考电压。M8~M10管构成电流镜,如果 失配将影响各支路的电流,进而影响式(2.10)中的自然对数项。电阻的失配和 变化会改变R2和R1的比值,同样式(2.10)的结果将变化。双极型晶体管的失 配和基极一射极电压的变化,也会影响式(2.10)中的自然对数项,输出参考电 压出现误差。其中元器件失配可以在版图绘制时使用匹配技术减小。单个元器 件参数的变化和尺寸不精确可以通过修正来减小。 在不同工艺角下MOS管、电阻和双极型晶体管的变化对输出参考电压温 度曲线影响的仿真结果,如图2-9、图2-10和图2-11所示。电源电压为2.1 V,M值为142。MOS管的变化对输出参考电压温度曲线的影响较小,双极型 晶体管的变化影响较大。 14

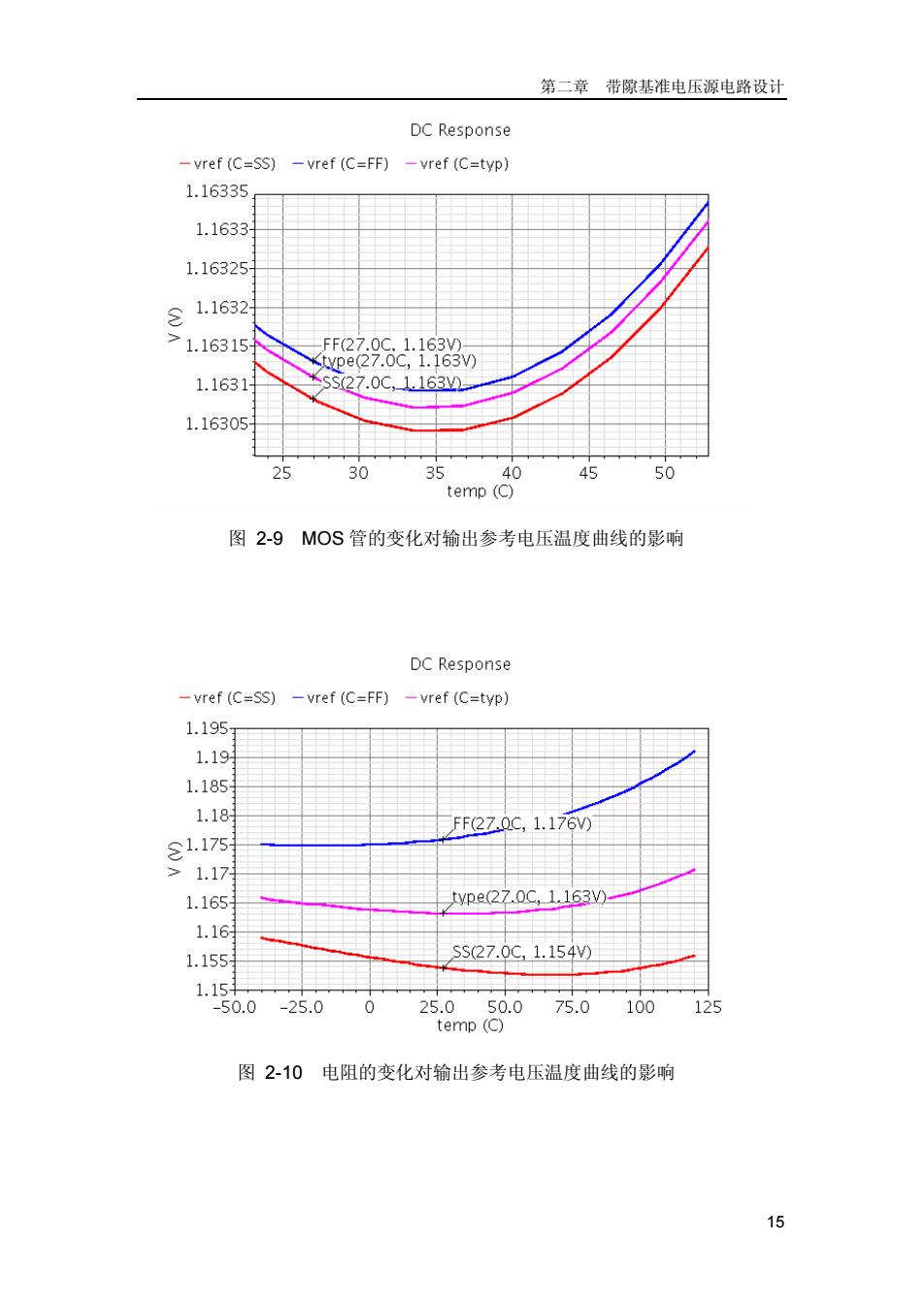

基准电压源和线性稳压器的设计 14 2.3 误差分析 R1 R2 Q1 Q2 I I I M : 1 VDD VSS A C B M8 M10 M9 v 2 d EA 2 d R1 v 2 d R2 v 2 d REF v A 1 2 图 2-8 引起带隙基准电压源电路误差的因素 引起电路输出参考电压变化的因素除电路结构外主要是工艺和版图。如图 2-8 所示,MOS 管的失配、电阻的失配和变化、双极型晶体管的失配和基极— 射极电压的变化都会影响最终的输出参考电压。M8~M10 管构成电流镜,如果 失配将影响各支路的电流,进而影响式(2.10)中的自然对数项。电阻的失配和 变化会改变 R2 和 R1 的比值,同样式(2.10)的结果将变化。双极型晶体管的失 配和基极—射极电压的变化,也会影响式(2.10)中的自然对数项,输出参考电 压出现误差。其中元器件失配可以在版图绘制时使用匹配技术减小。单个元器 件参数的变化和尺寸不精确可以通过修正来减小。 在不同工艺角下 MOS 管、电阻和双极型晶体管的变化对输出参考电压温 度曲线影响的仿真结果,如图 2-9、图 2-10 和图 2-11 所示。电源电压为 2.1 V,M 值为 142。MOS 管的变化对输出参考电压温度曲线的影响较小,双极型 晶体管的变化影响较大

第二章带隙基准电压源电路设计 DC Response -vref(C=SS)-vref(C=FF)-vref (C=typ) 1.16335 1.1633 1.16325 31.1632 >1.16315 FF(27.0C.1.163V) pe(27.0C,1.163V) 1.16311 sS(27.0,1.1630 1.16305 25 30 35 40 45 50 temp (C) 图2-9MOS管的变化对输出参考电压温度曲线的影响 DC Response -vref (C=SS)-vref(C=FF)-vref(C=typ) 1.195 1.19 1.185 1.18 FF(27.0C,1.1760 1.175 >1.17 1.165 typ.e(27.0C,1.163Y0 1.16 1.155 SS(27.0C,1.1540 1.151 -50.0-25.0 0 25.050.0 75.0 100 125 temp (C) 图2-10电阻的变化对输出参考电压温度曲线的影响 15

第二章 带隙基准电压源电路设计 15 图 2-9 MOS 管的变化对输出参考电压温度曲线的影响 图 2-10 电阻的变化对输出参考电压温度曲线的影响