第一章概述 Proc.IEEE,vol.94,no.1,pp.198-209,Jan.2006 [3]T.Deliyannis,Y.Sun and J.K.Fidler,Continuous-Time Active Filter Design, CRC Press,USA,January 1999. [4]Yichuang Sun,Design of high frequency integrated analogue filters,The Institution of Electrical Engineers,London,United Kingdom,2002 0

第一章 概述 3 Proc. IEEE, vol. 94, no. 1, pp. 198–209, Jan. 2006. [3] T. Deliyannis, Y. Sun and J. K. Fidler, Continuous-Time Active Filter Design, CRC Press, USA, January 1999. [4] Yichuang Sun, Design of high frequency integrated analogue filters, The Institution of Electrical Engineers, London, United Kingdom, 2002

第二章器件的偏差与失配 第二章器件的偏差与失配 2.1偏差的来源 Equation Section2当集成电路在制造的时候,有很多因素会导致器件的有 效尺寸和电学特性不同于电路设计人员所设计的值。这些因素可以分成以下几 类:系统偏差(Systematic variations)、工艺偏差(Process variations)和随机偏差 (Random variations)。系统偏差是那些即使电路大批量生产,也都会重复发生的 固有的偏差。工艺偏差是由于制造条件(工艺步骤的温度、杂质浓度和离子浓度 等)无法精确地保持一致,而导致的器件参数不一致。随机偏差是按统计规律地 出现在每个器件上的参数偏差。 2.1.1系统偏差 在芯片制造时,光刻技术的二维效应会导致器件的有效尺寸和掩膜版上的不 同。如图2-1所示是两个例子:图()是杂质的横向扩散导致实际的阱区域比掩 膜上的尺寸大。这是因为杂质的扩散不仅仅在离子注入的过程中发生,还发生在 之后的高温工序中,例如退火;图(b)是过刻蚀(Over-etching)的情况,在SiO2 保护层下面的多晶硅边缘被过度腐蚀,从而导致了多晶硅层比相应的掩膜层要 小。 SiO2 protection SiO2 protection Polysilicon ☑ Well Lateral diffusion under SiO2 Overetching (a) (b) 图21二维效应导致器件实际尺寸不同于版图掩膜 上面两种情况都是工艺步骤对器件尺寸的影响,然而,器件所处的位置和周 围的环境,也将影响其电学特性,比如相互靠近的电阻之间会产生寄生电容。另 外,还有一些更细微的邻近效应[2],如图2-2所示,在离子注入形成阱的过程中, 部分入射原子在光刻胶边缘发生水平方向的散射,嵌入阱边缘片的硅表面。这将 导致n阱表面的杂质浓度在阱边缘处更高,在距离um或更大的范围内逐渐减

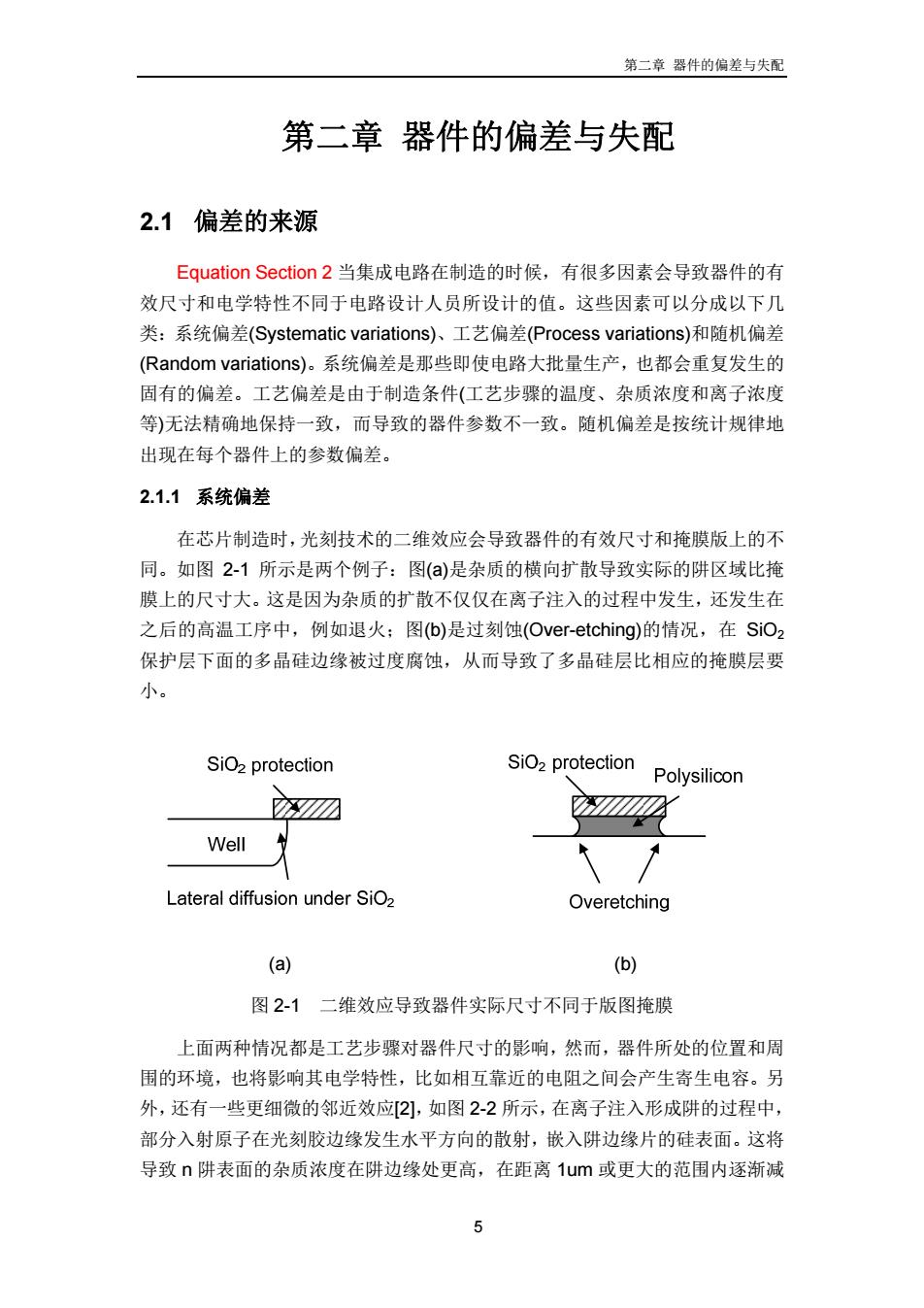

第二章 器件的偏差与失配 5 第二章 器件的偏差与失配 2.1 偏差的来源 Equation Section 2 当集成电路在制造的时候,有很多因素会导致器件的有 效尺寸和电学特性不同于电路设计人员所设计的值。这些因素可以分成以下几 类:系统偏差(Systematic variations)、工艺偏差(Process variations)和随机偏差 (Random variations)。系统偏差是那些即使电路大批量生产,也都会重复发生的 固有的偏差。工艺偏差是由于制造条件(工艺步骤的温度、杂质浓度和离子浓度 等)无法精确地保持一致,而导致的器件参数不一致。随机偏差是按统计规律地 出现在每个器件上的参数偏差。 2.1.1 系统偏差 在芯片制造时,光刻技术的二维效应会导致器件的有效尺寸和掩膜版上的不 同。如图 2-1 所示是两个例子:图(a)是杂质的横向扩散导致实际的阱区域比掩 膜上的尺寸大。这是因为杂质的扩散不仅仅在离子注入的过程中发生,还发生在 之后的高温工序中,例如退火;图(b)是过刻蚀(Over-etching)的情况,在 SiO2 保护层下面的多晶硅边缘被过度腐蚀,从而导致了多晶硅层比相应的掩膜层要 小。 上面两种情况都是工艺步骤对器件尺寸的影响,然而,器件所处的位置和周 围的环境,也将影响其电学特性,比如相互靠近的电阻之间会产生寄生电容。另 外,还有一些更细微的邻近效应[2],如图 2-2 所示,在离子注入形成阱的过程中, 部分入射原子在光刻胶边缘发生水平方向的散射,嵌入阱边缘片的硅表面。这将 导致 n 阱表面的杂质浓度在阱边缘处更高,在距离 1um 或更大的范围内逐渐减 (a) (b) 图 2-1 二维效应导致器件实际尺寸不同于版图掩膜

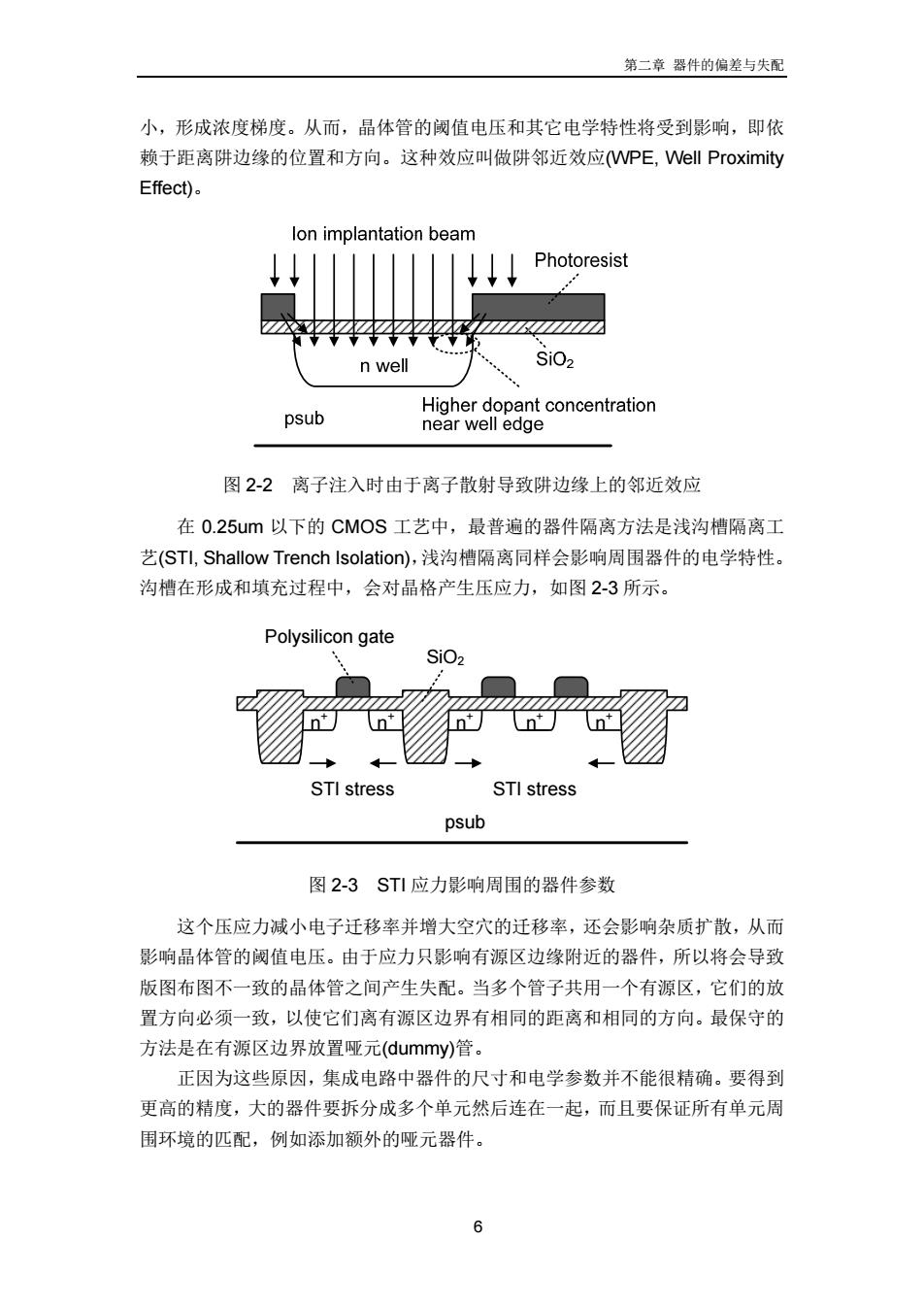

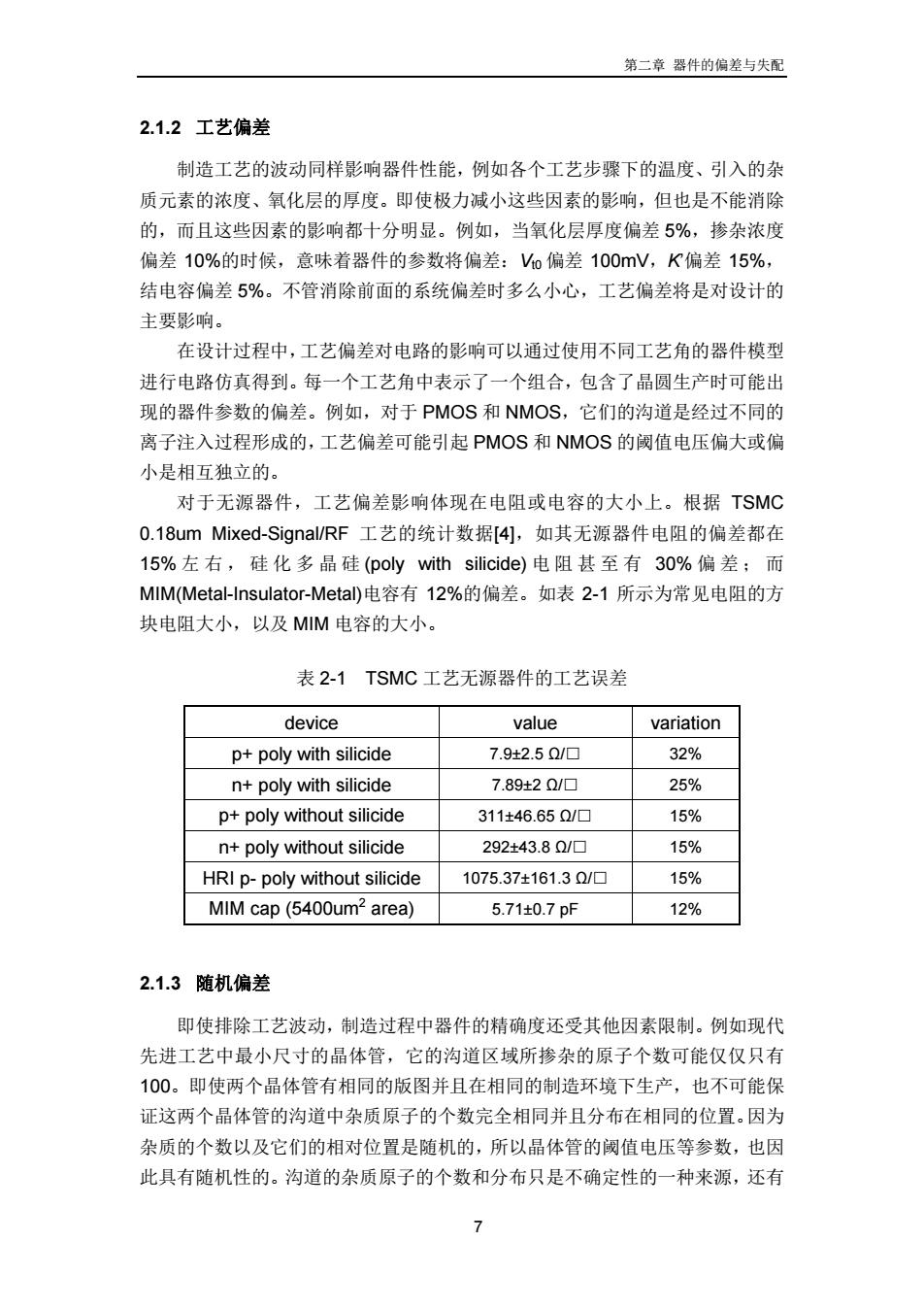

第二章器件的偏差与失配 小,形成浓度梯度。从而,晶体管的阈值电压和其它电学特性将受到影响,即依 赖于距离阱边缘的位置和方向。这种效应叫做阱邻近效应(WPE,Well Proximity Effect)。 lon implantation beam Photoresist n well SiO2 Higher dopant concentration psub near well edge 图2-2离子注入时由于离子散射导致阱边缘上的邻近效应 在0.25um以下的CMOS工艺中,最普遍的器件隔离方法是浅沟槽隔离工 艺(STl,Shallow Trench Isolation),浅沟槽隔离同样会影响周围器件的电学特性。 沟槽在形成和填充过程中,会对晶格产生压应力,如图2-3所示。 Polysilicon gate SiO2 STI stress STI stress psub 图2-3ST1应力影响周围的器件参数 这个压应力减小电子迁移率并增大空穴的迁移率,还会影响杂质扩散,从而 影响晶体管的阈值电压。由于应力只影响有源区边缘附近的器件,所以将会导致 版图布图不一致的晶体管之间产生失配。当多个管子共用一个有源区,它们的放 置方向必须一致,以使它们离有源区边界有相同的距离和相同的方向。最保守的 方法是在有源区边界放置哑元(dummy)管。 正因为这些原因,集成电路中器件的尺寸和电学参数并不能很精确。要得到 更高的精度,大的器件要拆分成多个单元然后连在一起,而且要保证所有单元周 围环境的匹配,例如添加额外的哑元器件

第二章 器件的偏差与失配 6 小,形成浓度梯度。从而,晶体管的阈值电压和其它电学特性将受到影响,即依 赖于距离阱边缘的位置和方向。这种效应叫做阱邻近效应(WPE, Well Proximity Effect)。 图 2-2 离子注入时由于离子散射导致阱边缘上的邻近效应 在 0.25um 以下的 CMOS 工艺中,最普遍的器件隔离方法是浅沟槽隔离工 艺(STI, Shallow Trench Isolation),浅沟槽隔离同样会影响周围器件的电学特性。 沟槽在形成和填充过程中,会对晶格产生压应力,如图 2-3 所示。 psub SiO2 n+ n+ n+ n+ n+ STI stress STI stress Polysilicon gate 图 2-3 STI 应力影响周围的器件参数 这个压应力减小电子迁移率并增大空穴的迁移率,还会影响杂质扩散,从而 影响晶体管的阈值电压。由于应力只影响有源区边缘附近的器件,所以将会导致 版图布图不一致的晶体管之间产生失配。当多个管子共用一个有源区,它们的放 置方向必须一致,以使它们离有源区边界有相同的距离和相同的方向。最保守的 方法是在有源区边界放置哑元(dummy)管。 正因为这些原因,集成电路中器件的尺寸和电学参数并不能很精确。要得到 更高的精度,大的器件要拆分成多个单元然后连在一起,而且要保证所有单元周 围环境的匹配,例如添加额外的哑元器件

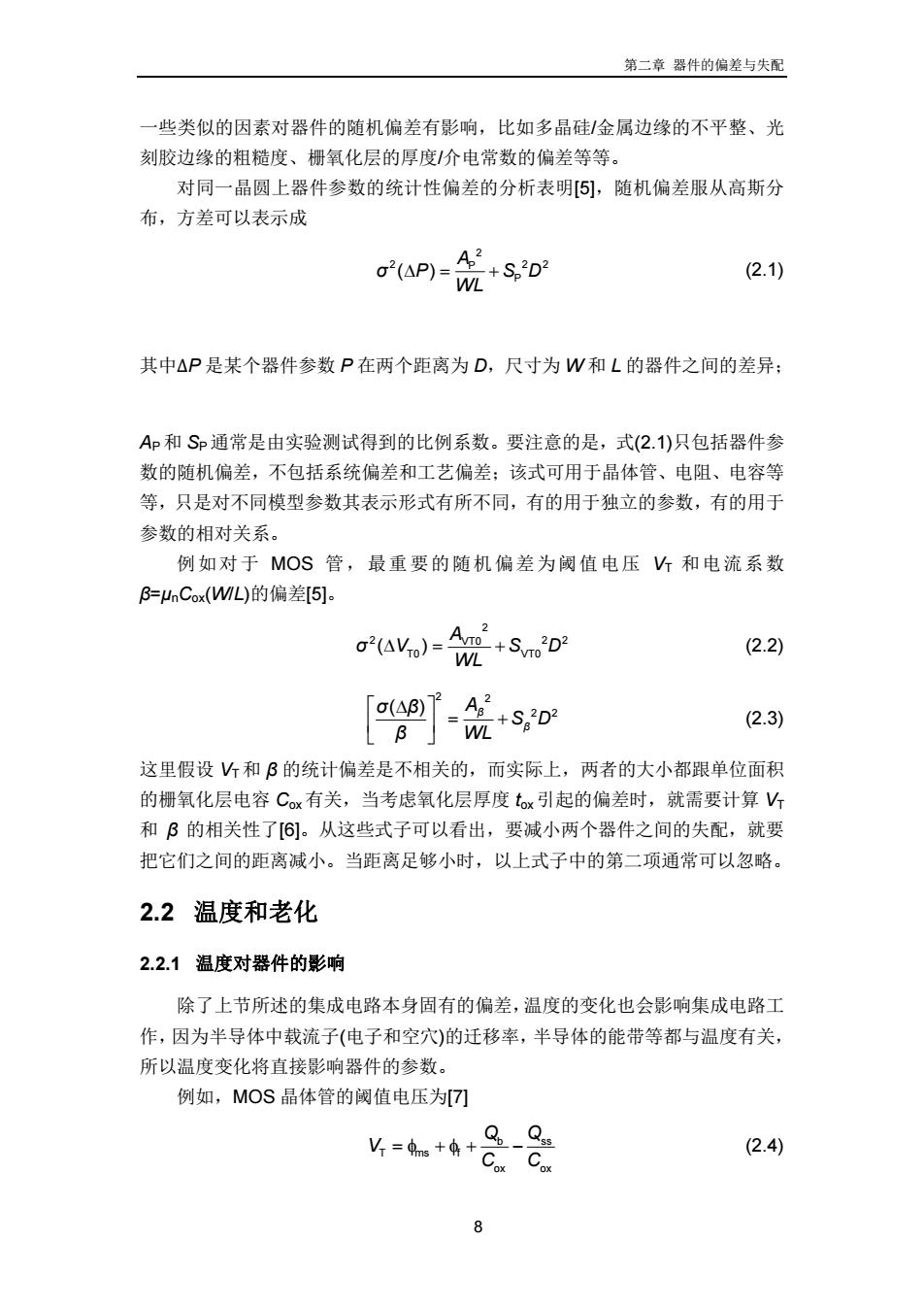

第二章器件的偏差与失配 2.1.2工艺偏差 制造工艺的波动同样影响器件性能,例如各个工艺步骤下的温度、引入的杂 质元素的浓度、氧化层的厚度。即使极力减小这些因素的影响,但也是不能消除 的,而且这些因素的影响都十分明显。例如,当氧化层厚度偏差5%,掺杂浓度 偏差10%的时候,意味着器件的参数将偏差:Vo偏差100mV,K偏差15%, 结电容偏差5%。不管消除前面的系统偏差时多么小心,工艺偏差将是对设计的 主要影响。 在设计过程中,工艺偏差对电路的影响可以通过使用不同工艺角的器件模型 进行电路仿真得到。每一个工艺角中表示了一个组合,包含了晶圆生产时可能出 现的器件参数的偏差。例如,对于PMOS和NMOS,它们的沟道是经过不同的 离子注入过程形成的,工艺偏差可能引起PMOS和NMOS的阈值电压偏大或偏 小是相互独立的。 对于无源器件,工艺偏差影响体现在电阻或电容的大小上。根据TSMC 0.18 um Mixed-Signal/RF工艺的统计数据[4],如其无源器件电阻的偏差都在 15%左右,硅化多晶硅(poly with silicide))电阻甚至有30%偏差;而 MlM(Metal-Insulator-Meta)电容有12%的偏差。如表2-1所示为常见电阻的方 块电阻大小,以及MM电容的大小。 表2-1TSMC工艺无源器件的工艺误差 device value variation p+poly with silicide 7.9±2.5/▣ 32% n+poly with silicide 7.89±2Ω/☐ 25% p+poly without silicide 311±46.650/☐ 15% n+poly without silicide 292±43.8/▣ 15% HRI p-poly without silicide 1075.37±161.30/▣ 15% MIM cap(5400um2 area) 5.71±0.7pf 12% 2.1.3随机偏差 即使排除工艺波动,制造过程中器件的精确度还受其他因素限制。例如现代 先进工艺中最小尺寸的晶体管,它的沟道区域所掺杂的原子个数可能仅仅只有 100。即使两个晶体管有相同的版图并且在相同的制造环境下生产,也不可能保 证这两个晶体管的沟道中杂质原子的个数完全相同并且分布在相同的位置。因为 杂质的个数以及它们的相对位置是随机的,所以晶体管的阈值电压等参数,也因 此具有随机性的。沟道的杂质原子的个数和分布只是不确定性的一种来源,还有 7

第二章 器件的偏差与失配 7 2.1.2 工艺偏差 制造工艺的波动同样影响器件性能,例如各个工艺步骤下的温度、引入的杂 质元素的浓度、氧化层的厚度。即使极力减小这些因素的影响,但也是不能消除 的,而且这些因素的影响都十分明显。例如,当氧化层厚度偏差 5%,掺杂浓度 偏差 10%的时候,意味着器件的参数将偏差:Vt0 偏差 100mV,K’偏差 15%, 结电容偏差 5%。不管消除前面的系统偏差时多么小心,工艺偏差将是对设计的 主要影响。 在设计过程中,工艺偏差对电路的影响可以通过使用不同工艺角的器件模型 进行电路仿真得到。每一个工艺角中表示了一个组合,包含了晶圆生产时可能出 现的器件参数的偏差。例如,对于 PMOS 和 NMOS,它们的沟道是经过不同的 离子注入过程形成的,工艺偏差可能引起 PMOS 和 NMOS 的阈值电压偏大或偏 小是相互独立的。 对于无源器件,工艺偏差影响体现在电阻或电容的大小上。根据 TSMC 0.18um Mixed-Signal/RF 工艺的统计数据[4],如其无源器件电阻的偏差都在 15% 左右,硅化多晶硅 (poly with silicide) 电阻甚至有 30% 偏差;而 MIM(Metal-Insulator-Metal)电容有 12%的偏差。如表 2-1 所示为常见电阻的方 块电阻大小,以及 MIM 电容的大小。 表 2-1 TSMC 工艺无源器件的工艺误差 device value variation p+ poly with silicide 7.9±2.5 Ω/□ 32% n+ poly with silicide 7.89±2 Ω/□ 25% p+ poly without silicide 311±46.65 Ω/□ 15% n+ poly without silicide 292±43.8 Ω/□ 15% HRI p- poly without silicide 1075.37±161.3 Ω/□ 15% MIM cap (5400um2 area) 5.71±0.7 pF 12% 2.1.3 随机偏差 即使排除工艺波动,制造过程中器件的精确度还受其他因素限制。例如现代 先进工艺中最小尺寸的晶体管,它的沟道区域所掺杂的原子个数可能仅仅只有 100。即使两个晶体管有相同的版图并且在相同的制造环境下生产,也不可能保 证这两个晶体管的沟道中杂质原子的个数完全相同并且分布在相同的位置。因为 杂质的个数以及它们的相对位置是随机的,所以晶体管的阈值电压等参数,也因 此具有随机性的。沟道的杂质原子的个数和分布只是不确定性的一种来源,还有

第二章器件的偏差与失配 一些类似的因素对器件的随机偏差有影响,比如多晶硅/金属边缘的不平整、光 刻胶边缘的粗糙度、栅氧化层的厚度/介电常数的偏差等等。 对同一晶圆上器件参数的统计性偏差的分析表明[],随机偏差服从高斯分 布,方差可以表示成 24P)=+5,3D2 (2.1) WL 其中△P是某个器件参数P在两个距离为D,尺寸为W和L的器件之间的差异; Ap和SP通常是由实验测试得到的比例系数。要注意的是,式(2.1)只包括器件参 数的随机偏差,不包括系统偏差和工艺偏差;该式可用于晶体管、电阻、电容等 等,只是对不同模型参数其表示形式有所不同,有的用于独立的参数,有的用于 参数的相对关系。 例如对于MOS管,最重要的随机偏差为阈值电压V和电流系数 B=Un Cox(WMWL)的偏差[5]: 2(AVio)= Avo+SoD 2 (2.2) WL =M+9D2 (2.3) B 这里假设V和B的统计偏差是不相关的,而实际上,两者的大小都跟单位面积 的栅氧化层电容Cox有关,当考虑氧化层厚度tx引起的偏差时,就需要计算V 和B的相关性了[6]。从这些式子可以看出,要减小两个器件之间的失配,就要 把它们之间的距离减小。当距离足够小时,以上式子中的第二项通常可以忽略。 2.2温度和老化 2.2.1温度对器件的影响 除了上节所述的集成电路本身固有的偏差,温度的变化也会影响集成电路工 作,因为半导体中载流子(电子和空穴)的迁移率,半导体的能带等都与温度有关, 所以温度变化将直接影响器件的参数。 例如,MOS晶体管的阈值电压为7] V=中s+4+ QQ:s (2.4) Cox Cox 8

第二章 器件的偏差与失配 8 一些类似的因素对器件的随机偏差有影响,比如多晶硅/金属边缘的不平整、光 刻胶边缘的粗糙度、栅氧化层的厚度/介电常数的偏差等等。 对同一晶圆上器件参数的统计性偏差的分析表明[5],随机偏差服从高斯分 布,方差可以表示成 2 2 22 P P ( ) A σ P SD WL (2.1) 其中∆P 是某个器件参数 P 在两个距离为 D,尺寸为 W 和 L 的器件之间的差异; AP和 SP通常是由实验测试得到的比例系数。要注意的是,式(2.1)只包括器件参 数的随机偏差,不包括系统偏差和工艺偏差;该式可用于晶体管、电阻、电容等 等,只是对不同模型参数其表示形式有所不同,有的用于独立的参数,有的用于 参数的相对关系。 例如对于 MOS 管,最重要的随机偏差为阈值电压 VT 和电流系数 β=μnCox(W/L)的偏差[5]。 2 2 22 VT0 T0 VT0 ( ) A σ V SD WL (2.2) 2 2 2 2 ( ) β β σ β A S D β WL (2.3) 这里假设 VT和 β 的统计偏差是不相关的,而实际上,两者的大小都跟单位面积 的栅氧化层电容 Cox有关,当考虑氧化层厚度 tox引起的偏差时,就需要计算 VT 和 β 的相关性了[6]。从这些式子可以看出,要减小两个器件之间的失配,就要 把它们之间的距离减小。当距离足够小时,以上式子中的第二项通常可以忽略。 2.2 温度和老化 2.2.1 温度对器件的影响 除了上节所述的集成电路本身固有的偏差,温度的变化也会影响集成电路工 作,因为半导体中载流子(电子和空穴)的迁移率,半导体的能带等都与温度有关, 所以温度变化将直接影响器件的参数。 例如,MOS 晶体管的阈值电压为[7] b ss ms o T f ox x V Q Q C C (2.4)