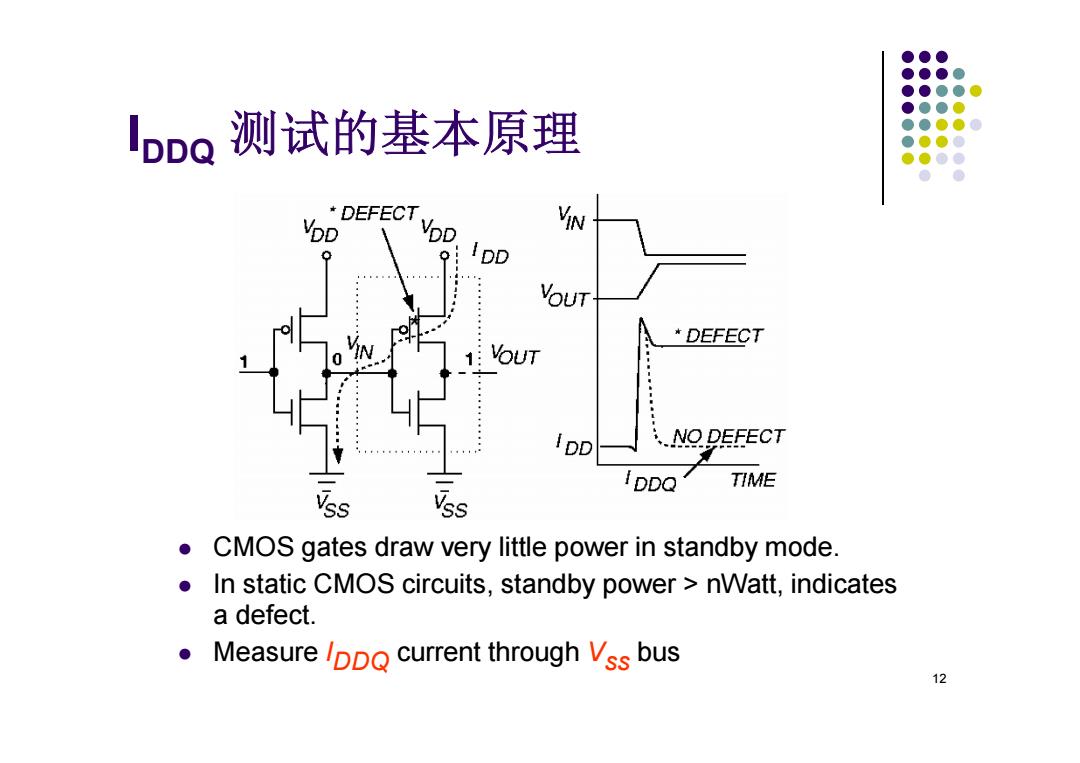

●● ●● ● lbQ测试的基本原理 ●● ●●●● ·DEFECT VDD,. Vp N 、100 VOUT DEFECT 1:6UT IDD .NO DEFECT I DDQ TIME Vss Vss e CMOS gates draw very little power in standby mode. ● In static CMOS circuits,standby power nWatt,indicates a defect. Measure /DDQ current through Vss bus 12

12 IDDQ 测试的基本原理 CMOS gates draw very little power in standby mode. In static CMOS circuits, standby power > nWatt, indicates a defect. Measure I DDQ current through Vss bus

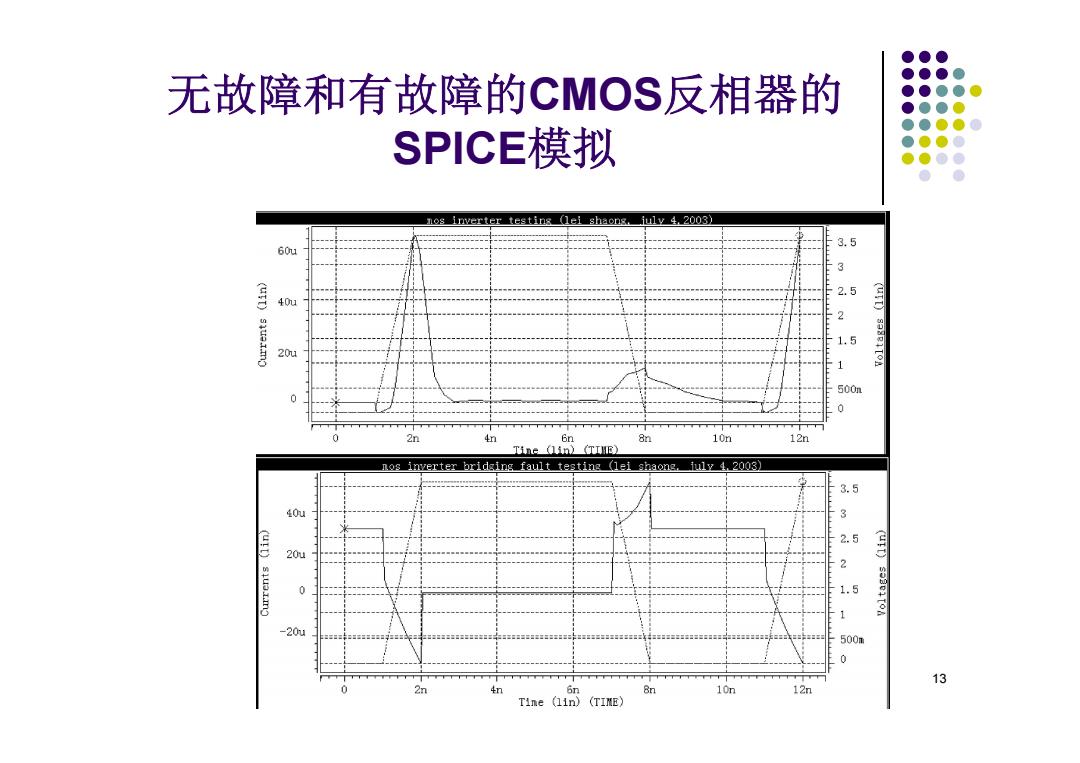

无故障和有故障的CMOS反相器的 ● ●● SPICE模拟 ●●●● ●● 2003 3.5 60u 3 2.5 40 215 20 500 6n 10m 12n inverter faul t (lei shaong.iuly 4.2003) 3.5 40 3 20u 142 1.5 -20u 500 13 2n 10n 12n Tine (lin) (TIME)

13 无故障和有故障的CMOS反相器的 SPICE模拟

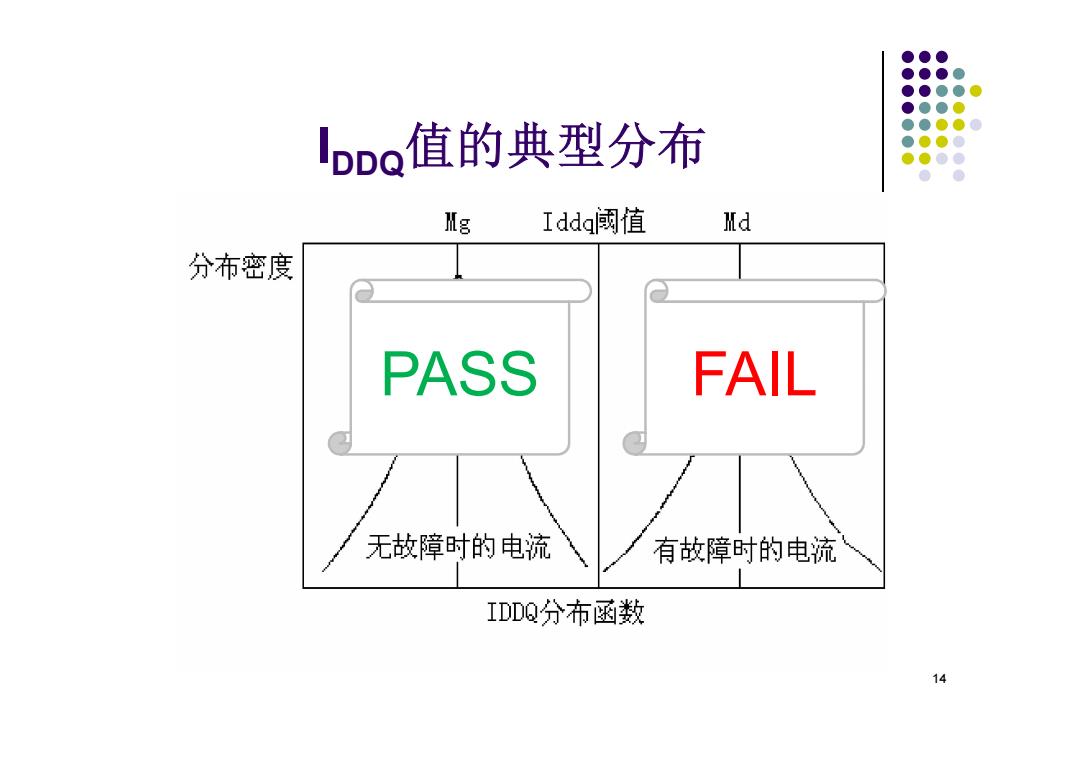

●●● ●●●● ●●●●● ●●●● bDQ值的典型分布 ●●●●0 ●●0● ●●o● Mg Iddg阚值 d 分布密度 PASS FAIL 无故障时的电流 有故障时的电流 IDDQ分布函数 14

14 IDDQ值的典型分布 PASS FAIL

●●●● ●●●●0 栅长与lba关系 ●●●0 ●●●d ●●●● ●●o ● ● Ioff(pA/um) 100 1 栅长(um 0.20.3 15

15 栅长与IDDQ关系

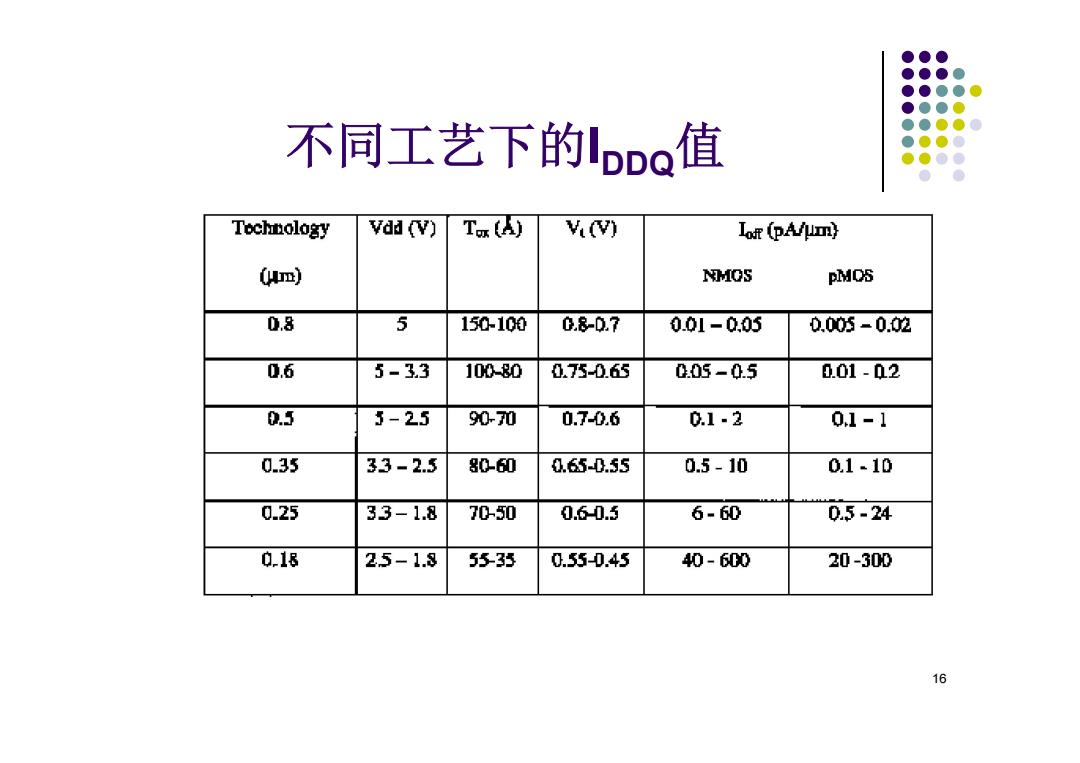

●●● ●●●● ●●●●● ●●●● 不同工艺下的lba值 ●●●●0 ●●●● ●●o● ●● Technology Va时v) Tox(A) v(V) Iof (pA/umn) (m) NMOS PMOS 0.8 5 150-100 0.8-0.7 001-0.05 0.005-0.02 0.6 5-33 100-80 0.75-0.65 005-0.5 0.01-02 0.5 3-25 90-70 0.7-0.6 0.1-2 01-1 0.35 33-2.5 80-60 0.65-0.55 0.5-10 0.1-10 0.25 33-1.8 70-50 0.6-0.5 6-60 05-24 0.18 25-1.8 55-35 0.550.45 40-600 20-300 16

16 不同工艺下的IDDQ值