电子料做女学 University of Electroe Scioncad TechofChina /986 Chapter 13 Bit-Level Arithmetic Architectures Xiang LING National Key Lab of Science and Technology on Communications

Chapter 13 Bit-Level Arithmetic Architectures Xiang LING National Key Lab of Science and Technology on Communications

13.1 Introduction /956 Three implementation styles ■bit parallel bit serial ■digit serial The major emphasis is on architecture design methodologies for mapping algorithms to arithmetic architecture at bit-level. 2021年2月 2

13.1 Introduction Three implementation styles bit parallel bit serial digit serial The major emphasis is on architecture design methodologies for mapping algorithms to arithmetic architecture at bit-level. 2021年2月 2

Number representation /96 A W-bit fixed point two's complement number A is represented as A=aw-1.aw-2...a1ao where the bits ai,0≤i≤W-l,are either0or1, and the MSB is the sign bit. The value of this number is in the range of [-1,1-2-W+1]and is given by A=-aw-1+∑aw-1-i2 example: 如 1000=[-1]cmp ■ 0111=-0+0.5+0.25+0.125=[0.875]cmp=1-23 ,0101=-0+0.5+0.125=[0.625]cmp 2021年2月 3

Number representation A W-bit fixed point two’s complement number A is represented as : A=aw-1 .aw-2…a1a0 where the bits ai , 0 ≤ i ≤ W-1, are either 0 or 1, and the MSB is the sign bit. The value of this number is in the range of [-1, 1–2 -W+1] and is given by : A = - aw-1 + Σaw-1-i2 -i example: 1000=[-1]cmp 0111=-0+0.5+0.25+0.125=[0.875]cmp=1-2 -3 0101=-0+0.5+0.125=[0.625]cmp 2021年2月 3

/966 For bit-serial implementations,constant word length multipliers are considered.For a WXW bit multiplication the W most-significant bits of the (2W-1)-bit product are retained. 2021年2月 4

For bit-serial implementations, constant word length multipliers are considered. For a W×W bit multiplication the W most-significant bits of the (2W-1)-bit product are retained. 2021年2月 4

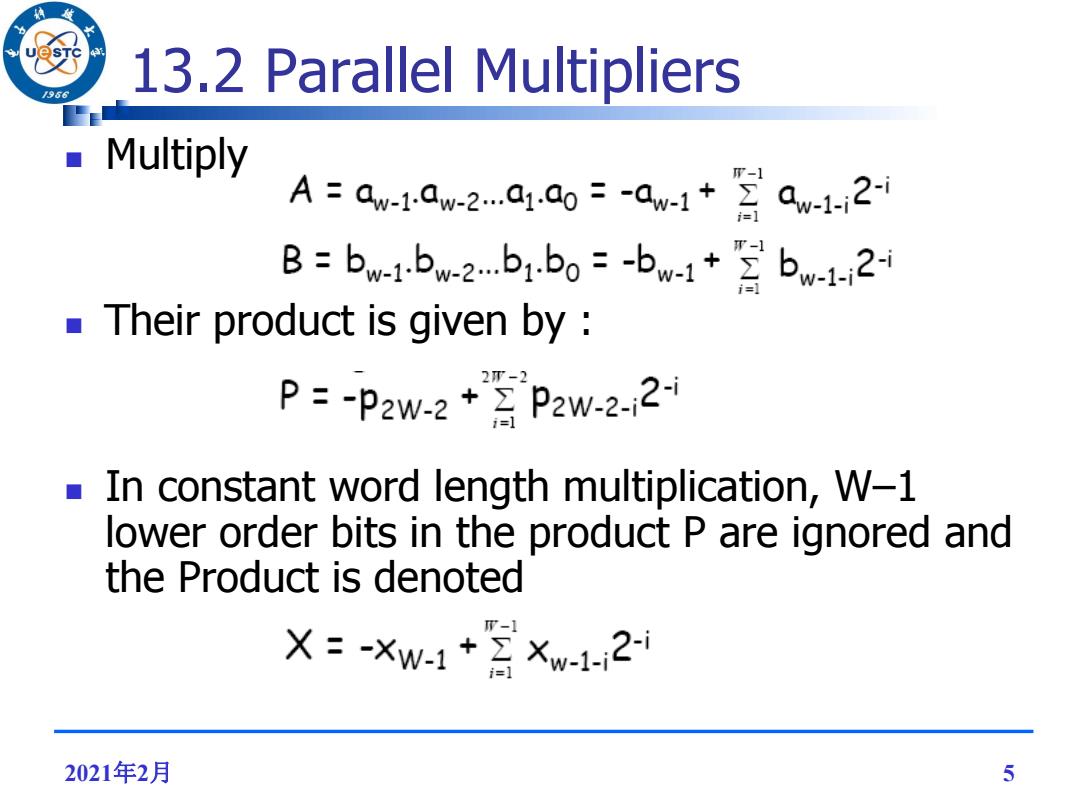

13.2 Parallel Multipliers 96 Multiply A=aw-1.aw-2...a1.o=-w1aw-1-i2i B=bw-1.bw2bo=-bb Their product is given by 2T-2 P=-P2w-2+gP2w-2-2 In constant word length multiplication,W-1 lower order bits in the product P are ignored and the Product is denoted r-1 X=-Xw-1+三×w-12-1 2021年2月 5

13.2 Parallel Multipliers Multiply Their product is given by : In constant word length multiplication, W–1 lower order bits in the product P are ignored and the Product is denoted 2021年2月 5