第六章扫描设计 子科发女学 /966 University of Electronic Science and Technology of China

第六章 扫描设计

本章要点 冬讨论为什么要使用扫描设计 Why? 理解扫描设计的原理What? 掌握扫描设计的几种基本结构Vhich: 熟悉DFT Compiler的设计流程HoW? 冬完成一个简单的扫描设计的实例 集成电路可测性设计 第六章:扫描设计3

本章要点 讨论为什么要使用扫描设计 理解扫描设计的原理 掌握扫描设计的几种基本结构 熟悉DFT Compiler的设计流程 完成一个简单的扫描设计的实例 集成电路可测性设计 第六章:扫描设计 3

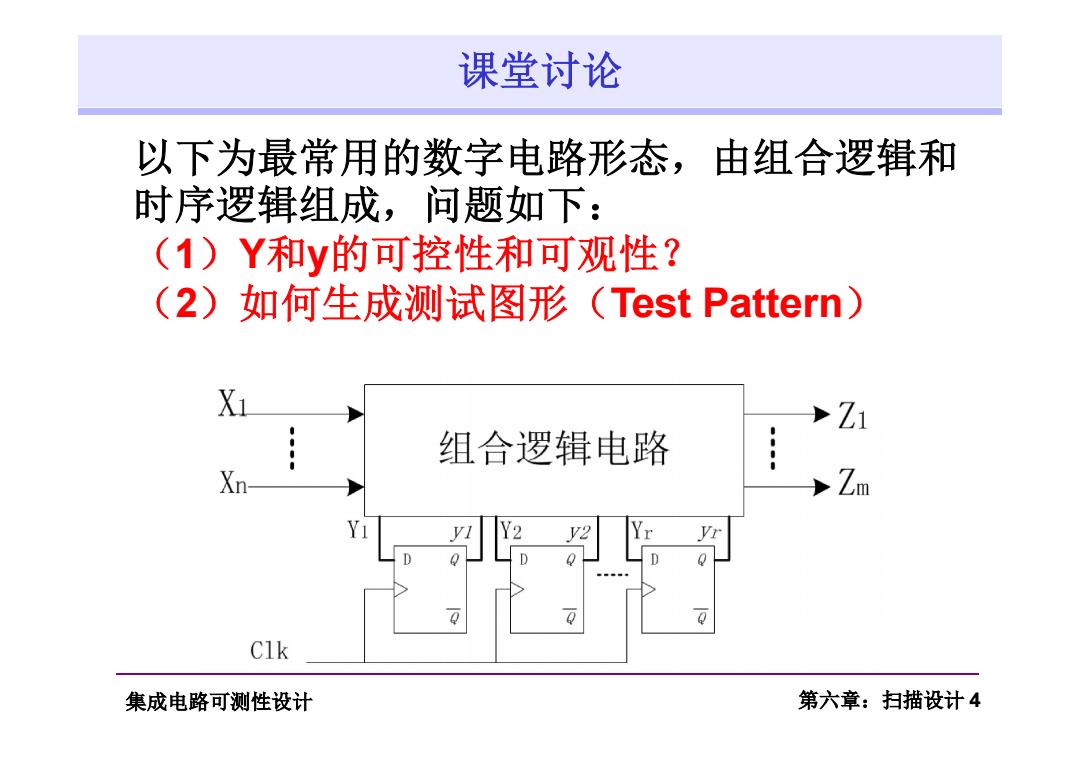

课堂讨论 以下为最常用的数字电路形态,由组合逻辑和 时序逻辑组成,问题如下: (1)Y和y的可控性和可观性? (2)如何生成测试图形(Test Pattern) Xi >Z1 组合逻辑电路 Xn Clk 集成电路可测性设计 第六章:扫描设计4

课堂讨论 集成电路可测性设计 第六章:扫描设计 4 以下为最常用的数字电路形态,由组合逻辑和 时序逻辑组成,问题如下: (1)Y和y的可控性和可观性? (2)如何生成测试图形(Test Pattern)

课堂讨论 纯组合逻辑,讨论以上两个问题 应用 PI 组合逻辑 PO 集成电路可测性设计 第六章:扫描设计5

课堂讨论 集成电路可测性设计 第六章:扫描设计 5 PI PO 组合逻辑 应用 纯组合逻辑,讨论以上两个问题

概述(1)-时序电路的主要问题 冬可控性和可观性差:触发器的输出不能由原 始输入直接控制,触发器的输入不能从原始 输出直接观察到 个原始输入的组合逻辑和个触发器的存储 电路,那么就需2个测试图形才能对其组 合逻辑部分穷举测试; 。初始化问题。 集成电路可测性设计 第六章:扫描设计6

概述(1)--时序电路的主要问题 可控性和可观性差:触发器的输出不能由原 始输入直接控制,触发器的输入不能从原始 输出直接观察到 ; n个原始输入的组合逻辑和r个触发器的存储 电路,那么就需2n+ r个测试图形才能对其组 合逻辑部分穷举测试; 初始化问题 。 集成电路可测性设计 第六章:扫描设计 6