●●● ●● ●●●● ●●● 第十一章存储器测试 子料战女学 /966 University of Electronic Science and Technology of China

2021/8/18 集成电路可测性设计 2 第十一章 存储器测试

●●● ●● ●●●● 内容提要 ●●0● ●●o● ① 概述 ② 存储器模型 ③ 失效机制和故障模型 ④ 存储器的测试算法 2021/8/18 集成电路可测性设计 3

2021/8/18 集成电路可测性设计 3 内容提要 ① 概述 ② 存储器模型 ③ 失效机制和故障模型 ④ 存储器的测试算法

●●●● 0●●●● ●●●● ●●●● ●●0● ●●0● ●● 11.1概述 2021/8/18 集成电路可测性设计 4

2021/8/18 集成电路可测性设计 4 11.1 概述

● ●● 11.1概述 ●●●● ●●● o Memories (esp.RAM)are at the forefront of commercial electronic designs DRAMs are the technology driver for the semiconductor industry Memories are the most numerous IPs used in SOC designs (hundreds and >90%of an SoC in 2010) 2021/8/18 集成电路可测性设计 5

2021/8/18 集成电路可测性设计 5 11.1 概述 Memories (esp. RAM) are at the forefront of commercial electronic designs DRAMs are the technology driver for the semiconductor industry Memories are the most numerous IPs used in SOC designs (hundreds ! and >90% of an SoC in 2010)

●● ●● 存储器的发展 ●● ●● ●● ●(1970,Intel,.DRAM,1024bits,1$/bit) ●(1997,DRAM,1st256Mbit,120X10-6$/bit) 邑 10G 1G 512M G 123nH 1O0M 5 16M ⑧ 64i 1OM 1M 4几A i几i 255k 1ook 82 36 994 02 06 Year 2021/8/18 集成电路可测性设计 6

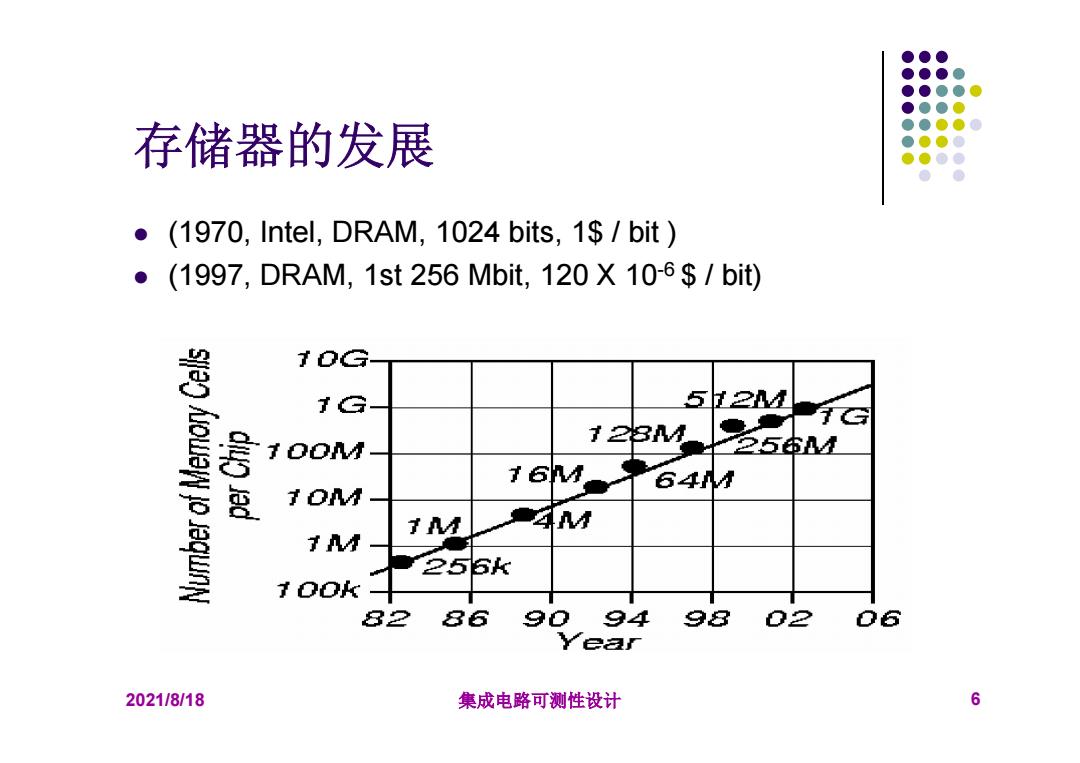

2021/8/18 集成电路可测性设计 6 (1970, Intel, DRAM, 1024 bits, 1$ / bit ) (1997, DRAM, 1st 256 Mbit, 120 X 10-6 $ / bit) 存储器的发展