形式验证方法 ·形式验证就是采用穷举的方法检查难检查的错误, 不需要测试图形或testbench。理论上讲验证速度 快、代码覆盖率为100%。形式验证的方法为理论证 明、模型检查和等效检查。 2020/9/4 集成电路可测性设计 17

2020/9/4 集成电路可测性设计 17 形式验证方法 形式验证就是采用穷举的方法检查难检查的错误, 不需要测试图形或testbench。理论上讲验证速度 快、代码覆盖率为100%。形式验证的方法为理论证 明、模型检查和等效检查

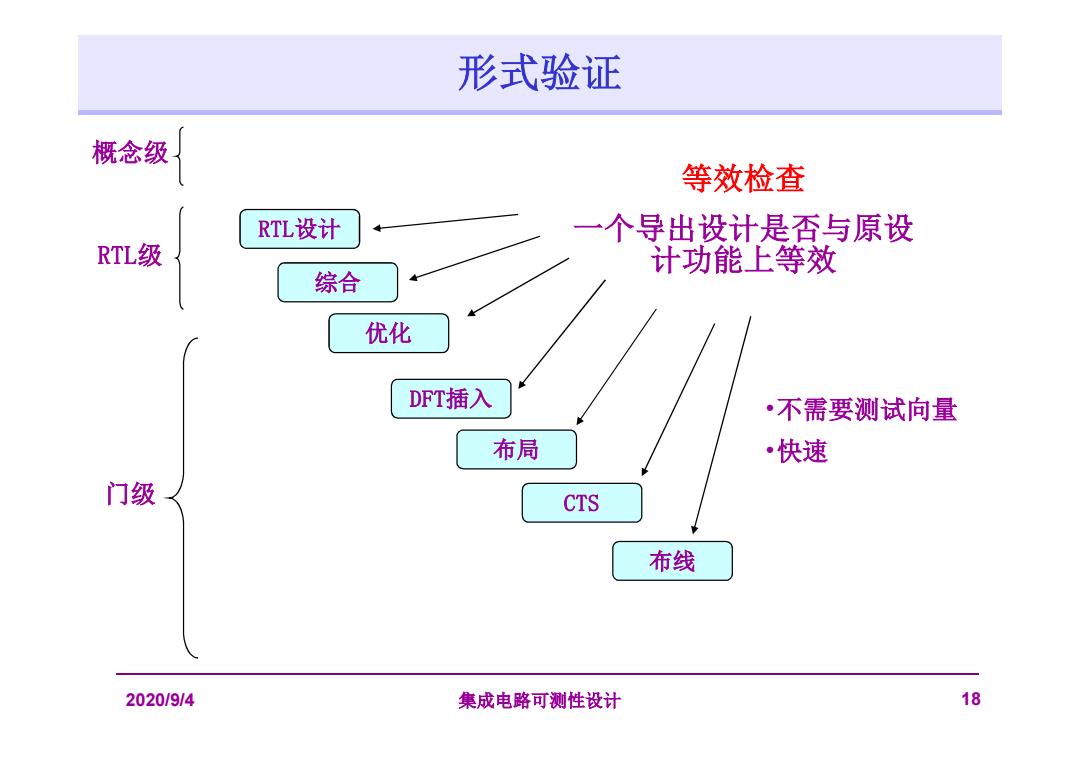

形式验证 概念级 等效检查 RTL设计 一个导出设计是否与原设 RTL级 计功能上等效 综合 优化 DFT插入 ·不需要测试向量 布局 •快速 门级 CTS 布线 2020/9/4 集成电路可测性设计 18

2020/9/4 集成电路可测性设计 18 形式验证 RTL设计 综合 优化 DFT插入 布局 CTS 布线 等效检查 一个导出设计是否与原设 计功能上等效 概念级 RTL级 门级 •不需要测试向量 •快速

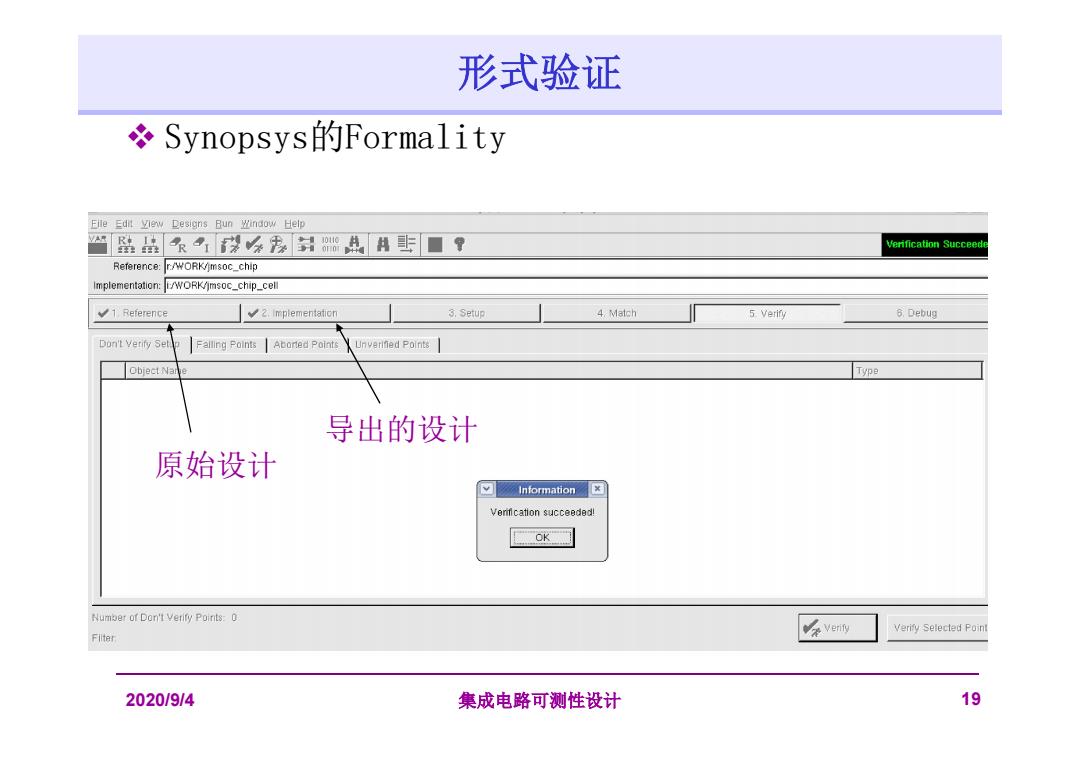

形式验证 Synopsys的Formality Eile Edlt yiew Designs Bun Window Help 四路品尔⅓封总科非☐9 Verification Succeed Reference: r/WORK/msoc_chip Implementation:/WORK/jmsoc_chip_cell 1 Reference √2.implementaticn 3.Setup 4.Match 5 Verify 6.Debug Don't Verify Set Falling Points Aborted Points Unverined Points ObjectNa Type 导出的设计 原始设计 2 Information圆x Verication succeeded! Number of Don't Verify Points:0 Verify Selected Point Fita时 2020/9/4 集成电路可测性设计 19

2020/9/4 集成电路可测性设计 19 形式验证 Synopsys的Formality 原始设计 导出的设计

物理验证和分析 ?典型的包括时序、信号完整性、串扰、IR下降、 电迁移、功耗分析、天线效应等。 2020/9/4 集成电路可测性设计 20

2020/9/4 集成电路可测性设计 20 物理验证和分析 典型的包括时序、信号完整性、串扰、IR下降、 电迁移、功耗分析、天线效应等

多种验证方法举例 版图验证(DRC&LVS) -版图验证主要是对布局布线生成的GDS进行最终的检查, 检查的规则采用的是foundry提供的专用于tape-out前检 查的规则文件。 -LVS是检查网表和版图的一致性,而且在这一阶段,LVS 会对标准单元和宏单元的电源和地的连接情况也连带检 查,而布局布线阶段的只能对单元的输入输出进行检查。 -工具 >mentor公司的calibre >Synopsys的hercules >Cadencel的dracular 2020/9/4 集成电路可测性设计 21

2020/9/4 集成电路可测性设计 21 多种验证方法举例 版图验证(DRC & LVS) 版图验证主要是对布局布线生成的GDS进行最终的检查, 检查的规则采用的是foundry提供的专用于tape-out前检 查的规则文件。 LVS是检查网表和版图的一致性,而且在这一阶段,LVS 会对标准单元和宏单元的电源和地的连接情况也连带检 查,而布局布线阶段的只能对单元的输入输出进行检查。 工具 mentor公司的calibre Synopsys的hercules Cadence的dracular