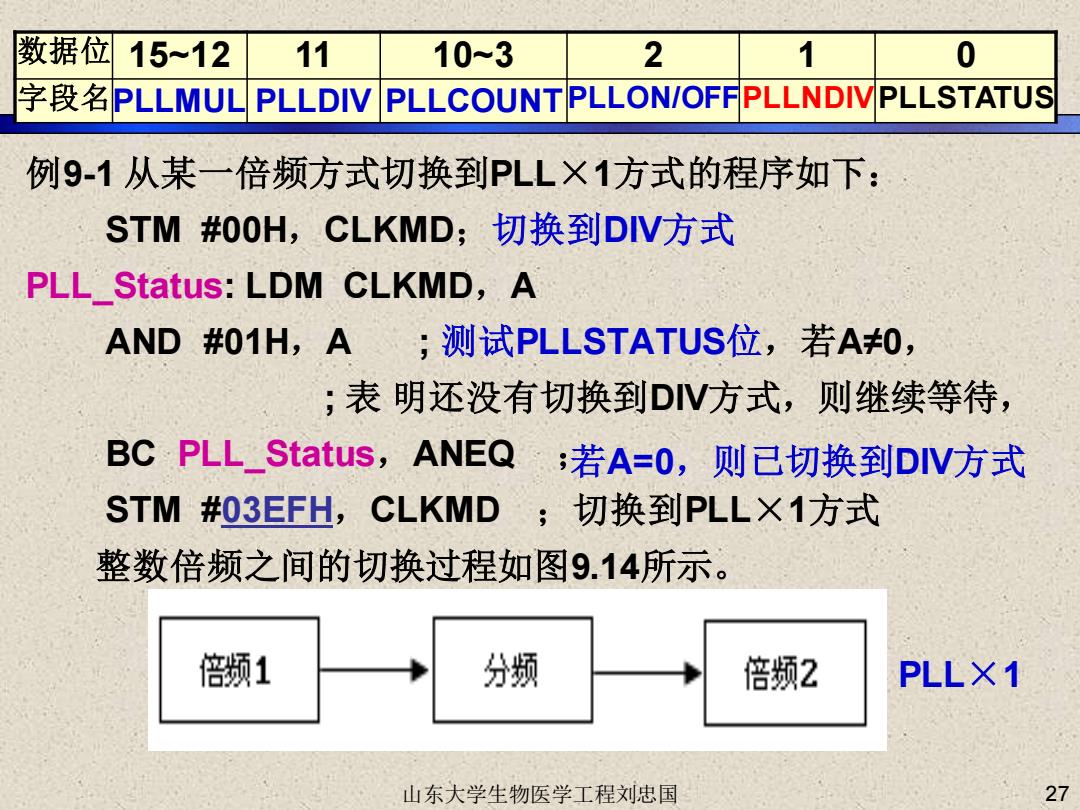

数据位15~12 11 10~3 2 1 0 字段名PLLMUL PLLDIV PLLCOUNTPLLON/OFFPLLNDIVPLLSTATUS 例9-1从某一倍频方式切换到PLL×1方式的程序如下: STM#0OH,CLKMD;切换到DIV方式 PLL Status:LDM CLKMD,A AND #01H,A 、;测试PLLSTATUS位,若A0, ;表明还没有切换到DV方式,则继续等待, BC PLL Status,ANEQ ;若A=0,则已切换到DI方式 STM#03EFH,CLKMD;切换到PLL×1方式 整数倍频之间的切换过程如图9.14所示。 倍频1 分频 倍频2 PLLX1 山东大学生物医学工程刘忠国 27

9.1.3 DSP时钟电路设计 例9-1 从某一倍频方式切换到PLL×1方式的程序如下: STM #00H,CLKMD;切换到DIV方式 PLL_Status: LDM CLKMD,A AND #01H,A ; 测试PLLSTATUS位,若A≠0, ; 表 明还没有切换到DIV方式,则继续等待, BC PLL_Status,ANEQ ; STM #03EFH,CLKMD ;切换到PLL×1方式 整数倍频之间的切换过程如图9.14所示。 27 PLL×1 若A=0,则已切换到DIV方式 山东大学生物医学工程刘忠国 数据位 15~12 11 10~3 2 1 0 字段名PLLMUL PLLDIV PLLCOUNT PLLON/OFFPLLNDIVPLLSTATUS

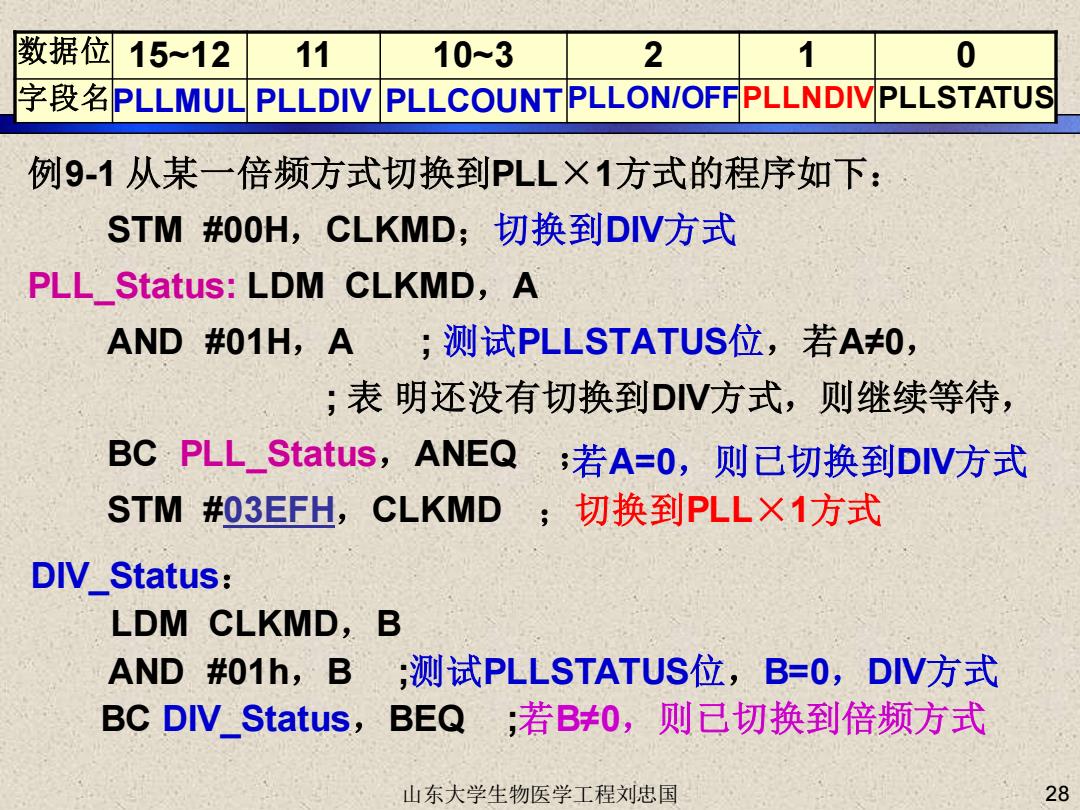

数据位15~12 11 10~3 2 1 0 字段名PLLMULPLLDIV PLLCOUNTPLLON/OFFPLLNDIVPLLSTATUS 例9-1从某一倍频方式切换到PLL×1方式的程序如下: STM#0OH,CLKMD;切换到DIV方式 PLL Status:LDM CLKMD,A AND#01H,A;测试PLLSTATUS位,若A0, ;表明还没有切换到DⅣ方式,则继续等待, BC PLL_Status,ANEQ;若A=0,则已切换到DIV方式 STM#O3EFH,CLKMD;切换到PLL×1方式 DIV Status: LDM CLKMD,B AND #01h,B ;测试PLLSTATUS位,B=O,DIV方式 BC DIV Status,BEQ;若B≠0,则已切换到倍频方式 山东大学生物医学工程刘忠国 28

9.1.3 DSP时钟电路设计 例9-1 从某一倍频方式切换到PLL×1方式的程序如下: STM #00H,CLKMD;切换到DIV方式 PLL_Status: LDM CLKMD,A AND #01H,A ; 测试PLLSTATUS位,若A≠0, ; 表 明还没有切换到DIV方式,则继续等待, BC PLL_Status,ANEQ ; STM #03EFH,CLKMD ;切换到PLL×1方式 28 若A=0,则已切换到DIV方式 DIV_Status: LDM CLKMD,B AND #01h,B ;测试PLLSTATUS位,B=0,DIV方式 BC DIV_Status,BEQ ;若B≠0,则已切换到倍频方式 山东大学生物医学工程刘忠国 数据位 15~12 11 10~3 2 1 0 字段名PLLMUL PLLDIV PLLCOUNT PLLON/OFFPLLNDIVPLLSTATUS

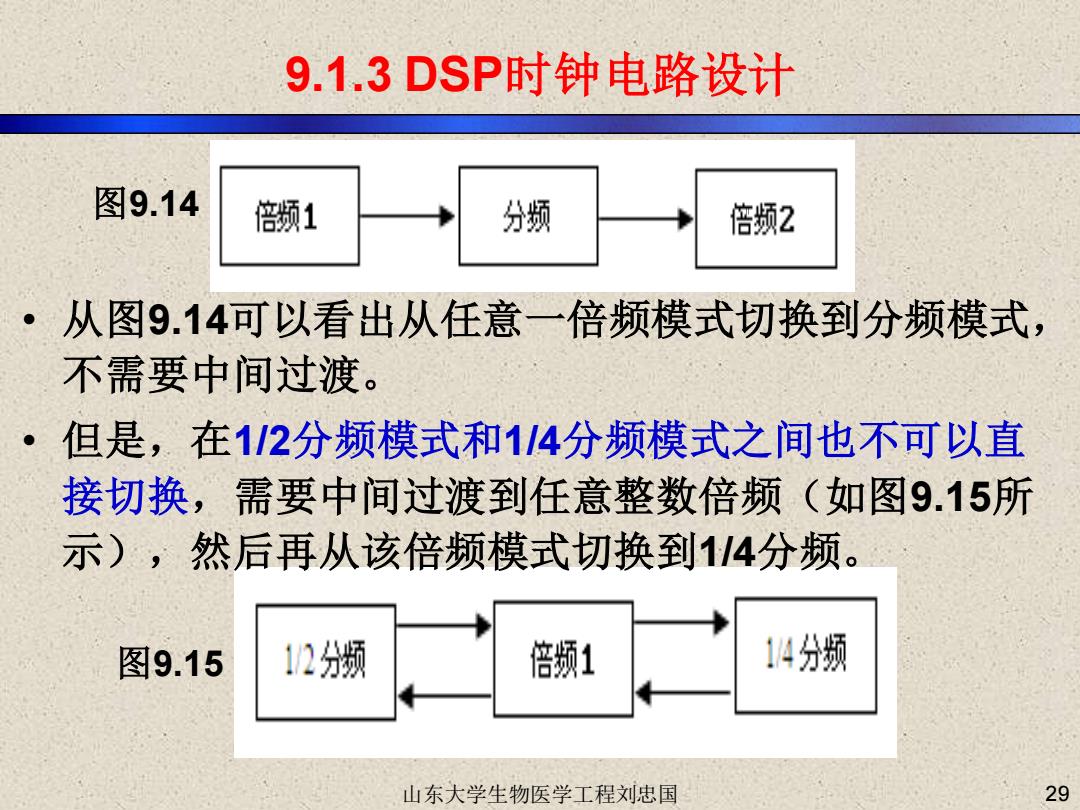

9.1.3DSP时钟电路设计 图9.14 倍频1 分频 倍频2 从图9.14可以看出从任意一倍频模式切换到分频模式, 不需要中间过渡。 ·但是,在112分频模式和114分频模式之间也不可以直 接切换,需要中间过渡到任意整数倍频(如图9.15所 示),然后再从该倍频模式切换到1/4分频。 图9.15 12分频 倍频1 14分频 山东大学生物医学工程刘忠国 29

9.1.3 DSP时钟电路设计 29 图9.14 • 从图9.14可以看出从任意一倍频模式切换到分频模式, 不需要中间过渡。 • 但是,在1/2分频模式和1/4分频模式之间也不可以直 接切换,需要中间过渡到任意整数倍频(如图9.15所 示),然后再从该倍频模式切换到1/4分频。 图9.15 山东大学生物医学工程刘忠国

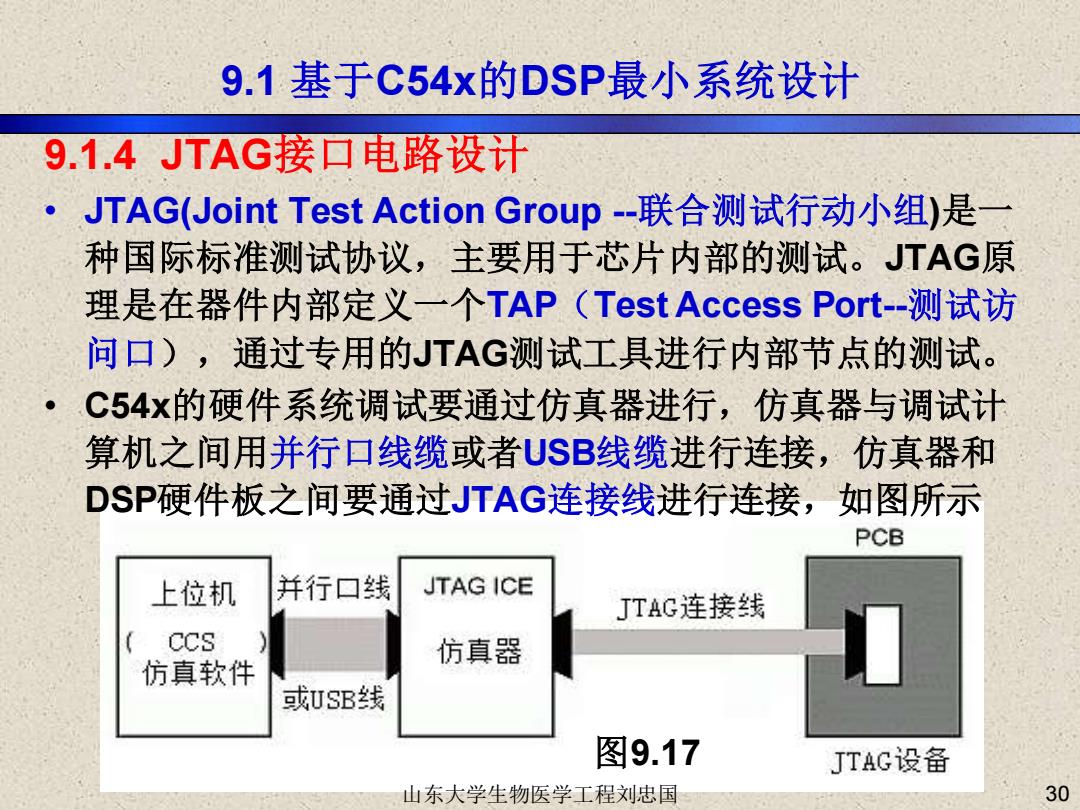

9.1基于C54x的DSP最小系统设计 9.1.4JTAG接▣电路设计 JTAG(Joint Test Action Group-联合测试行动小组)是一 种国际标准测试协议,主要用于芯片内部的测试。JTAG原 理是在器件内部定义一个TAP(Test Access Port.-测试访 问口),通过专用的JTAG测试工具进行内部节点的测试。 C54x的硬件系统调试要通过仿真器进行,仿真器与调试计 算机之间用并行口线缆或者USB线缆进行连接,仿真器和 DSP硬件板之间要通过JTAG连接线进行连接,如图所示 PCB 上位机 并行口线 JTAG ICE JTAG连接线 CCS 仿真器 仿真软件 或USB线 图9.17 JTAG设备 山东大学生物医学工程刘忠国 30

9.1 基于C54x的DSP最小系统设计 9.1.4 JTAG接口电路设计 • JTAG(Joint Test Action Group --联合测试行动小组)是一 种国际标准测试协议,主要用于芯片内部的测试。JTAG原 理是在器件内部定义一个TAP(Test Access Port--测试访 问口),通过专用的JTAG测试工具进行内部节点的测试。 • C54x的硬件系统调试要通过仿真器进行,仿真器与调试计 算机之间用并行口线缆或者USB线缆进行连接,仿真器和 DSP硬件板之间要通过JTAG连接线进行连接,如图所示 30 图9.17 山东大学生物医学工程刘忠国

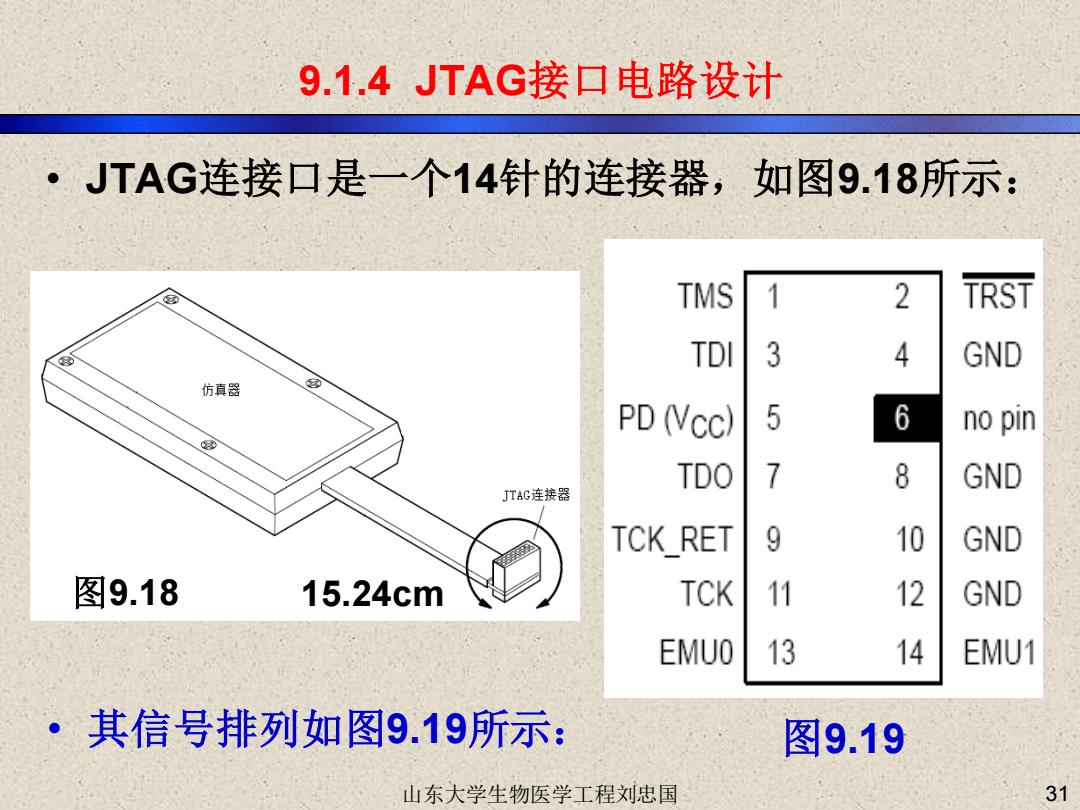

9.1.4JTAG接口电路设计 ·JTAG连接口是一个14针的连接器,如图9.18所示: TMS 1 2 TRST TDI 3 4 GND 仿真器 PD (Vcc) 5 6 no pin TDO 8 GND JTAG连接器 TCK RET 9 10 GND 图9.18 15.24cm TCK 11 12 GND EMUO 13 14 EMU1 ·其信号排列如图9.19所示: 图9.19 山东大学生物医学工程刘忠国 31

9.1.4 JTAG接口电路设计 • JTAG连接口是一个14针的连接器,如图9.18所示: 15.24cm 31 图9.18 • 其信号排列如图9.19所示: 图9.19 山东大学生物医学工程刘忠国