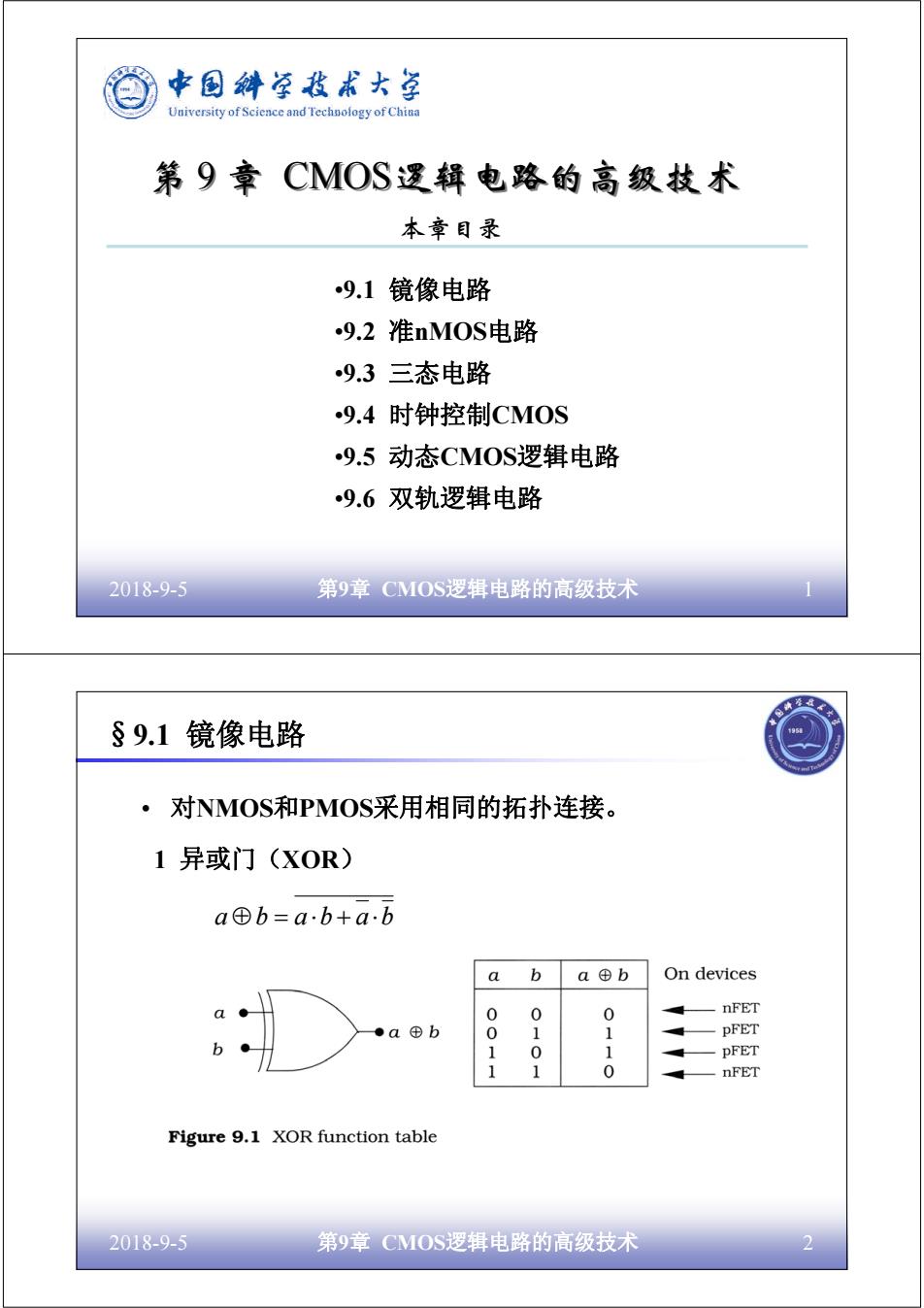

中国绅学我术大学 University of Science and Technology of China 第9章CMOS逻辑电路的高级技术 本章目录 9.1镜像电路 92准nMOS电路 9.3三态电路 9.4时钟控制CMOS 9.5动态CMOS逻辑电路 9.6双轨逻辑电路 2018-9-5 第9章CMOS逻辑电路的高级技术 §91镜像电路 ·对NMOS和PMOS采用相同的拓扑连接。 1异或门(XOR) a⊕b=a,b+a.b a b a⊕b On devices 0 0 0 一nFET ●a⊕b 0 pFET b 0 pFET 1 1 0 nFET Figure 9.1 XOR function table 2018-9-5 第9章CMOS逻辑电路的高级技术 2

2018-9-5 第9章 CMOS逻辑电路的高级技术 1 第 9 章 CMOS逻辑电路的高级技术 逻辑电路的高级技术 本章目录 •9.1 镜像电路 •9.2 准nMOS电路 •9.3 三态电路 •9.4 时钟控制CMOS •9.5 动态CMOS逻辑电路 •9.6 双轨逻辑电路 2018-9-5 第9章 CMOS逻辑电路的高级技术 2 §9.1 镜像电路 • 对NMOS和PMOS采用相同的拓扑连接。 1 异或门(XOR) a ⊕b = a ⋅b + a ⋅b

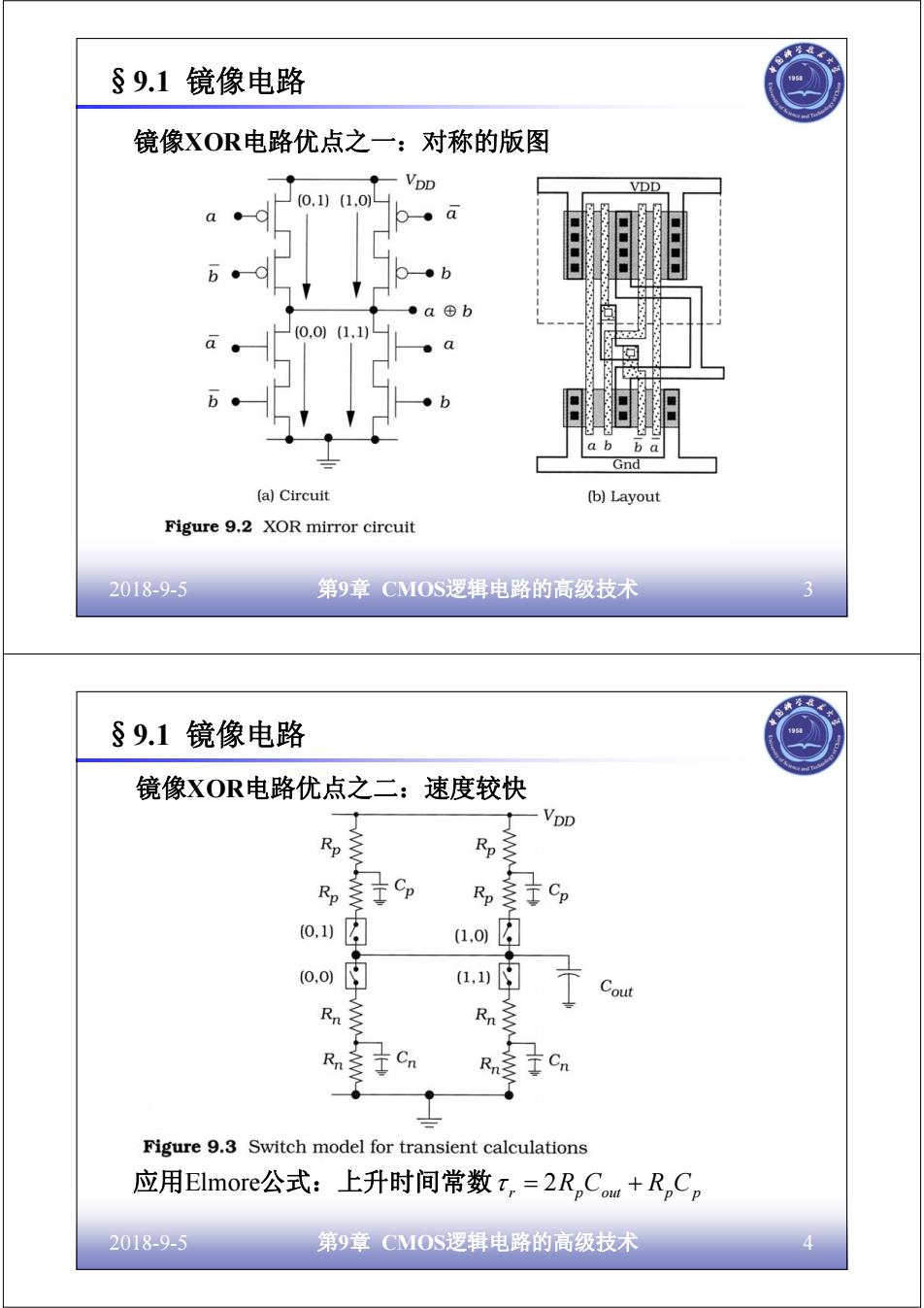

§9.1镜像电路 镜像XOR电路优点之一:对称的版图 VpD VDD 0.1)(1,04 a ●a⊕b 0.0)(1.1 a b Gnd (a)Circuit (b)Layout Figure 9.2 XOR mirror circuit 2018-9-5 第9章CMOS逻辑电路的高级技术 §9.1镜像电路 镜像XOR电路优点之二: 速度较快 VpD R 9 Rp Cp o.)的 (1.0) o,0内 1,1) Cout Rn R三 Cn Figure 9.3 Switch model for transient calculations 应用Elmore公式:上升时间常数t,=2R,Com+R,Cp 2018-9-5 第9章CMOS逻辑电路的高级技术

2018-9-5 第9章 CMOS逻辑电路的高级技术 3 §9.1 镜像电路 镜像XOR电路优点之一:对称的版图 2018-9-5 第9章 CMOS逻辑电路的高级技术 4 §9.1 镜像电路 镜像XOR电路优点之二:速度较快 Elmore r = 2RpCout + RpCp 应用 公式:上升时间常数τ

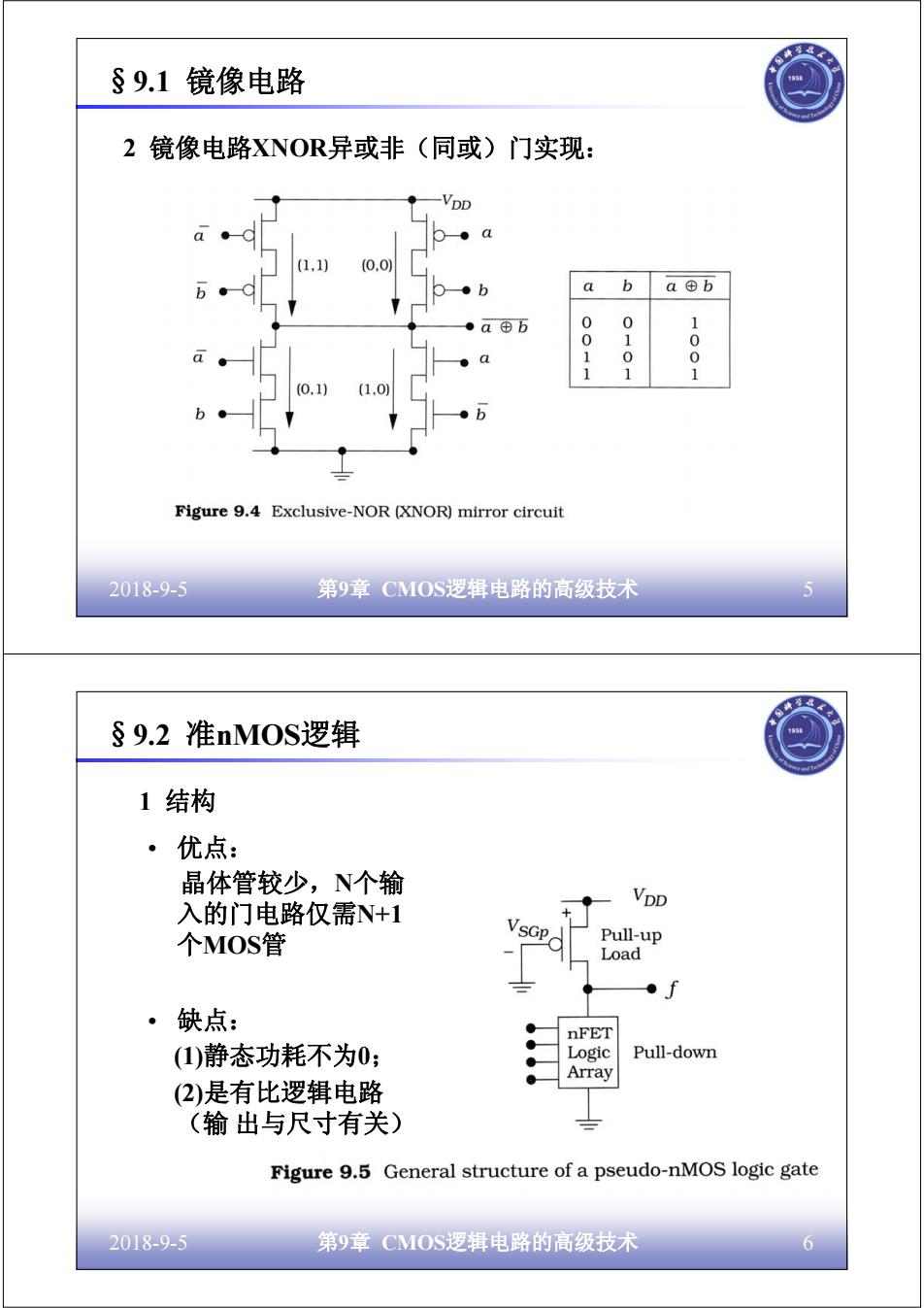

§9.1镜像电路 2镜像电路XNOR异或非(同或)门实现: VDD 1,10 (0.0 6 O●b a b a⊕b a⊕b 0 0 0 0 0 1 1 1 0,1) 1,0 Figure 9.4 Exclusive-NOR(XNOR)mirror circuit 2018-9-5 第9章CMOS逻辑电路的高级技术 §9.2准nMOS逻辑 1结构 优点: 晶体管较少,N个输 入的门电路仅需N+1 VpD 个MOS管 VSGP Pull-up Load f ·缺点: nFET (1)静态功耗不为0; ● Logic Pull-down Array (2)是有比逻辑电路 (输出与尺寸有关) Figure 9.5 General structure of a pseudo-nMOS logic gate 2018-9-5 第9章CMOS逻辑电路的高级技术

2018-9-5 第9章 CMOS逻辑电路的高级技术 5 §9.1 镜像电路 2 镜像电路XNOR异或非(同或)门实现: 2018-9-5 第9章 CMOS逻辑电路的高级技术 6 §9.2 准nMOS逻辑 1 结构 • 优点: 晶体管较少,N个输 入的门电路仅需N+1 个MOS管 • 缺点: (1)静态功耗不为0; (2)是有比逻辑电路 (输 出与尺寸有关)

§9.2准nMOS逻辑 2准nMOS逻辑INV VpD VpD B MOSFET尺寸的确定: Dp 设Vm=Voo'且Vou很小; 则pFET工作在饱和区, VOL nFET工作在线性区 Figure 9.6 Pseudo-nMOS inverter la=l→号2Wo-k.Ma-哈]-gUo-1y,2 2 sa=o-a)w--g。. 2018-9-5 第9章CMOS逻辑电路的高级技术 §9.2准nMOS逻辑 例9.1一个CMOS工艺,'oo=5V,'m=0.7V,'p=-0.8V, kn=150uA/V2,k,=68μA/W2。一个准nMOS反相器的尺寸为 (W1L)n=4及(W1L)p=6,这个反相器的输出电压为 a=w-心o-r-台o-nD B =4.3- 4.32-408x4.2=1.75V2 600 如果nMOS反相器的尺寸为(W/L)n=8及(W/L)p=2,则 'o=4.3- 4.32、 136 ×4.22=0.24V 1200 2018-9-5 第9章CMOS逻辑电路的高级技术 8

2018-9-5 第9章 CMOS逻辑电路的高级技术 7 §9.2 准nMOS逻辑 2 准nMOS逻辑 INV • MOSFET尺寸的确定: 设Vin=VDD,且VOL很小; 则pFET工作在饱和区, nFET工作在线性区 2 2 ( | |) 2 [2( ) ] 2 DD Tp p DD Tn OL OL n ⇒ V −V V −V = V − V β β 2 2 ( ) ( ) ( | |) DD Tp n p ⇒VOL = VDD −VTn − VDD −VTn − V − V β β Dn Dp I = I 2018-9-5 第9章 CMOS逻辑电路的高级技术 8 §9.2 准nMOS逻辑 及 ,这个反相器的输出电压为 。一个准 反相器的尺寸为 例 一个 工艺, ( / ) 4 ( / ) 6 150μA/V , 68μA/V nMOS 9.1 CMOS 5V, 0.7V, 0.8V, ' 2 ' 2 = = = = = = = − n p n p DD Tn Tp W L W L k k V V V 4.2 1.75V 600 408 4.3 4.3 ( ) ( ) ( | |) 2 2 2 2 = − − × = = − − − − DD − Tp n p VOL VDD VTn VDD VTn V V β β 如果nMOS反相器的尺寸为(W / L)n = 8及(W / L) p = 2,则 4.2 0.24V 1200 136 4.3 4.32 2 VOL = − − × = ?

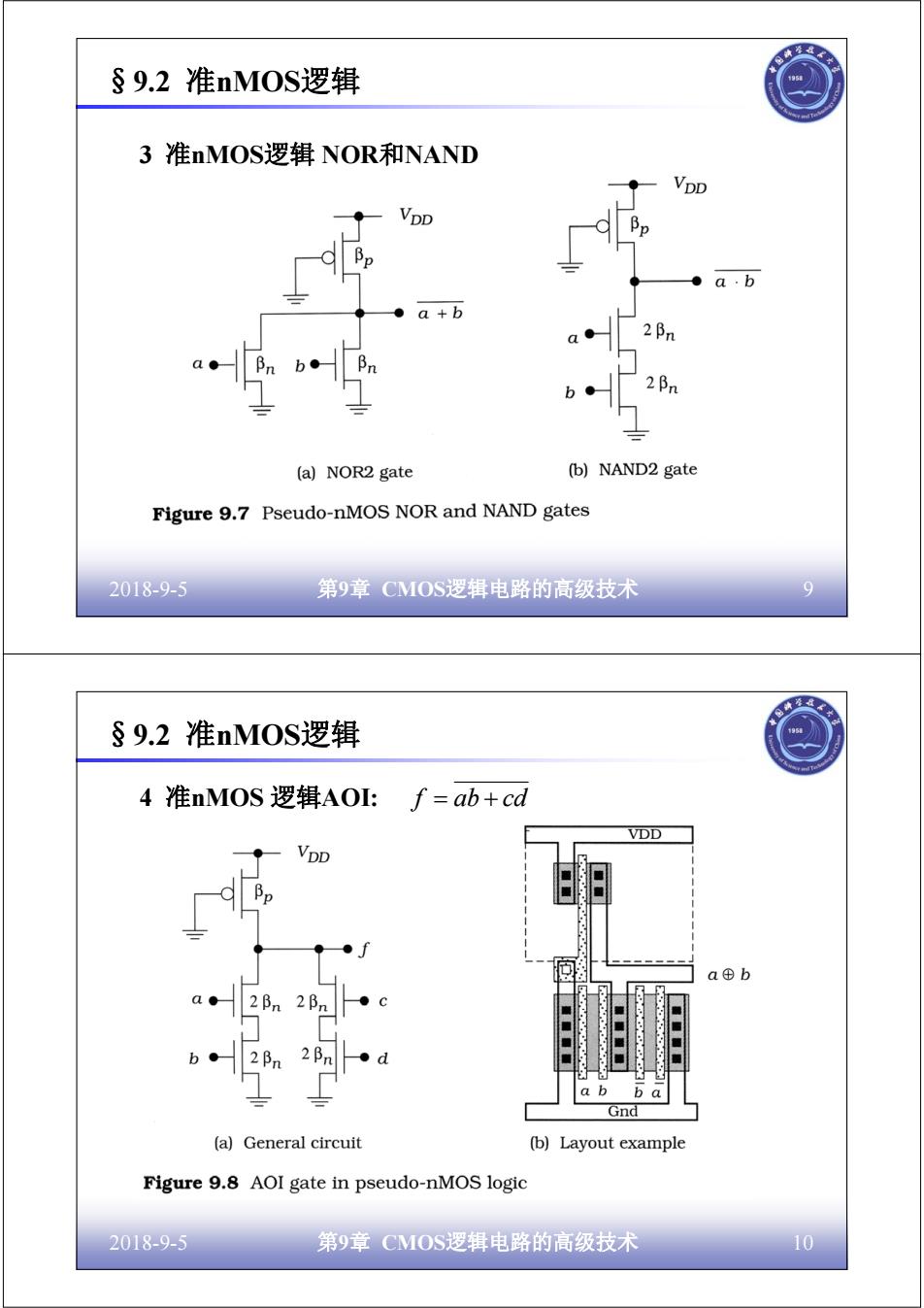

§9.2准nMOS逻辑 3准nMOS逻辑NOR和NAND VDD ●a.b ●a+b … a (a)NOR2 gate (b)NAND2 gate Figure 9.7 Pseudo-nMOS NOR and NAND gates 2018-9-5 第9章CMOS逻辑电路的高级技术 §9.2准nMOS逻辑 4准nMOS逻辑AO:f=ab+cd VDD VDD a⊕b a 2 a b b a Gnd (a)General circuit (b)Layout example Figure 9.8 AOI gate in pseudo-nMOS logic 2018-9-5 第9章CMOS逻辑电路的高级技术 10

2018-9-5 第9章 CMOS逻辑电路的高级技术 9 §9.2 准nMOS逻辑 3 准nMOS逻辑 NOR和NAND 2018-9-5 第9章 CMOS逻辑电路的高级技术 10 §9.2 准nMOS逻辑 4 准nMOS 逻辑AOI: f = ab + cd