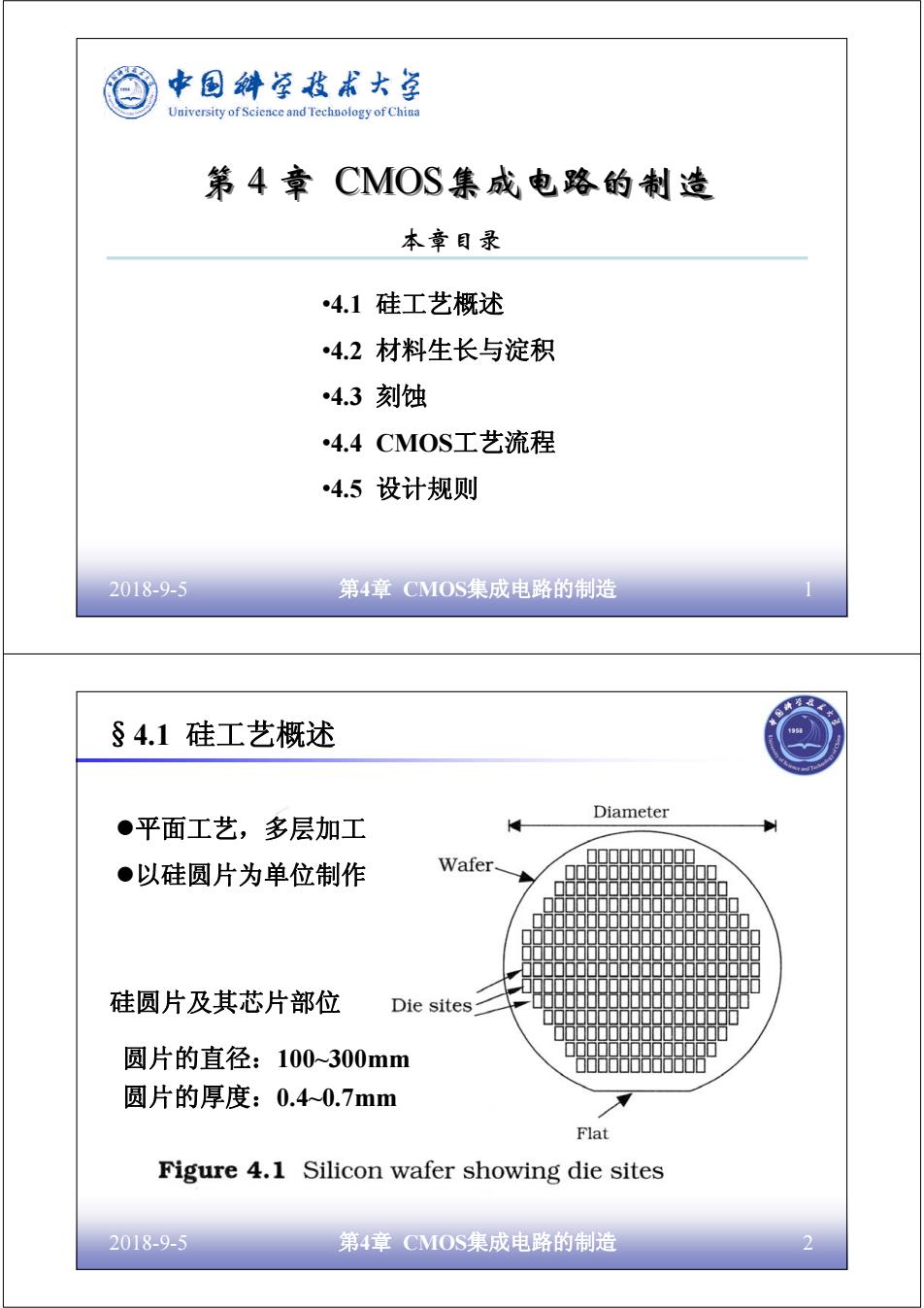

中国绅学我术大学 University of Science and Technology of China 第4章CMOS集成电路的制造 本章目录 4.1硅工艺概述 4.2材料生长与淀积 4.3刻蚀 4.4CMOS工艺流程 4.5设计规则 2018-9-5 第4章CMOS集成电路的制造 §4.1硅工艺概述 ●平面工艺,多层加工 Diameter ●以硅圆片为单位制作 Wafer- 硅圆片及其芯片部位 Die sites 圆片的直径:100-300mm 圆片的厚度:0.40.7mm Flat Figure 4.1 Silicon wafer showing die sites 2018-9-5 第4章CMOS集成电路的制造 2

2018-9-5 第4章 CMOS集成电路的制造 1 第 4 章 CMOS集成电路的制造 集成电路的制造 本章目录 •4.1 硅工艺概述 •4.2 材料生长与淀积 •4.3 刻蚀 •4.4 CMOS工艺流程 •4.5 设计规则 2018-9-5 第4章 CMOS集成电路的制造 2 §4.1 硅工艺概述 硅圆片及其芯片部位 圆片的直径:100~300mm 圆片的厚度:0.4~0.7mm z平面工艺,多层加工 z以硅圆片为单位制作

§4.1硅工艺概述 ●集成电路成本 (1)固定成本 固定成本与销售量无关。包括基础设施和生产设备的建设费用; 研发费用;人工费用等。 (2)可变成本 可变成本是指直接用于制造产品的费用,与产品的产量成正比。 可变成本=芯片成本+芯片测试成本+芯片封装成本 最终测试的成品率 每个集成电路的成本=每个集成电路的可变成本+ 固定成本 产量 经济学观点:提高成品率将降低每个集成电路的成本,因此成 品率分析很重要。 2018-9-5 第4章CMOS集成电路的制造 §4.1硅工艺概述 19 ●成品率Y Y= Na×100% N。:功能正确的芯片数目 Ni N:芯片的总数目 π(d/2)2 πd Ac:芯片面积 Adie Ade d:圆片直径 Y=(1+ D×Aae)a D:缺陷密度,单位:cm2 :与制造工艺复杂性相关的参数 对于现代复杂的CMOS工艺,a≈3 芯片成本= 圆片成本 三芯片成本=f(芯片面积) NG 2018-9-5 第4章CMOS集成电路的制造

2018-9-5 第4章 CMOS集成电路的制造 3 §4.1 硅工艺概述 z集成电路成本 最终测试的成品率 芯片成本 芯片测试成本 芯片封装成本 可变成本 + + = 产量 固定成本 每个集成电路的成本 = 每个集成电路的可变成 本 + (1)固定成本 固定成本与销售量无关。包括基础设施和生产设备的建设费用; 研发费用;人工费用等。 (2)可变成本 可变成本是指直接用于制造产品的费用,与产品的产量成正比。 经济学观点:提高成品率将降低每个集成电路的成本,因此成 品率分析很重要。 2018-9-5 第4章 CMOS集成电路的制造 4 §4.1 硅工艺概述 z成品率Y = ×100% T G N N Y die die T A d A d N 2 ( 2 2 π π = − ) α α × − = (1+ ) D Adie Y NG 圆片成本 芯片成本 = :芯片的总数目 :功能正确的芯片数目 T G N N :圆片直径 :芯片面积 d Adie CMOS 3 cm 2 ≈ − α α 对于现代复杂的 工艺, :与制造工艺复杂性相关的参数 D:缺陷密度,单位: 4 ⇒ 芯片成本 = f (芯片面积)

§4.1硅工艺概述 © ●集成电路加工的基本操作 >形成某种材料的薄膜 >在各种薄膜材料上形成需要的图形 >通过掺杂改变材料的电阻率或杂质类型 2018-9-5 第4章CMOS集成电路的制造 §4.2材料生长与淀积 形成薄膜的方法 ◆热氧化 ◆物理气相淀积(PVD) ◆化学气相淀积(CVD) §4.2.1二氧化硅 Si0,称为石英玻璃,电阻率约为10122cm 。 Si02是一种极好的电绝缘体 SiO,能很好地附着在大多数材料上 SO,可生长在硅圆片上或淀积在硅圆片上面 2018-9-5 第4章CMOS集成电路的制造 6

2018-9-5 第4章 CMOS集成电路的制造 5 §4.1 硅工艺概述 z集成电路加工的基本操作 ¾形成某种材料的薄膜 ¾在各种薄膜材料上形成需要的图形 ¾通过掺杂改变材料的电阻率或杂质类型 2018-9-5 第4章 CMOS集成电路的制造 6 • SiO2称为石英玻璃,电阻率约为1012Ω·cm • SiO2是一种极好的电绝缘体 • SiO2能很好地附着在大多数材料上 • SiO2可生长在硅圆片上或淀积在硅圆片上面 §4.2.1 二氧化硅 §4.2 材料生长与淀积 形成薄膜的方法 热氧化 物理气相淀积(PVD) 化学气相淀积(CVD)

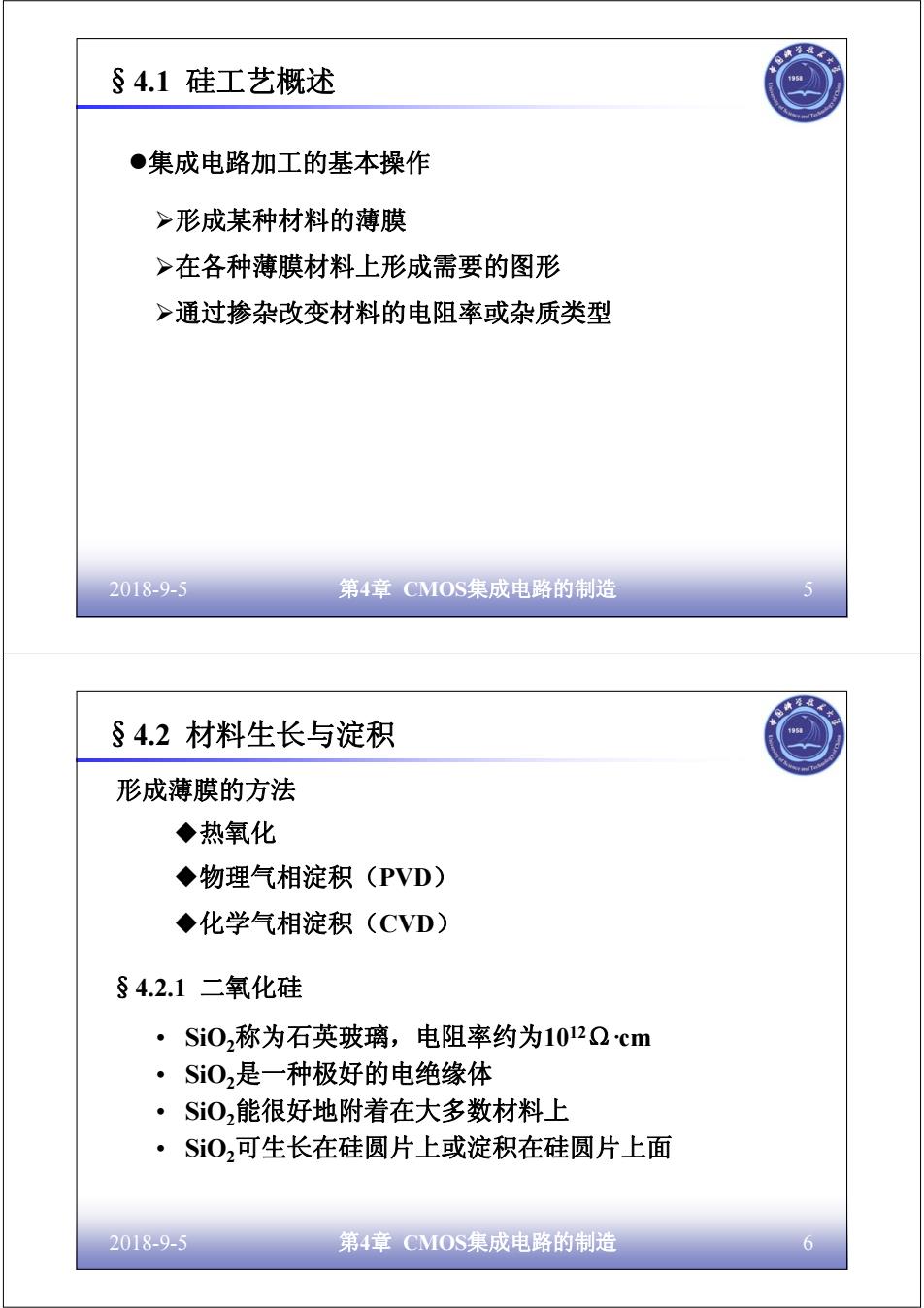

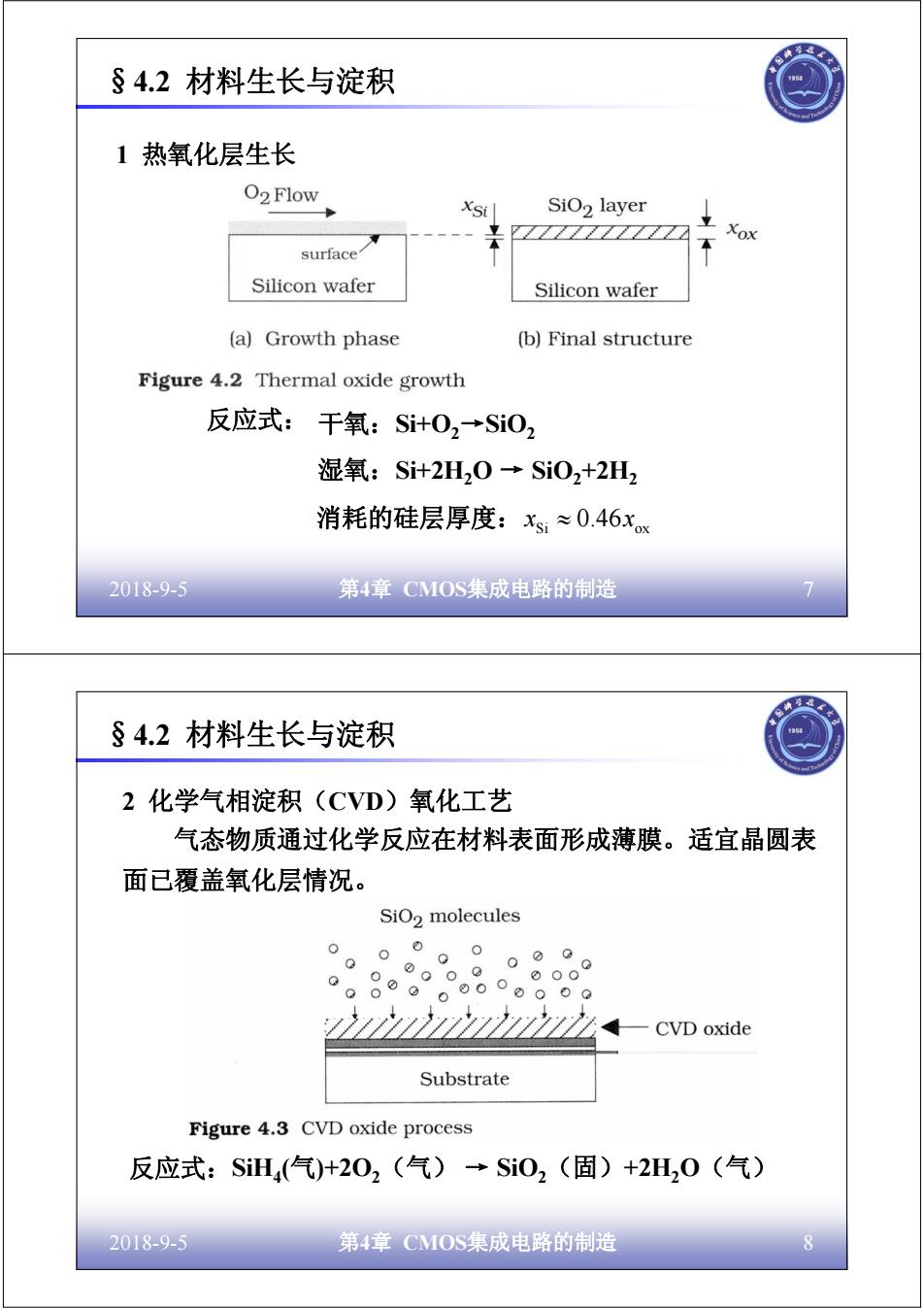

§4.2材料生长与淀积 1热氧化层生长 O2 Flow xsi SiO2 layer LVVV77777777☑ Xox surface Silicon wafer Silicon wafer (a)Growth phase (b)Final structure Figure 4.2 Thermal oxide growth 反应式:干氧:Sit02→Si02 湿氧:Si+2H20→Si02+2H2 消耗的硅层厚度:xs≈0.46x 2018-9-5 第4章CMOS集成电路的制造 §4.2材料生长与淀积 2化学气相淀积(CVD)氧化工艺 气态物质通过化学反应在材料表面形成薄膜。适宜晶圆表 面已覆盖氧化层情况。 SiO2 molecules 。0。g08a 2.0。a00000000 CVD oxide Substrate Figure 4.3 CVD oxide process 反应式:SiH(气)+202(气)→Si02(固)+2H,0(气) 2018-9-5 第4章CMOS集成电路的制造 8

2018-9-5 第4章 CMOS集成电路的制造 7 干氧:Si+O2→SiO2 湿氧:Si+2H2O → SiO2+2H2 1 热氧化层生长 §4.2 材料生长与淀积 反应式: Si ox 消耗的硅层厚度:x ≈ 0.46x 2018-9-5 第4章 CMOS集成电路的制造 8 SiH4(气)+2O2(气) → SiO2(固)+2H2O(气) 2 化学气相淀积(CVD)氧化工艺 气态物质通过化学反应在材料表面形成薄膜。适宜晶圆表 面已覆盖氧化层情况。 §4.2 材料生长与淀积 反应式:

§4.2材料生长与淀积 §4.2.2氮化硅 ·用于表面覆盖,对大多数物质原子有阻挡作用,防污染 介电常数较大:6w≈7.8&。 制造过程中用来在电气上隔离相邻场效应管 同$0,一样,能被化学漂洗掉 反应式: 3SiH4(气)+4NH(气)→SiN4(固)+12H(气) 2018-9-5 第4章CMOS集成电路的制造 §4.2材料生长与淀积 §4.2.3 多晶硅 多晶硅:Poy层,形成栅极 在SiO,上淀积硅原子,形成多晶(局部小区域Si原子规则 排列) 反应式:SiH4→Sit2H, Poy优点: •可被掺杂,增强导电性 与SiO2良好接合 ·可覆盖高熔点金属,如钛(T)、铂(Pt)、钨(W)、 钴(C0),降低薄层电阻 2018-9-5 第4章CMOS集成电路的制造 10

2018-9-5 第4章 CMOS集成电路的制造 9 3SiH4(气)+4NH3(气) → Si3N4(固)+12H2(气) §4.2 材料生长与淀积 §4.2.2 氮化硅 • 用于表面覆盖,对大多数物质原子有阻挡作用,防污染 • 介电常数较大: • 制造过程中用来在电气上隔离相邻场效应管 • 同SiO2一样,能被化学漂洗掉 0 ε ≈ 7.8ε N 反应式: 2018-9-5 第4章 CMOS集成电路的制造 10 多晶硅:Poly层,形成栅极 SiH4 → Si+2H2 §4.2.3 多晶硅 §4.2 材料生长与淀积 反应式: •可被掺杂,增强导电性 •与SiO2良好接合 •可覆盖高熔点金属,如钛(Ti)、铂(Pt)、钨(W)、 钴(Co),降低薄层电阻 Poly优点: 在SiO2上淀积硅原子,形成多晶(局部小区域Si原子规则 排列)