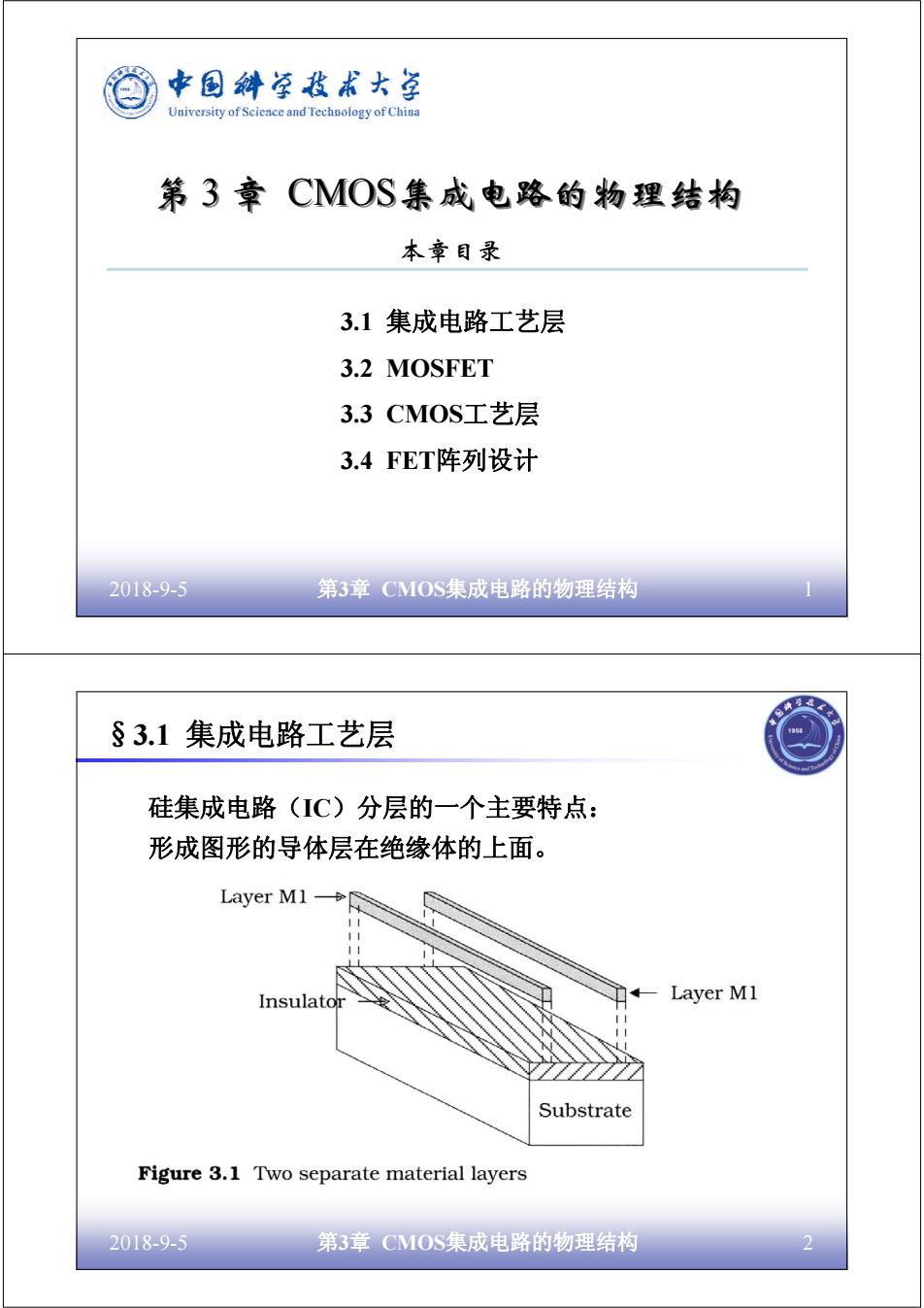

中国绅字我术大学 University of Science and Technology of China 第3章CMOS集成电路的物理结构 本章目录 3.1集成电路工艺层 3.2 MOSFET 3.3CMOS工艺层 3.4FET阵列设计 2018-9-5 第3章CMOS集成电路的物理结构 §3.1集成电路工艺层 硅集成电路(C)分层的一个主要特点: 形成图形的导体层在绝缘体的上面。 Layer M1- Insulator Layer M1 Substrate Figure 3.1 Two separate material layers 2018-9-5 第3章CMOS集成电路的物理结构

2018-9-5 第3章 CMOS集成电路的物理结构 1 第 3 章 CMOS集成电路的物理结构 集成电路的物理结构 本章目录 3.1 集成电路工艺层 3.2 MOSFET 3.3 CMOS工艺层 3.4 FET阵列设计 2018-9-5 第3章 CMOS集成电路的物理结构 2 §3.1 集成电路工艺层 硅集成电路(IC)分层的一个主要特点: 形成图形的导体层在绝缘体的上面

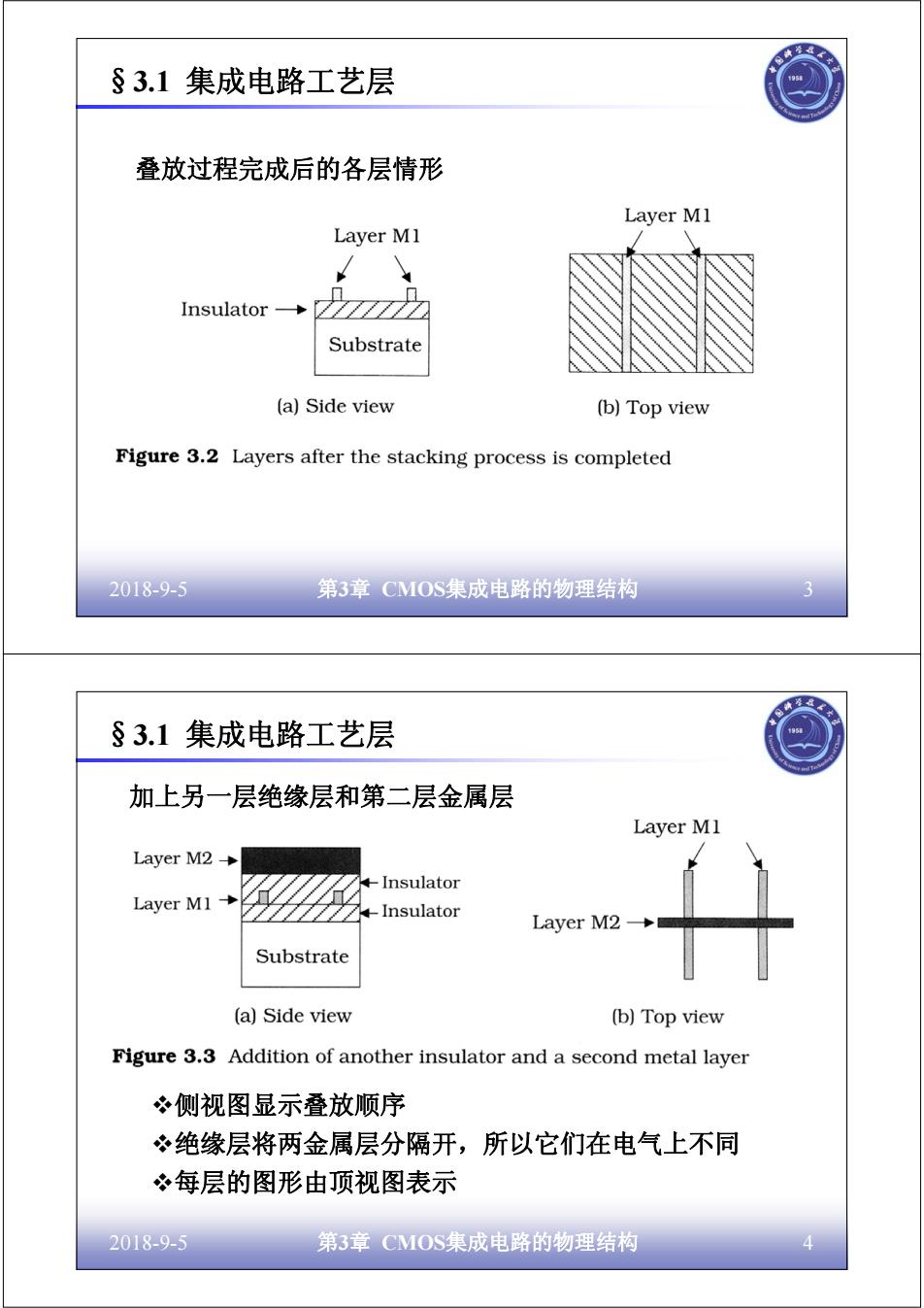

§3.1集成电路工艺层 叠放过程完成后的各层情形 Layer MI Layer MI Insulator+☑777 Substrate (a)Side view (b)Top view Figure 3.2 Layers after the stacking process is completed 2018-9-5 第3章CMOS集成电路的物理结构 §3.1集成电路工艺层 加上另一层绝缘层和第二层金属层 Layer MI Layer M2 +Insulator Layer MI Insulator Layer M2→■ Substrate (a)Side view (b)Top view Figure 3.3 Addition of another insulator and a second metal layer ?侧视图显示叠放顺序 冬绝缘层将两金属层分隔开,所以它们在电气上不同 冬每层的图形由顶视图表示 2018-9-5 第3章CMOS集成电路的物理结构

2018-9-5 第3章 CMOS集成电路的物理结构 3 叠放过程完成后的各层情形 §3.1 集成电路工艺层 2018-9-5 第3章 CMOS集成电路的物理结构 4 §3.1 集成电路工艺层 加上另一层绝缘层和第二层金属层 侧视图显示叠放顺序 绝缘层将两金属层分隔开,所以它们在电气上不同 每层的图形由顶视图表示

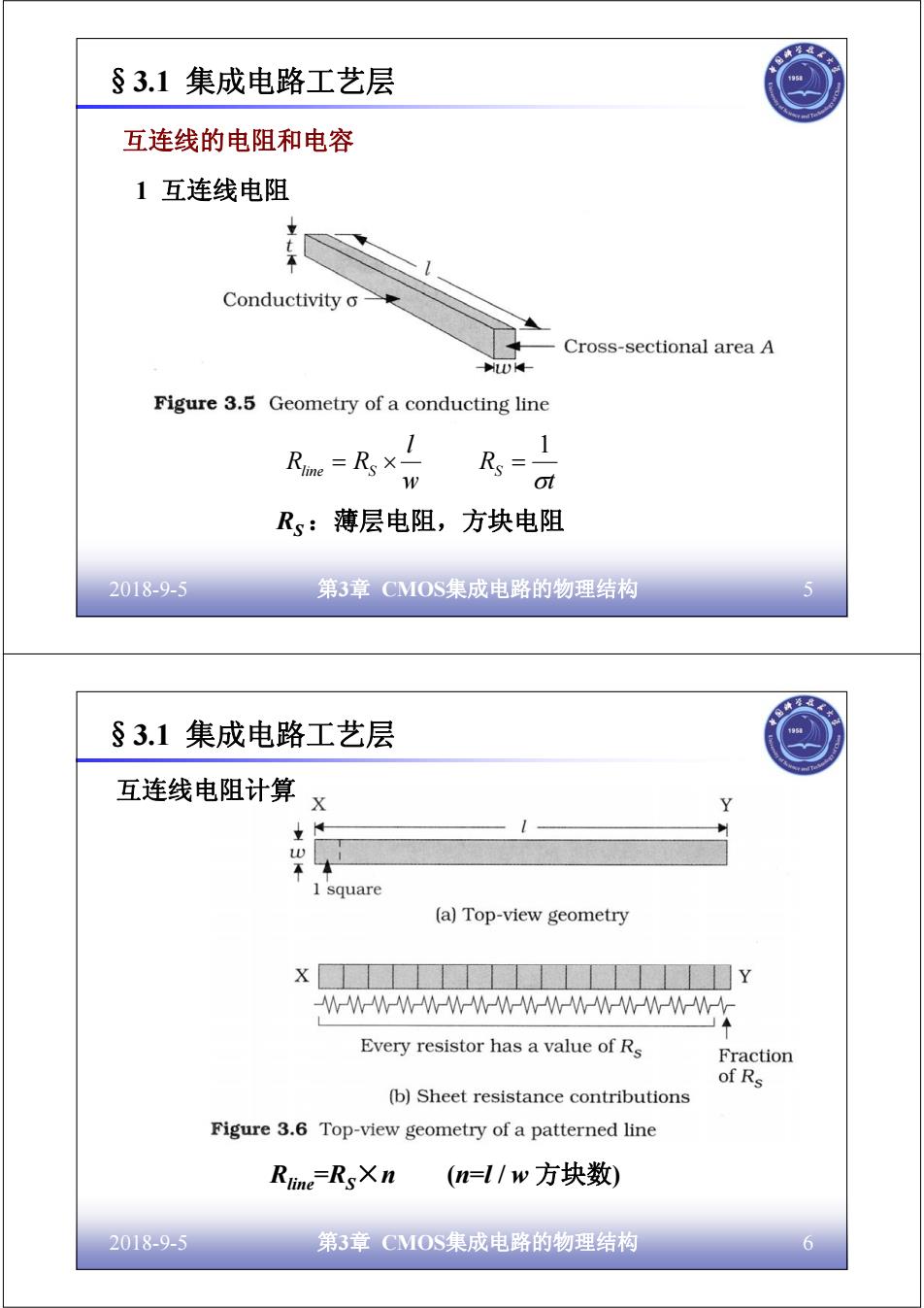

§3.1集成电路工艺层 互连线的电阻和电容 1互连线电阻 Conductivity o Cross-sectional area A WK- Figure 3.5 Geometry of a conducting line Rime =Rs x W ,- ot R:薄层电阻,方块电阻 2018-9-5 第3章CMOS集成电路的物理结构 §3.1集成电路工艺层 互连线电阻计算 X 1 square (a)Top-view geometry Y w-W-w----- Every resistor has a value of Rs Fraction of Rs (b)Sheet resistance contributions Figure 3.6 Top-view geometry of a patterned line Riine-RsXn (n=l/w方块数) 2018-9-5 第3章CMOS集成电路的物理结构 6

2018-9-5 第3章 CMOS集成电路的物理结构 5 §3.1 集成电路工艺层 互连线的电阻和电容 1 互连线电阻 w l Rline = RS × RS :薄层电阻,方块电阻 t RS σ 1 = 2018-9-5 第3章 CMOS集成电路的物理结构 6 §3.1 集成电路工艺层 互连线电阻计算 Rline=RS×n (n=l / w 方块数)

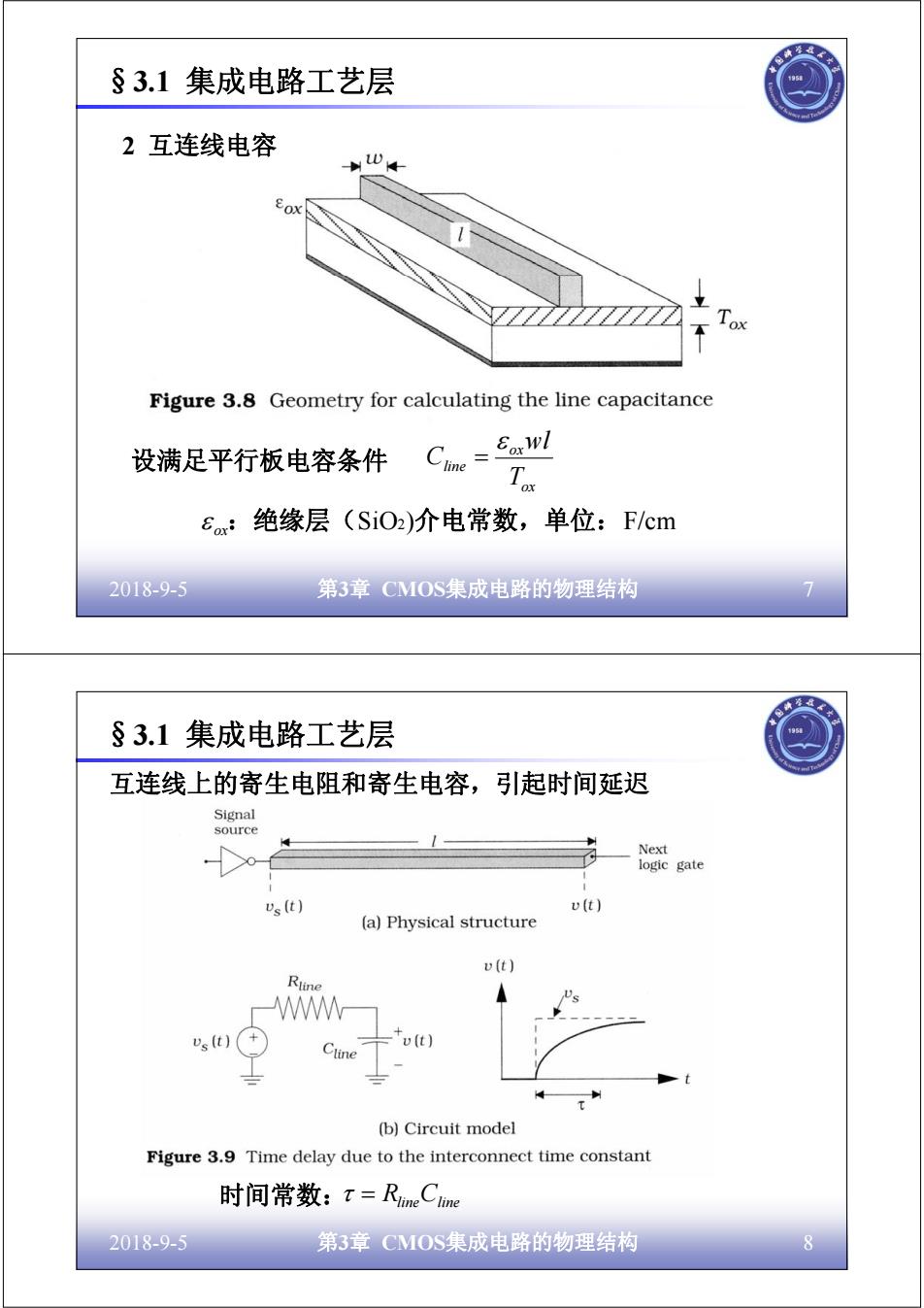

§3.1集成电路工艺层 2互连线电容 EOX o Figure 3.8 Geometry for calculating the line capacitance 设满足平行板电容条件 Ciae-£aswl &:绝缘层(SiO2)介电常数,单位:F/cm 2018-9-5 第3章CMOS集成电路的物理结构 §3.1集成电路工艺层 互连线上的寄生电阻和寄生电容,引起时间延迟 Signal source Next ● logic gate 's(t) v(t) (a)Physical structure v(t) vs(t) "v(t) (b)Circuit model Figure 3.9 Time delay due to the interconnect time constant 时间常数:T=RimneCuine 2018-9-5 第3章CMOS集成电路的物理结构 8

2018-9-5 第3章 CMOS集成电路的物理结构 7 §3.1 集成电路工艺层 2 互连线电容 设满足平行板电容条件 ox ox line T wl C ε = ε ox:绝缘层(SiO2)介电常数,单位:F/cm 2018-9-5 第3章 CMOS集成电路的物理结构 8 §3.1 集成电路工艺层 互连线上的寄生电阻和寄生电容,引起时间延迟 时间常数: = RlineCline τ

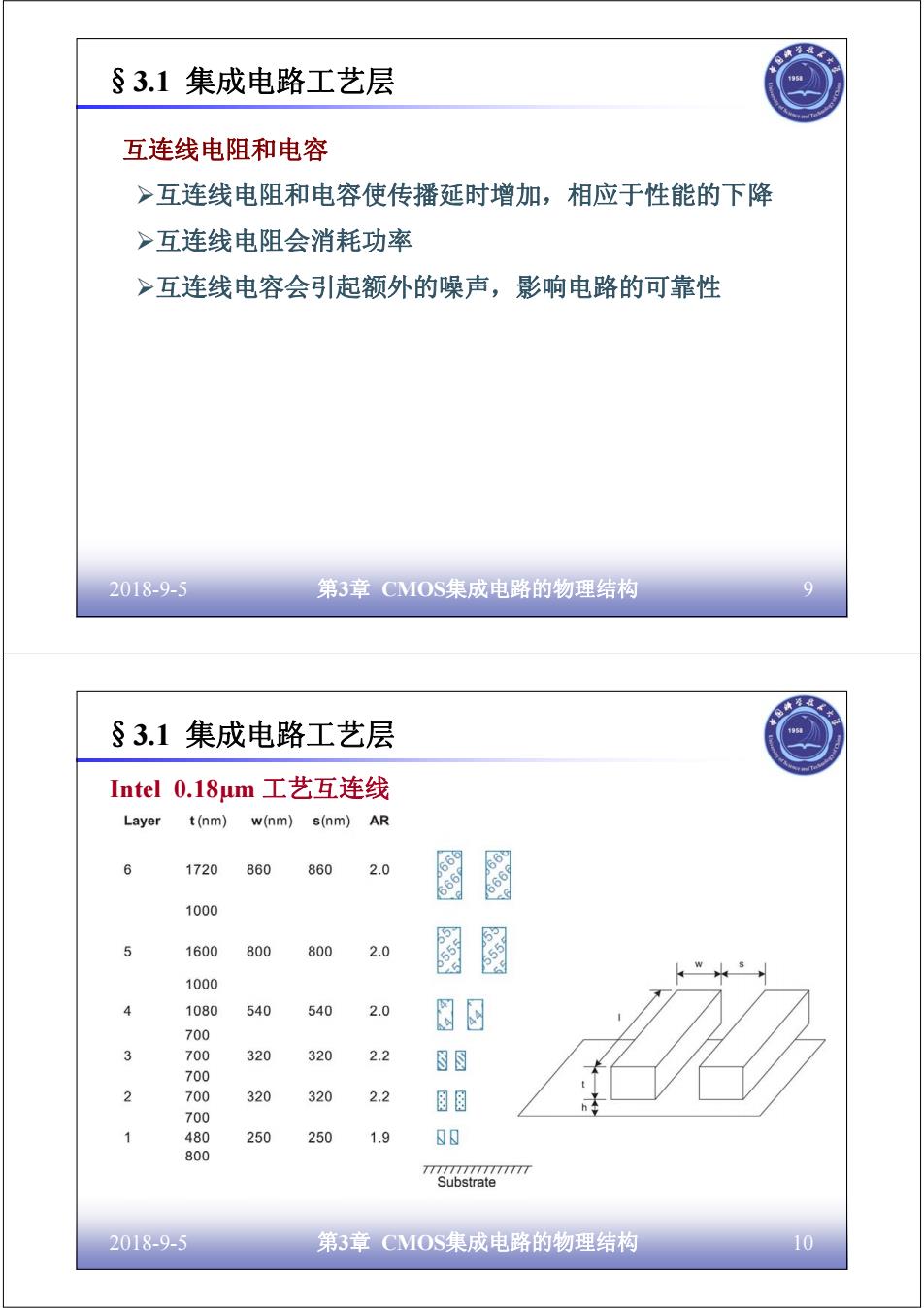

§3.1集成电路工艺层 互连线电阻和电容 >互连线电阻和电容使传播延时增加,相应于性能的下降 >互连线电阻会消耗功率 >互连线电容会引起额外的噪声,影响电路的可靠性 2018-9-5 第3章CMOS集成电路的物理结构 §3.1集成电路工艺层 Intel0.18um工艺互连线 Layer t(nm) w(nm) s(nm)AR 6 1720 860 860 2.0 1000 5 1600 800 800 2.0 1000 1080 540 540 2.0 图 700 3 700 320 320 2.2 图因 700 700 320 320 2.2 图因 700 480 250 250 1.9 g 800 Substrate 2018-9-5 第3章CMOS集成电路的物理结构 10

2018-9-5 第3章 CMOS集成电路的物理结构 9 §3.1 集成电路工艺层 ¾互连线电阻和电容使传播延时增加,相应于性能的下降 ¾互连线电阻会消耗功率 ¾互连线电容会引起额外的噪声,影响电路的可靠性 互连线电阻和电容 2018-9-5 第3章 CMOS集成电路的物理结构 10 §3.1 集成电路工艺层 Intel 0.18µm 工艺互连线