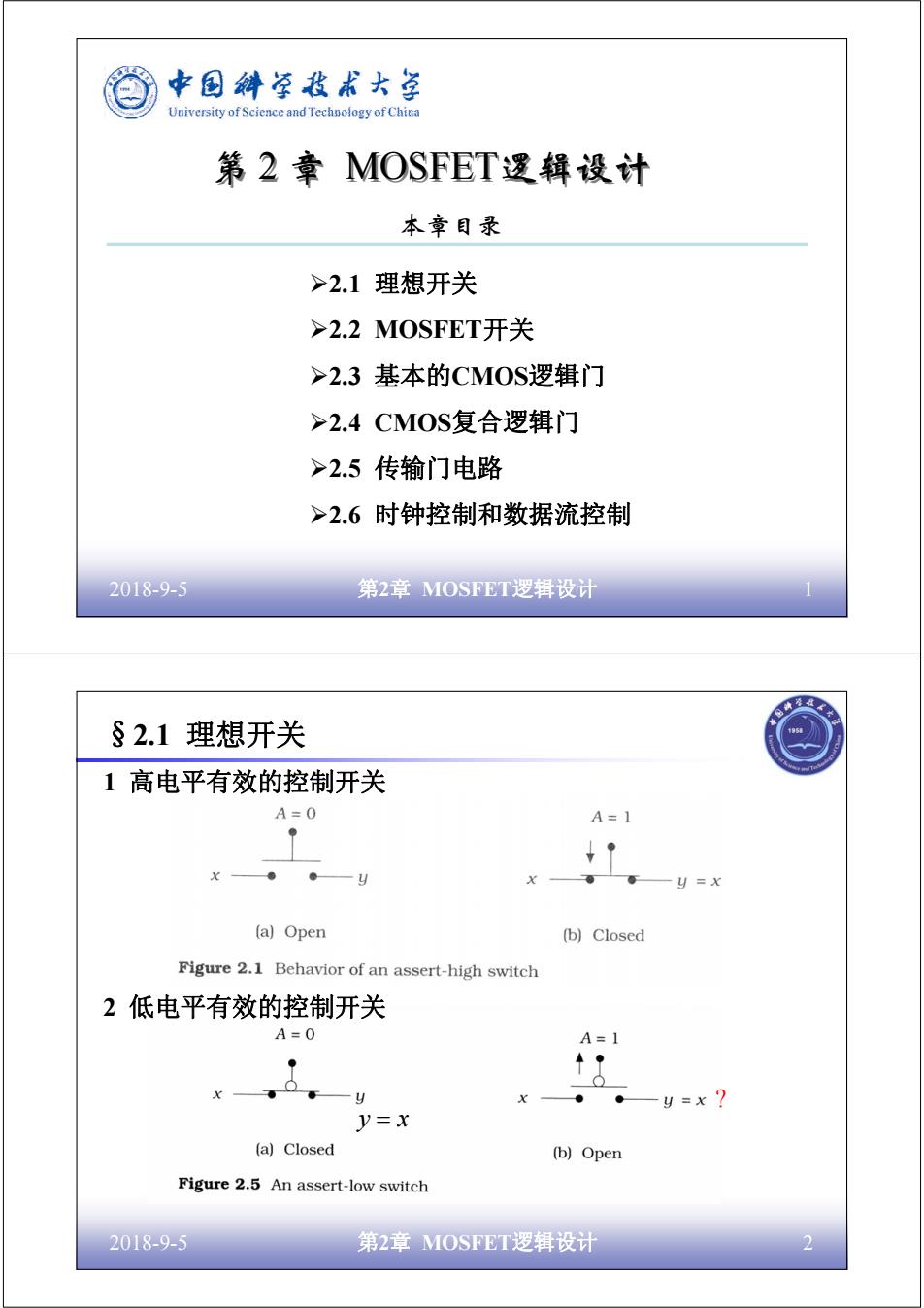

中国绅学我术大学 University of Science and Technology of China 第2章MOSFET逻辑设计 本章目录 >2.1理想开关 >2.2 MOSFET开关 >2.3基本的CMOS逻辑门 >2.4CM0S复合逻辑门 >2.5传输门电路 >2.6时钟控制和数据流控制 2018-9-5 第2章MOSFET:逻辑设计 §2.1理想开关 1高电平有效的控制开关 A=0 A=1 —y=x (a)Open (b)Closed Figure 2.1 Behavior of an assert-high switch 2低电平有效的控制开关 A=0 A=1 ↑ x。。—y=x? y=x (a)Closed (b)Open Figure 2.5 An assert-low switch 2018-9-5 第2章MOSFET:逻辑设计 2

2018-9-5 第2章 MOSFET逻辑设计 1 第 2 章 MOSFET逻辑设计 本章目录 ¾2.1 理想开关 ¾2.2 MOSFET开关 ¾2.3 基本的CMOS逻辑门 ¾2.4 CMOS复合逻辑门 ¾2.5 传输门电路 ¾2.6 时钟控制和数据流控制 2018-9-5 第2章 MOSFET逻辑设计 2 §2.1 理想开关 1 高电平有效的控制开关 2 低电平有效的控制开关 y = x ?

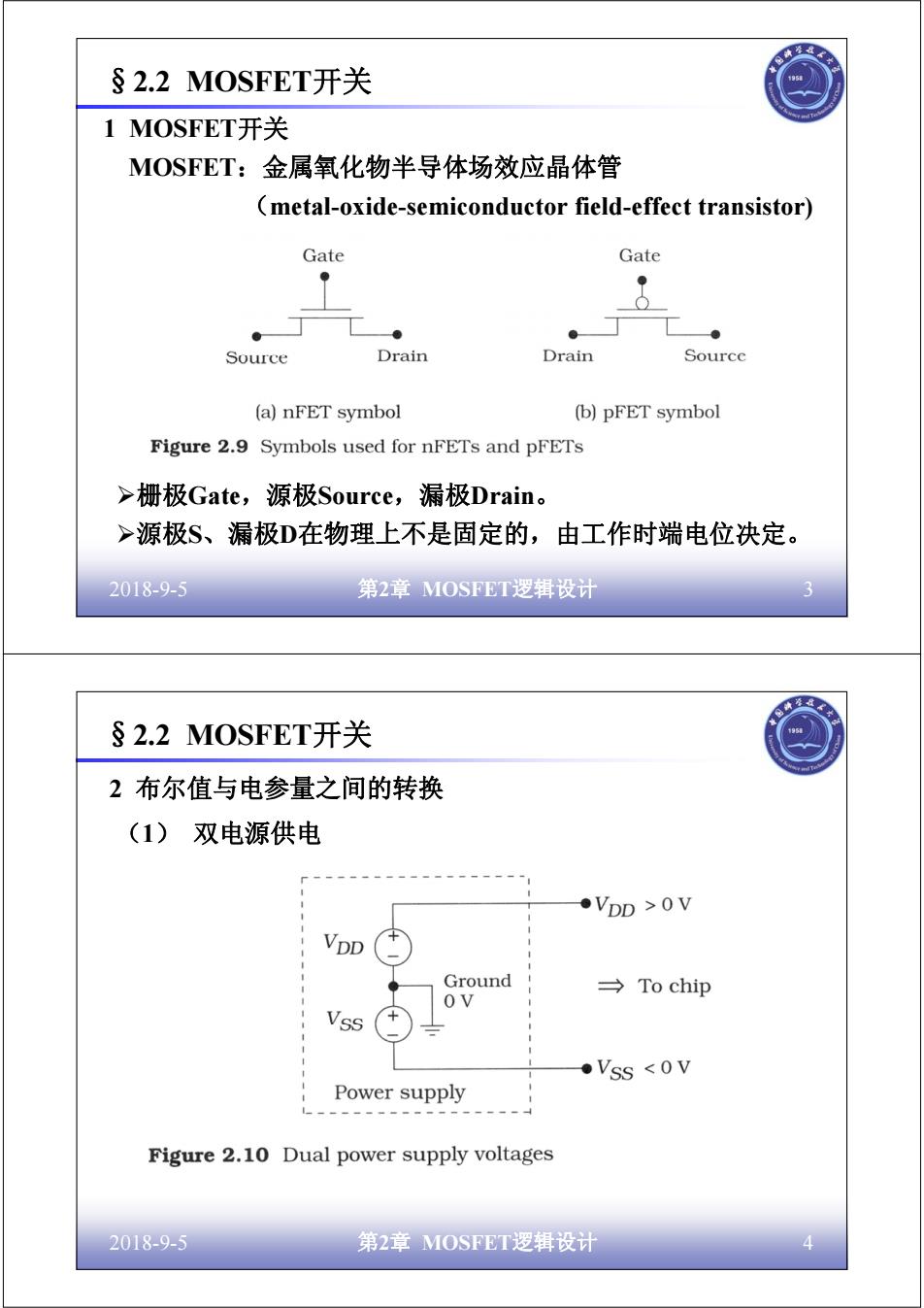

§2.2 MOSFET开关 1 MOSFET开关 MOSFET:金属氧化物半导体场效应晶体管 (metal-oxide-semiconductor field-effect transistor) Gate Gate ● Source Drain Drain Source (a)nFET symbol (b)pFET symbol Figure 2.9 Symbols used for nFETs and pFETs >栅极Gate,源极Source,.漏极Drain。 >源极S、漏极D在物理上不是固定的,由工作时端电位决定。 2018-9-5 第2章MOSFET:逻辑设计 §2.2 MOSFET开关 2布尔值与电参量之间的转换 (1)双电源供电 ●VDD>0V VpD Ground →To chip ov Vss ●Vss<0V Power supply Figure 2.10 Dual power supply voltages 2018-9-5 第2章MOSFET:逻辑设计

2018-9-5 第2章 MOSFET逻辑设计 3 §2.2 MOSFET开关 1 MOSFET开关 ¾栅极Gate,源极Source,漏极Drain。 ¾源极S、漏极D在物理上不是固定的,由工作时端电位决定。 MOSFET:金属氧化物半导体场效应晶体管 (metal-oxide-semiconductor field-effect transistor) 2018-9-5 第2章 MOSFET逻辑设计 4 §2.2 MOSFET开关 2 布尔值与电参量之间的转换 (1) 双电源供电

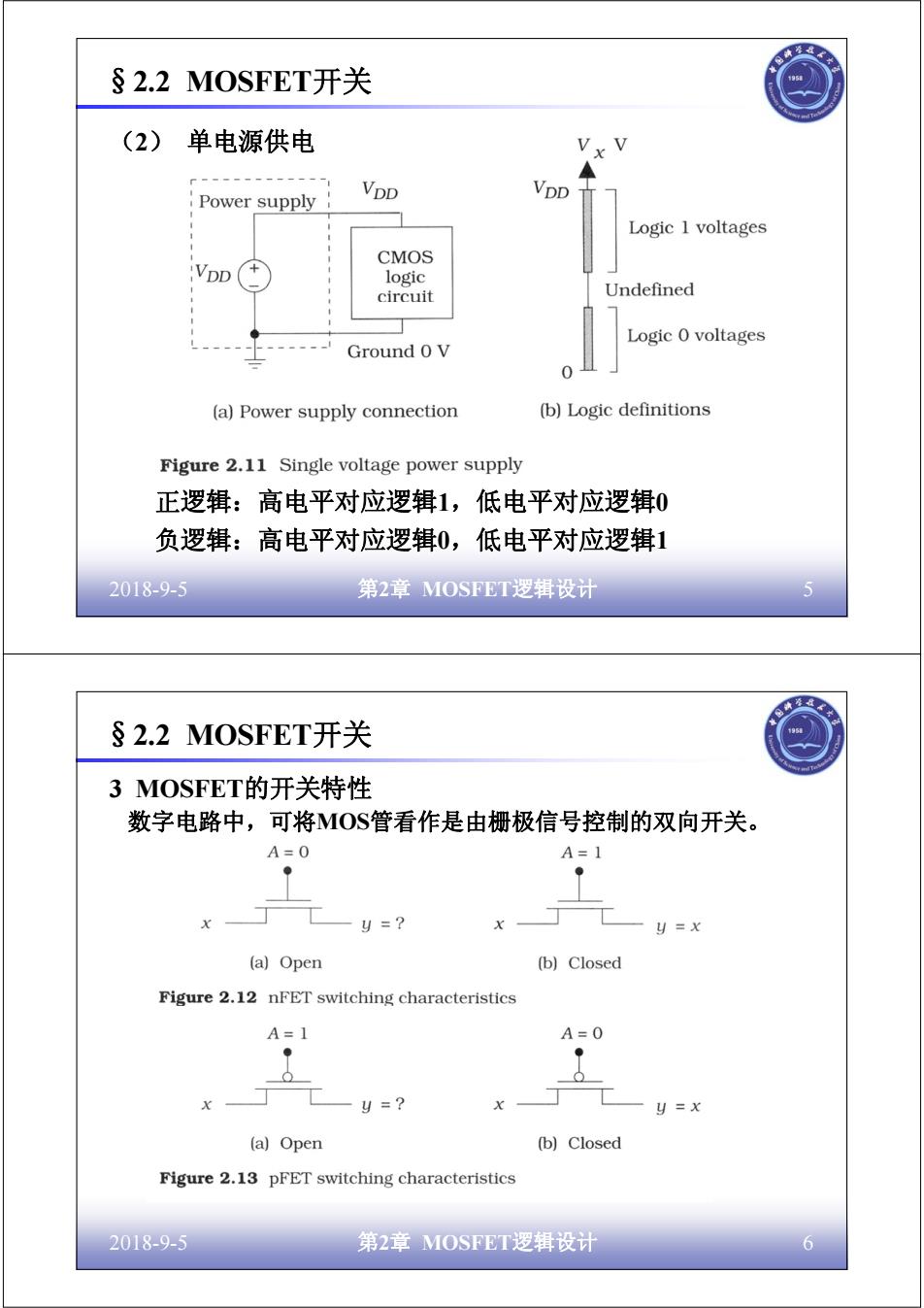

§2.2 MOSFET开关 (2) 单电源供电 i Power supply VpD VpD Logic 1 voltages CMOS VDD logic circuit Undefined Logic 0 voltages Ground 0V (a)Power supply connection (b)Logic definitions Figure 2.11 Single voltage power supply 正逻辑:高电平对应逻辑1,低电平对应逻辑0 负逻辑:高电平对应逻辑0,低电平对应逻辑1 2018-9-5 第2章MOSFET逻辑设计 §2.2 MOSFET开关 3 MOSFET的开关特性 数字电路中,可将MOS管看作是由栅极信号控制的双向开关。 A=0 A=1 丁y=? 一y=X (a)Open (b)Closed Figure 2.12 nFET switching characteristics A=1 A=0 ● y=? y =x (a)Open (b)Closed Figure 2.13 pFET switching characteristics 2018-9-5 第2章MOSFET:逻辑设计 6

2018-9-5 第2章 MOSFET逻辑设计 5 §2.2 MOSFET开关 (2) 单电源供电 正逻辑:高电平对应逻辑1,低电平对应逻辑0 负逻辑:高电平对应逻辑0,低电平对应逻辑1 2018-9-5 第2章 MOSFET逻辑设计 6 §2.2 MOSFET开关 3 MOSFET的开关特性 数字电路中,可将MOS管看作是由栅极信号控制的双向开关

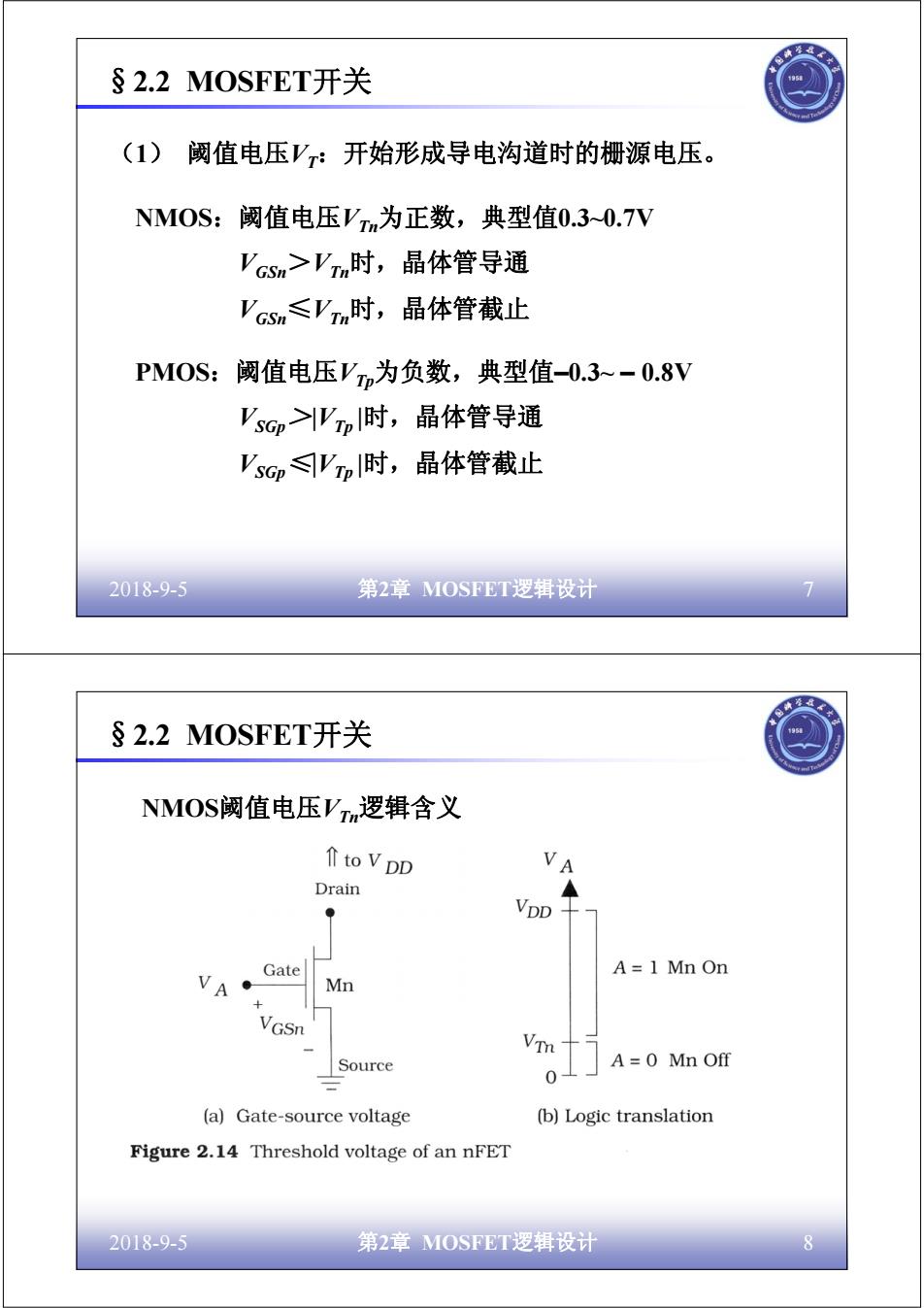

§2.2 MOSFET开关 e (1) 阈值电压V:开始形成导电沟道时的栅源电压。 NMOS:阈值电压Vn为正数,典型值0.30.7V 'csm>Vn时,晶体管导通 'Gsn≤Vm时,晶体管截止 PMOS: 阈值电压V,为负数,典型值-0.3~-0.8V VsGm>Vp时,晶体管导通 VsGnVI时,晶体管截止 2018-9-5 第2章MOSFET:逻辑设计 §2.2 MOSFET开关 NMOS阈值电压V逻辑含义 to V DD Drain VpD Gate A=1 Mn On Mn VGSn Source 01 A=0 Mn Off (a)Gate-source voltage (b)Logic translation Figure 2.14 Threshold voltage of an nFET 2018-9-5 第2章MOSFET:逻辑设计 8

2018-9-5 第2章 MOSFET逻辑设计 7 §2.2 MOSFET开关 (1) 阈值电压VT:开始形成导电沟道时的栅源电压。 NMOS:阈值电压VTn为正数,典型值0.3~0.7V VGSn>VTn时,晶体管导通 VGSn≤VTn时,晶体管截止 PMOS:阈值电压VTp为负数,典型值–0.3~ – 0.8V VSGp>|VTp |时,晶体管导通 VSGp≤|VTp |时,晶体管截止 2018-9-5 第2章 MOSFET逻辑设计 8 §2.2 MOSFET开关 NMOS阈值电压VTn逻辑含义

§2.2 MOSFET开关 PMOS阈值电压V,逻辑含义 Source V DD VsGp VDD A=1 Mp Off VA ● (Vpp·IVTp D-十 Gate Mp A=0 Mp On Drain Ito ground 0 (a)Source-gate voltage (b)Logic translation Figure 2.15 pFET threshold voltage 2018-9-5 第2章MOSFET逻辑设计 §2.2 MOSFET开关 (2) 电压传输特性 NMOS电压传输特性: VpD VpD Vmn in ●Out T。p0ut Vx=0V Vy=Ov Vx Vpn Vy=VI 之 =(VDD -Vmn) (a)Logic 0 transfer (b)Logic 1 transfer Figure 2.16 nFET pass characteristics NMOS传送强逻辑0电压,但传送弱逻辑1电压 2018-9-5 第2章MOSFET:逻辑设计 10

2018-9-5 第2章 MOSFET逻辑设计 9 §2.2 MOSFET开关 PMOS阈值电压VTp逻辑含义 2018-9-5 第2章 MOSFET逻辑设计 10 §2.2 MOSFET开关 (2) 电压传输特性 NMOS电压传输特性: NMOS传送强逻辑0电压,但传送弱逻辑1电压