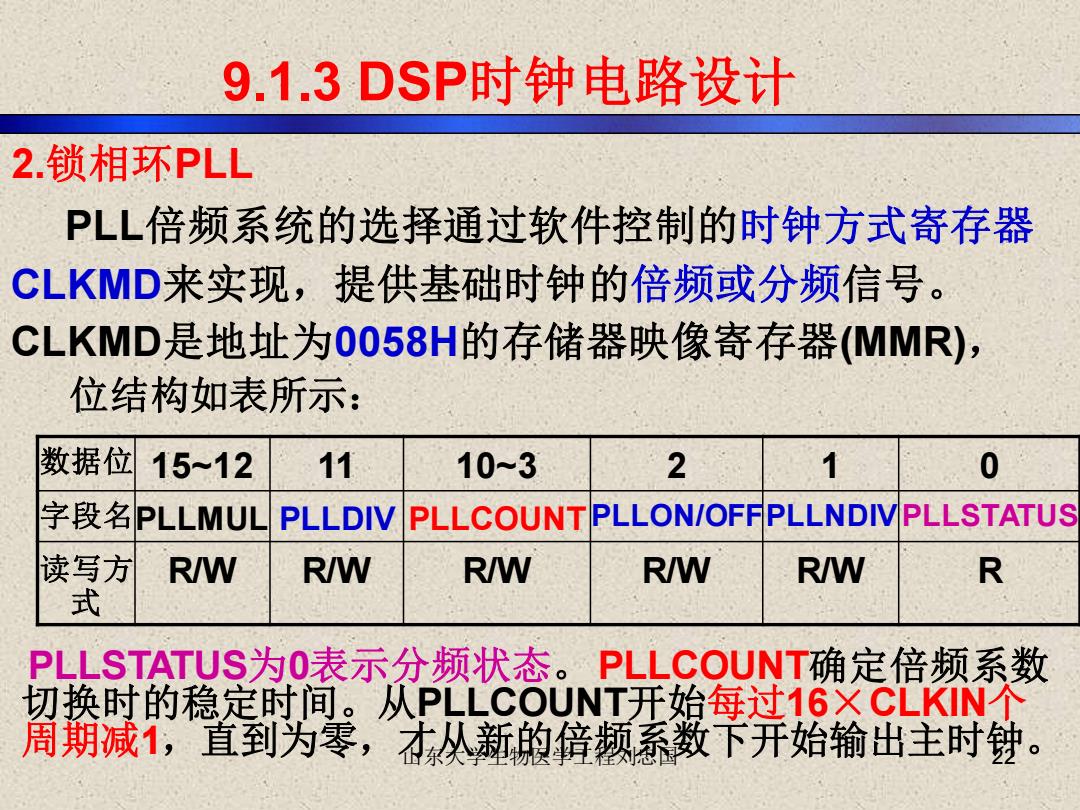

9.1.3DSP时钟电路设计 2.锁相环PLL PLL倍频系统的选择通过软件控制的时钟方式寄存器 CLKMD来实现,提供基础时钟的倍频或分频信号。 CLKMD是地址为0058H的存储器映像寄存器(MMR), 位结构如表所示: 数据位 15~12 11 10~3 2 1 0 字段名PLLMUL PLLDIV PLLCOUNTPLLON/OFFPLLNDIVPLLSTATUS 读写方 R/W R/W R/W R/W R/W R 式 PLLSTATUS为O表示分频状态。PLLCOUNT确定倍频系数 切换时的稳定时间。从PLLCOUNT开始每过16 X CLKIN个 周期减1,直到为零,本公新煦倍频系数下开始输出主时缈

9.1.3 DSP时钟电路设计 山东大学生物医学工程刘忠国 22 数据位 15~12 11 10~3 2 1 0 字段名PLLMUL PLLDIV PLLCOUNT PLLON/OFFPLLNDIVPLLSTATUS 读写方 式 R/W R/W R/W R/W R/W R 2.锁相环PLL PLL倍频系统的选择通过软件控制的时钟方式寄存器 CLKMD来实现,提供基础时钟的倍频或分频信号。 CLKMD是地址为0058H的存储器映像寄存器(MMR), PLLSTATUS为0表示分频状态。 位结构如表所示: PLLCOUNT确定倍频系数 切换时的稳定时间。从PLLCOUNT开始每过16×CLKIN个 周期减1,直到为零,才从新的倍频系数下开始输出主时钟

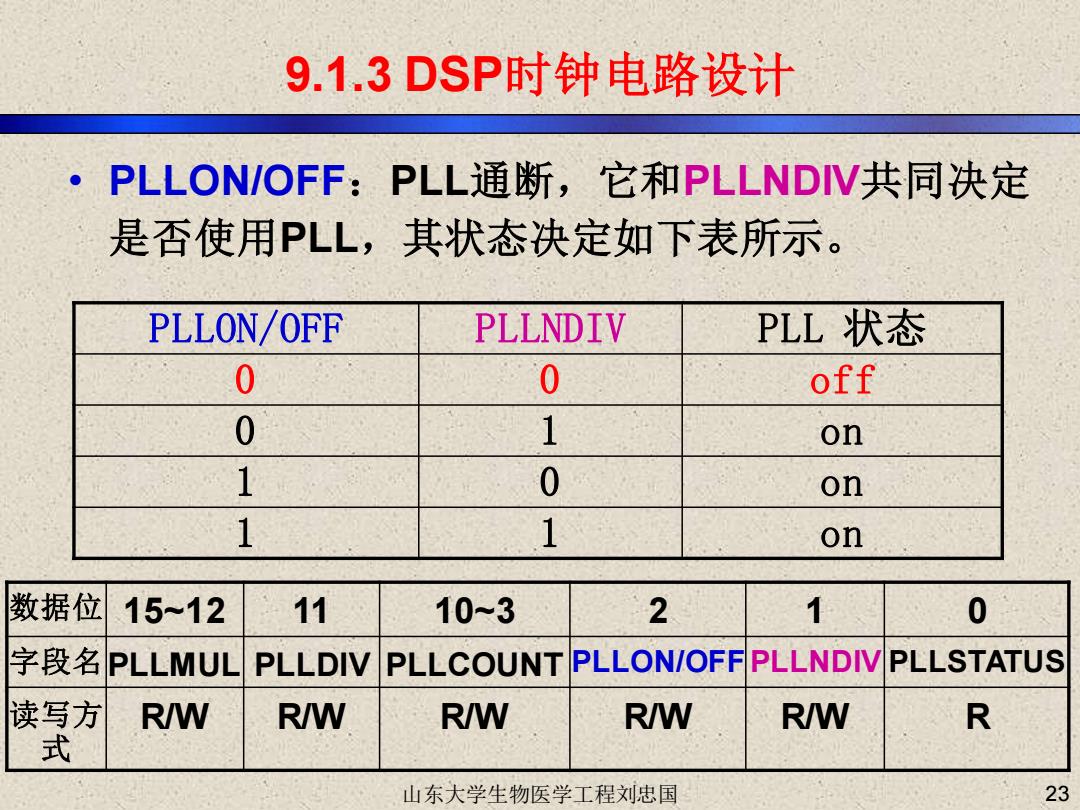

9.1.3DSP时钟电路设计 PLLON/OFF:PLL通断,它和PLLNDIV共同决定 是否使用PLL,其状态决定如下表所示。 PLLON/OFF PLLNDIV PLL状态 0 0 off 0 1 on 1 0 on 1 1 on 数据位 15~12 11 10-3 2 1 0 字段名PLLMUL PLLDIV PLLCOUNT PLLON/OFFPLLNDIVPLLSTATUS 读写方 R/W R/W R/W R/W R/W R 式 山东大学生物医学工程刘忠国 23

9.1.3 DSP时钟电路设计 • PLLON/OFF:PLL通断,它和PLLNDIV共同决定 是否使用PLL,其状态决定如下表所示。 PLLON/OFF PLLNDIV PLL 状态 0 0 off 0 1 on 1 0 on 1 1 on 数据位 15~12 11 10~3 2 1 0 字段名PLLMUL PLLDIV PLLCOUNT PLLON/OFFPLLNDIV PLLSTATUS 读写方 式 R/W R/W R/W R/W R/W R 山东大学生物医学工程刘忠国 23

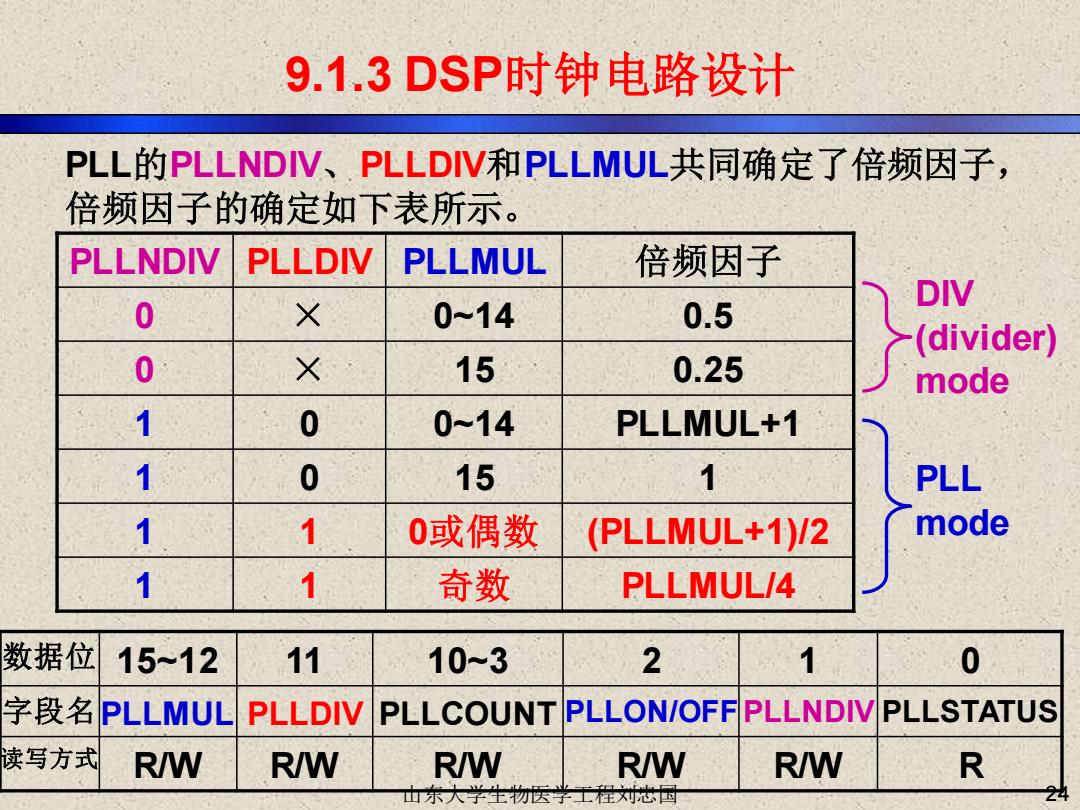

9.1.3DSP时钟电路设计 PLL的PLLNDIV、PLLDIV和PLLMUL共同确定了倍频因子, 倍频因子的确定如下表所示。 PLLNDIV PLLDIV PLLMUL 倍频因子 0 × DIV 0~14 0.5 (divider) 0 × 15 0.25 mode 1 0 0~14 PLLMUL+1 1 0 15 1 PLL 1 1 0或偶数 (PLLMUL+1)/2 mode 1 1 奇数 PLLMUL/4 数据位 15~12 11 10~3 2 1 0 字段名PLLMUL PLLDIV PLLCOUNTPLLON/OFFPLLNDIVPLLSTATUS 读写方式 R/W R/W R/W R/W R/W R 山东人子生物医字士任刘心国

9.1.3 DSP时钟电路设计 PLL的PLLNDIV、PLLDIV和PLLMUL共同确定了倍频因子, 倍频因子的确定如下表所示。 PLLNDIV PLLDIV PLLMUL 倍频因子 0 × 0~14 0.5 0 × 15 0.25 1 0 0~14 PLLMUL+1 1 0 15 1 1 1 0或偶数 (PLLMUL+1)/2 1 1 奇数 PLLMUL/4 数据位 15~12 11 10~3 2 1 0 字段名PLLMUL PLLDIV PLLCOUNT PLLON/OFFPLLNDIV PLLSTATUS 读写方式 R/W R/W R/W R/W R/W R 24 DIV (divider) mode PLL mode 山东大学生物医学工程刘忠国

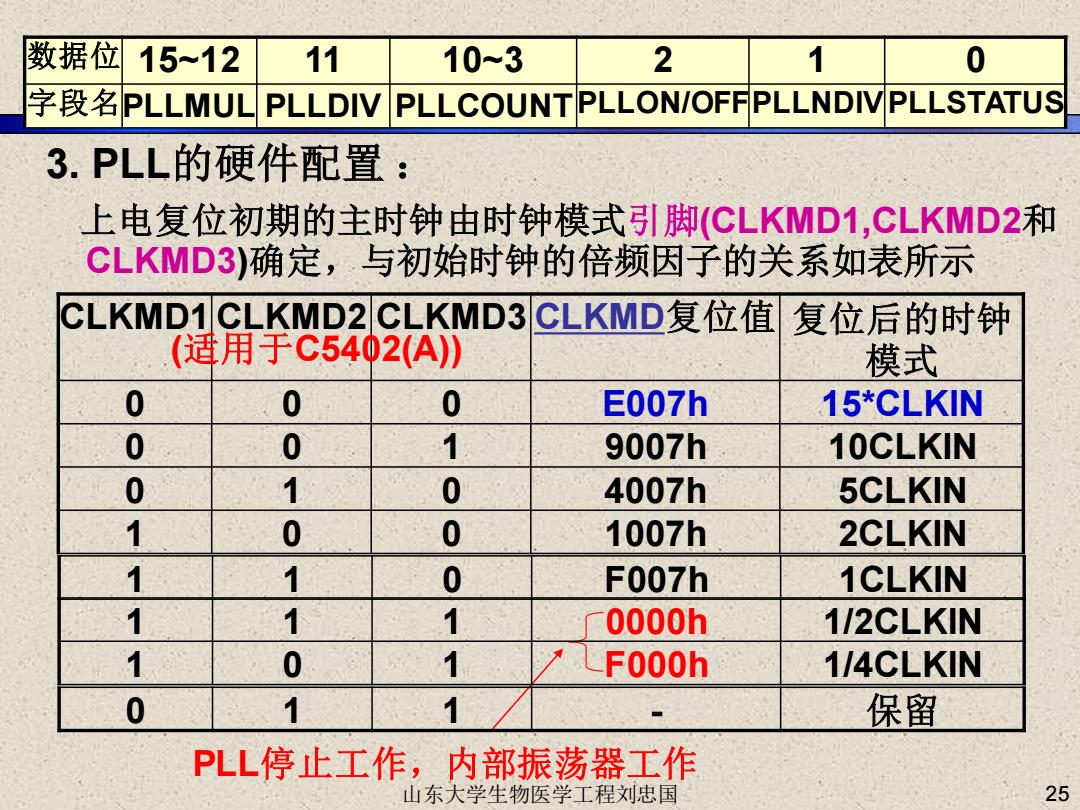

数据位15~12 11 10~3 2 1 0 字段名PLLMULPLLDIV PLLCOUNTPLLON/OFFPLLNDIVPLLSTATUS 3.PLL的硬件配置 上电复位初期的主时钟由时钟模式引脚(CLKMD1,CLKMD2和 CLKMD3)确定,与初始时钟的倍频因子的关系如表所示 CLKMD1 CLKMD2 CLKMD3 CLKMD复位值复位后的时钟 (适用于C5402(A) 模式 0 0 0 E007h 15*CLKIN 0 0 1 9007h 10CLKIN 0 1 0 4007h 5CLKIN 1 0 0 1007h 2CLKIN 1 1 0 F007h 1CLKIN 1 1 1 0000h 1/2CLKIN 1 0 1 /F000h 1/4CLKIN 0 1 1 保留 PLL停止工作,内部振荡器工作 山东大学生物医学工程刘忠国 25

9.1.3 DSP时钟电路设计 3. PLL的硬件配置 : 上电复位初期的主时钟由时钟模式引脚(CLKMD1,CLKMD2和 CLKMD3)确定,与初始时钟的倍频因子的关系如表所示 CLKMD1 CLKMD2 CLKMD3 CLKMD复位值 复位后的时钟 模式 0 0 0 E007h 15*CLKIN 0 0 1 9007h 10CLKIN 0 1 0 4007h 5CLKIN 1 0 0 1007h 2CLKIN PLL停止工作,内部振荡器工作 数据位 15~12 11 10~3 2 1 0 字段名PLLMUL PLLDIV PLLCOUNTPLLON/OFFPLLNDIVPLLSTATUS (适用于C5402(A)) 山东大学生物医学工程刘忠国 25 0 1 1 - 保留 1 1 1 0000h 1/2CLKIN 1 0 1 F000h 1/4CLKIN 1 1 0 F007h 1CLKIN

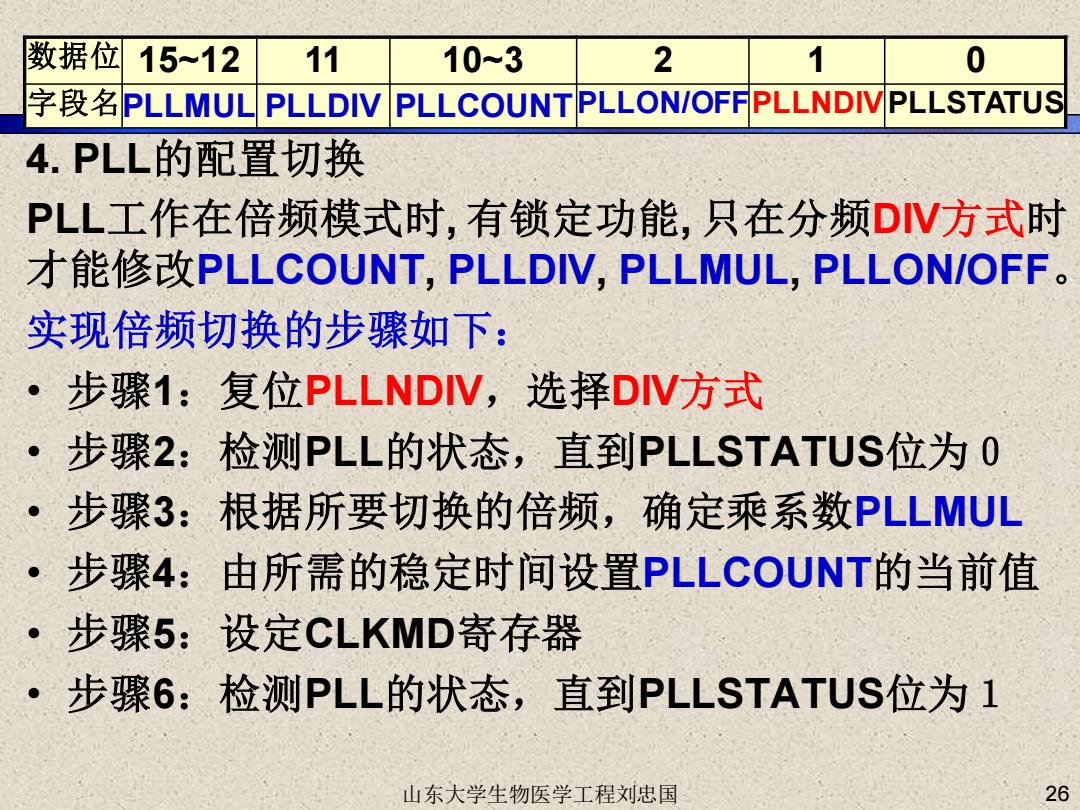

数据位15~12 11 10~3 2 1 0 字段名PLLMULPLLDIV PLLCOUNTPLLON/OFFPLLNDIVPLLSTATUS 4.PLL的配置切换 PLL工作在倍频模式时,有锁定功能,只在分频DⅣ方式时 才能修改PLLCOUNT,PLLDIV,PLLMUL,PLLON/OFF。 实现倍频切换的步骤如下: 步骤1:复位PLLNDIV,选择DV方式 步骤2:检测PLL的状态,直到PLLSTATUS位为0 ·步骤3:根据所要切换的倍频,确定乘系数PLLMUL ·步骤4:由所需的稳定时间设置PLLCOUNT的当前值 步骤5:设定CLKMD寄存器 步骤6:检测PLL的状态,直到PLLSTATUS位为1 山东大学生物医学工程刘忠国 26

9.1.3 DSP时钟电路设计 4. PLL的配置切换 PLL工作在倍频模式时, 有锁定功能, 只在分频DIV方式时 才能修改PLLCOUNT, PLLDIV, PLLMUL, PLLON/OFF。 实现倍频切换的步骤如下: • 步骤1:复位PLLNDIV,选择DIV方式 • 步骤2:检测PLL的状态,直到PLLSTATUS位为0 • 步骤3:根据所要切换的倍频,确定乘系数PLLMUL • 步骤4:由所需的稳定时间设置PLLCOUNT的当前值 • 步骤5:设定CLKMD寄存器 • 步骤6:检测PLL的状态,直到PLLSTATUS位为1 山东大学生物医学工程刘忠国 26 数据位 15~12 11 10~3 2 1 0 字段名PLLMUL PLLDIV PLLCOUNTPLLON/OFFPLLNDIVPLLSTATUS