9.1.2DSP复位电路设计 对DSP进行复位的方法有以下几种: 1.软件复位法:程序内执行“RESET”汇编语句实现。 2硬件复位法:上电复位、手动复位、自动复位。 )RC上电复位电路:利用RC电路的延迟特性来产生复 位所需要的低电平时间,其电路结构如图所示: 5v 1.5V t=-RC In(1- 5V cc 要求: 100k R 74HC14 TMS320054x 10 100-~200ms Vc RS t=167ms 4宝 施密特触发器保 证复位脉冲低电 平持续期的稳定。 山东大学生物医学工程刘忠国 17

9.1.2 DSP复位电路设计 • 对DSP进行复位的方法有以下几种: 1.软件复位法:程序内执行“RESET”汇编语句实现。 2.硬件复位法:上电复位、手动复位、自动复位。 1)RC上电复位电路:利用RC电路的延迟特性来产生复 位所需要的低电平时间,其电路结构如图所示: 100kΩ 4.7uf 5v 要求: 100~200ms 施密特触发器保 证复位脉冲低电 平持续期的稳定。) V V t ln(1 CC C = −RC − 1.5V 5V Vc 17 t=167ms 山东大学生物医学工程刘忠国

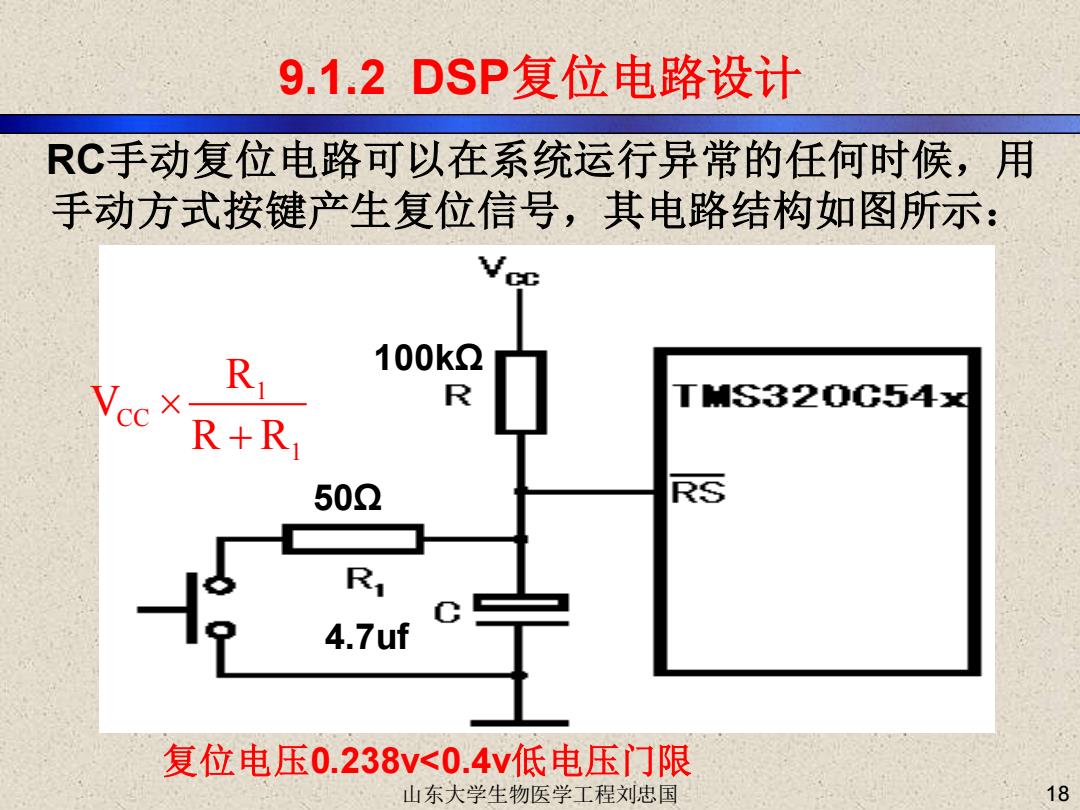

9.1.2DSP复位电路设计 RC手动复位电路可以在系统运行异常的任何时候,用 手动方式按键产生复位信号,其电路结构如图所示: CC 100k Vcc× R R TMS320054x R+R 500 RS R 4.7uf 复位电压0.238v<0.4v低电压门限 山东大学生物医学工程刘忠国 18

9.1.2 DSP复位电路设计 RC手动复位电路可以在系统运行异常的任何时候,用 手动方式按键产生复位信号,其电路结构如图所示: 50Ω 100kΩ 4.7uf 1 CC 1 R V R R + 18 复位电压0.238v<0.4v低电压门限 山东大学生物医学工程刘忠国

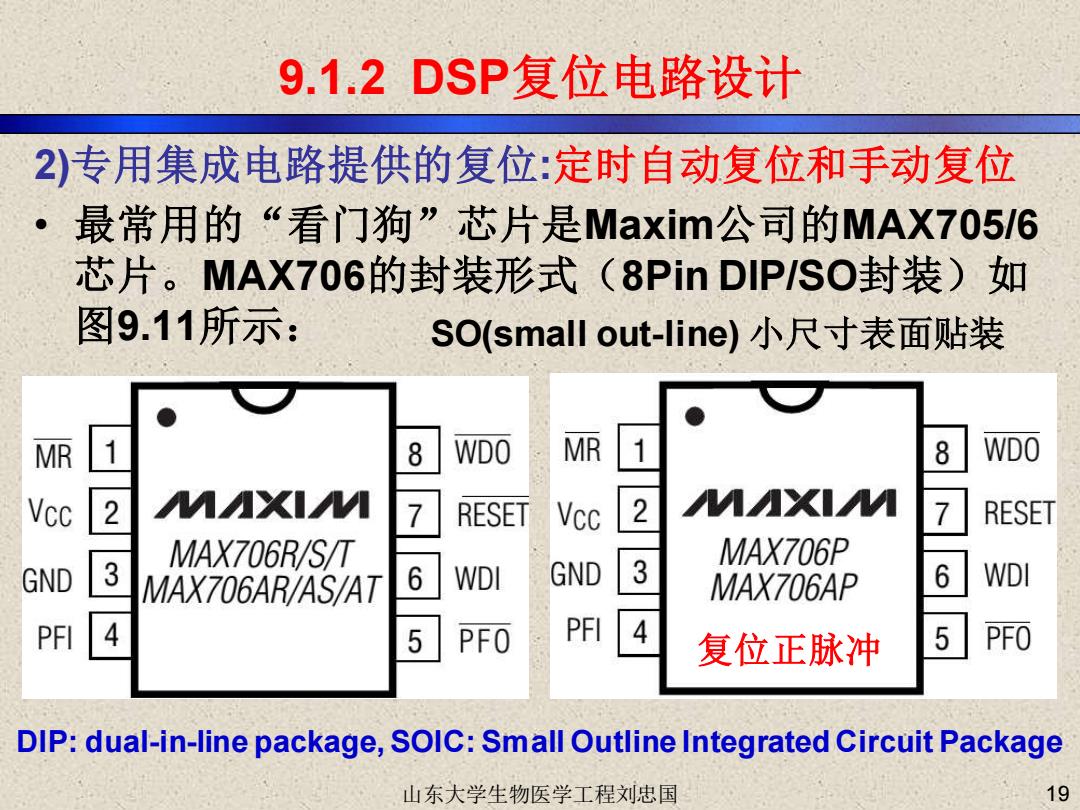

9.1.2DSP复位电路设计 2)专用集成电路提供的复位:定时自动复位和手动复位 最常用的“看门狗”芯片是Maxim公司的MAX705/6 芯片。MAX706的封装形式(8 Pin DIP/SO封装)如 图9.11所示: SO(small out-.line)小尺寸表面贴装 1 8 WDO MR 1 8 WDO 2 MAXIM 7 RESET Vcc 2 MAXIM 7 RESET MAX706R/S/T MAX706P 3 MAX706AR/AS/AT 6 WDI GND 3 MAX706AP 6 WDI PF 4 5 PFO PFI 复位正脉冲 5 PFO DIP:dual-in-line package,SOIC:Small Outline Integrated Circuit Package 山东大学生物医学工程刘忠国 19

9.1.2 DSP复位电路设计 2)专用集成电路提供的复位:定时自动复位和手动复位 • 最常用的“看门狗”芯片是Maxim公司的MAX705/6 芯片。MAX706的封装形式(8Pin DIP/SO封装)如 图9.11所示: SO(small out-line) 小尺寸表面贴装 DIP: dual-in-line package, SOIC: Small Outline Integrated Circuit Package 山东大学生物医学工程刘忠国 19 复位正脉冲

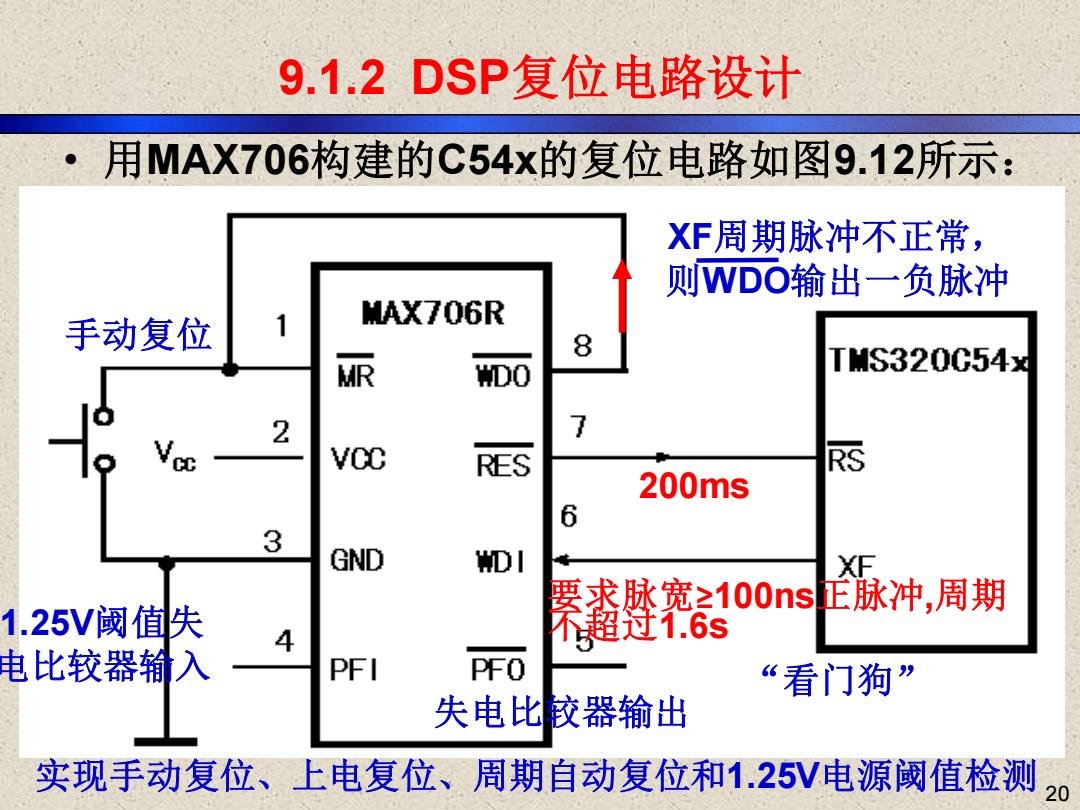

9.1.2DSP复位电路设计 用MAX706构建的C54x的复位电路如图9.12所示: XF周期脉冲不正常, 则WDO输出一负脉冲 MAX706R 手动复位 8 MR WDO TMS320054x 2 V00 RES RS 200ms 6 3 GND XF 要求脉宽≥100ns正脉冲,周期 1.25V阈值失 4 不超过1.6s 电比较器输入 PFI PFO “看门狗” 失电比较器输出 实现手动复位、上电复位、周期自动复位和1.25V电源阈值检测 20

9.1.2 DSP复位电路设计 • 用MAX706构建的C54x的复位电路如图9.12所示: 20 200ms 手动复位 要求脉宽≥100ns正脉冲,周期 不超过1.6s XF周期脉冲不正常, 则WDO输出一负脉冲 实现手动复位、上电复位、周期自动复位和1.25V电源阈值检测 “看门狗” 1.25V阈值失 电比较器输入 失电比较器输出

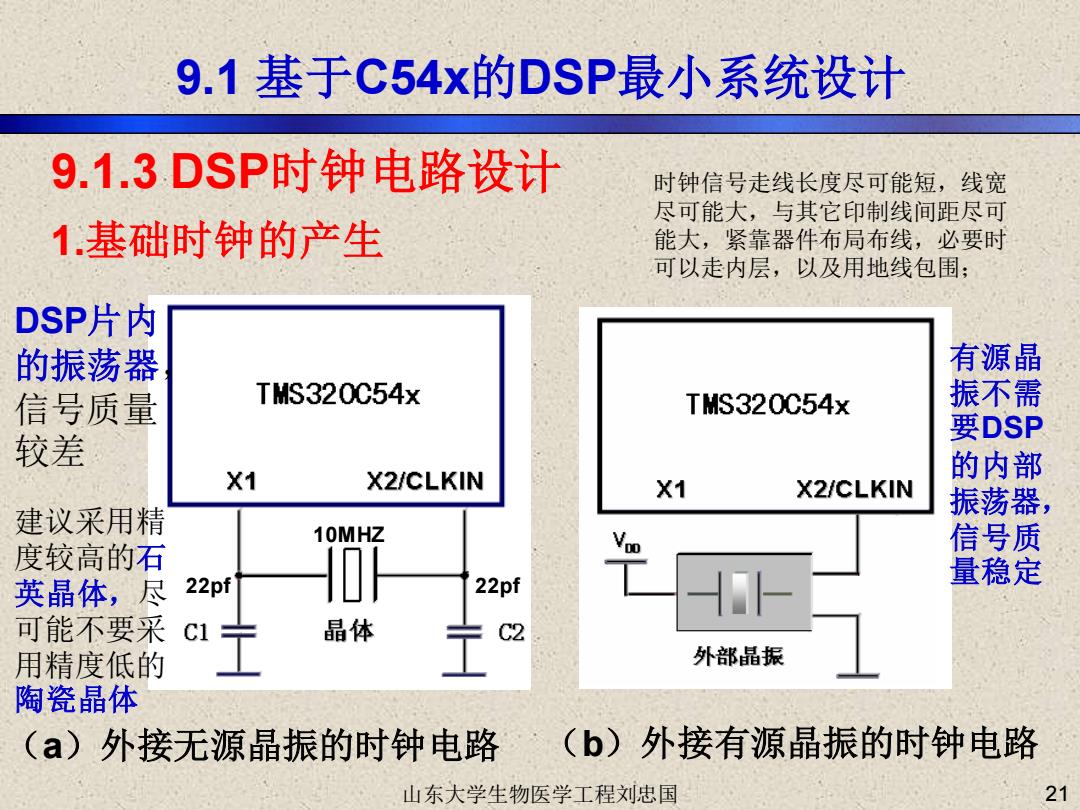

9.1基于C54x的DSP最小系统设计 9.1.3DSP时钟电路设计 时钟信号走线长度尽可能短,线宽 尽可能大,与其它印制线间距尽可 1基础时钟的产生 能大,紧靠器件布局布线,必要时 可以走内层,以及用地线包围; DSP片内 的振荡器 信号质量 TMS320C54x TMS320C54x 需 DSP 较差 X1 X2/CLKIN 的内部 X1 X2/CLKIN 建议采用精 振荡器, 10M 度较高的石 英晶体,尽 22pf 0 22pf 可能不要采 晶体 C2 用精度低的 外部晶振 陶瓷晶体 (a)外接无源晶振的时钟电路 (b)外接有源晶振的时钟电路 山东大学生物医学工程刘忠国 21

9.1 基于C54x的DSP最小系统设计 9.1.3 DSP时钟电路设计 1.基础时钟的产生 时钟信号走线长度尽可能短,线宽 尽可能大,与其它印制线间距尽可 能大,紧靠器件布局布线,必要时 可以走内层,以及用地线包围; DSP片内 的振荡器, 信号质量 较差 有源晶 振不需 要DSP 的内部 振荡器, 信号质 量稳定 建议采用精 10MHZ 度较高的石 英晶体,尽 可能不要采 用精度低的 陶瓷晶体 22pf 22pf 21 (a)外接无源晶振的时钟电路 (b)外接有源晶振的时钟电路 山东大学生物医学工程刘忠国