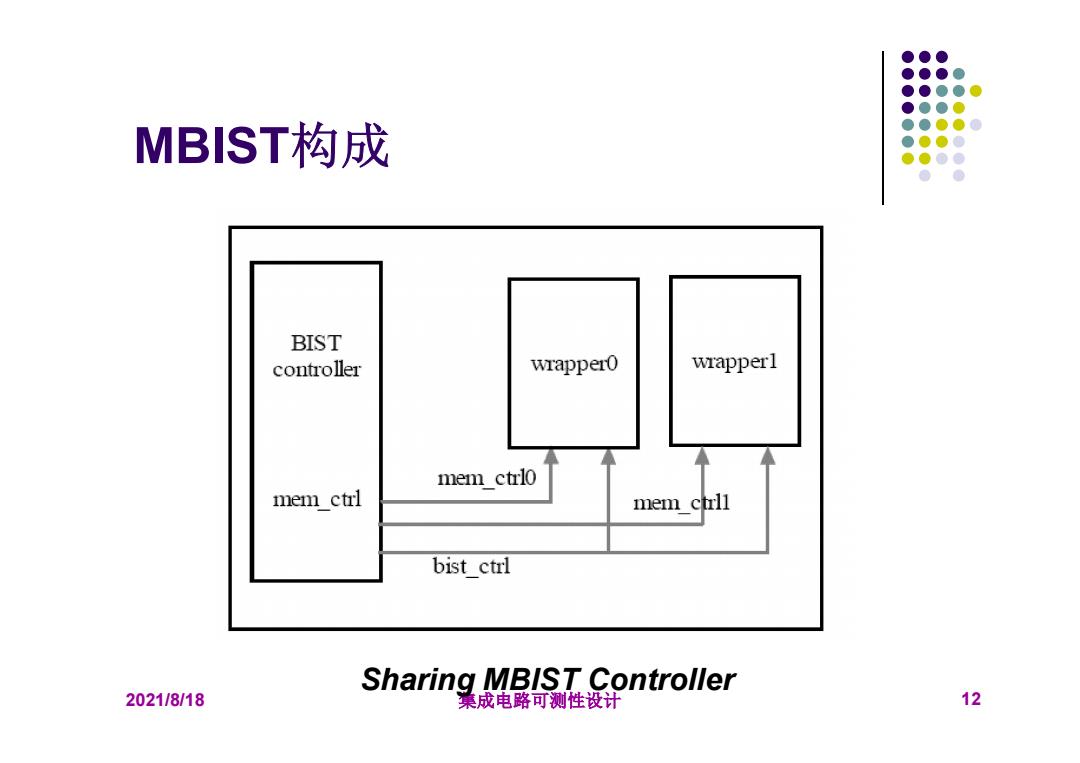

●● ●●●● ●●● ●●●●0 MBIST构成 ●●●● ●●● BIST controller wrapper0 wrapperl mem ctrlo mem ctrl mem ctrll bist ctrl Sharing MBIST Controller 2021/8/18 巢成电路可测性设计 12

2021/8/18 集成电路可测性设计 12 MBIST构成 Sharing MBIST Controller

●● 定义 ●●●● BLBO-Buit-in logic block observer,内建逻辑模 块观察器,给触发器增加的额外硬件,以便它们可改装 为LFSR矢量生成器或响应压缩器、扫描链、或触发 器. ● CUT-被测电路(Circuit-under-test) ·穷举测试-施加所有可能的2n矢量到具有n个输入的 电路. ● 不可化简的多项式-不能分解的布尔多项式: ● LFSR-Linear feedback shift register,线性反馈移 位寄存器,生成伪-随机测试矢量序列的硬件. 2021/8/18 集成电路可测性设计 13

2021/8/18 集成电路可测性设计 13 定义 BILBO – Built-in logic block observer,内建逻辑模 块观察器, 给触发器增加的额外硬件, 以便它们可改装 为LFSR矢量生成器或响应压缩器、扫描链、或触发 器. CUT – 被测电路( Circuit-under-test ) 穷举测试– 施加所有可能的2n 矢量到具有n个输入的 电路. 不可化简的多项式– 不能分解的布尔多项式. LFSR – Linear feedback shift register,线性反馈移 位寄存器, 生成伪-随机测试矢量序列的硬件

●●0 定义 ●●●● ●●● ●伪穷举测试-Pseudo-exhaustive testing,将电路划 分为较小的电路,重迭模块和完全测试每个模块, 。 伪随机测试-Pseudo-random testing,算法矢量生成 器产生所有可能测试矢量的子集,具有随机产生矢量 的大部分特性. ●签名-Signature,区分好电路和坏电路之间的统计电 ·路特性。 TPG-Hardware test pattern generator,.硬件测试 矢量生成器 2021/8/18 集成电路可测性设计 14

2021/8/18 集成电路可测性设计 14 定义 伪穷举测试– Pseudo-exhaustive testing,将电路划 分为较小的电路, 重迭模块和完全测试每个模块. 伪随机测试– Pseudo-random testing,算法矢量生成 器产生所有可能测试矢量的子集, 具有随机产生矢量 的大部分特性. 签名– Signature,区分好电路和坏电路之间的统计电 路特性. TPG – Hardware test pattern generator,硬件测试 矢量生成器

●●●● ●●● ●●●● ●●●● ●●0● ●●o● ● 2、BST结构 2021/8/18 集成电路可测性设计 15

2021/8/18 集成电路可测性设计 15 2、BIST结构

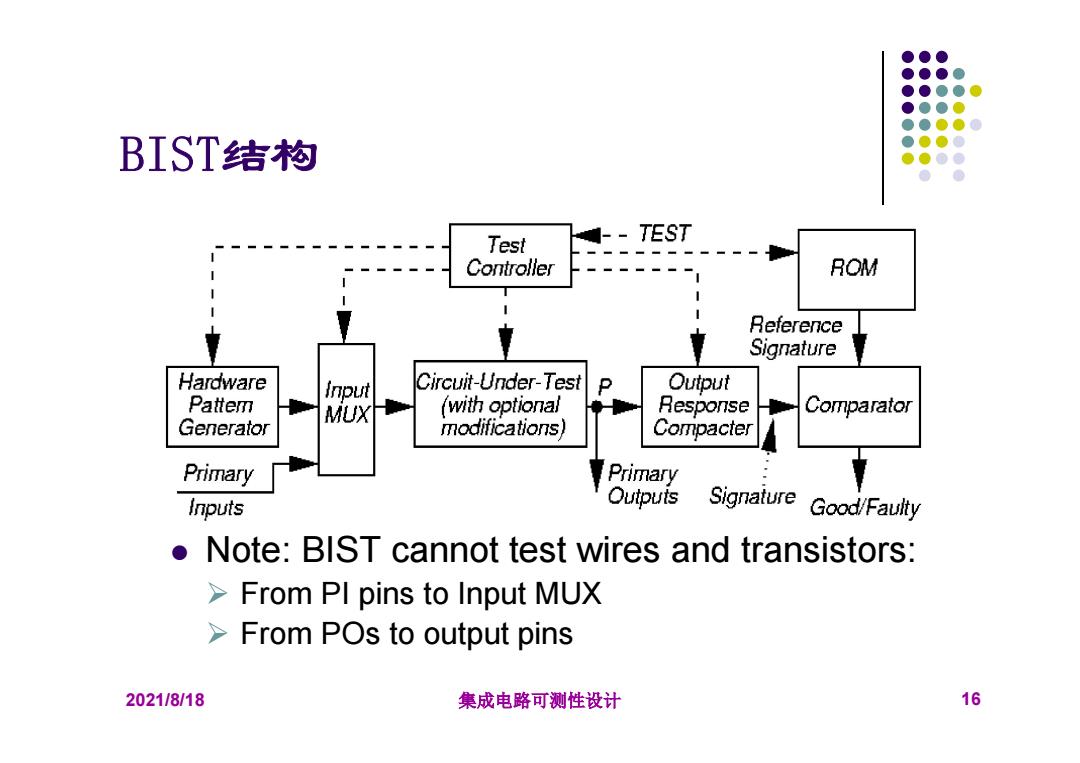

● BIST结构 ●●●● ●●●● Test -TEST Controller ROM Reference Signature Hardware Input Circuit-Under-Test P Output Pattem MUX (with optional Response Comparator Generator modifications) Compacter Primary Primary Inputs Outputs Signature Good/Faulty Note:BIST cannot test wires and transistors: >From PI pins to Input MUX From POs to output pins 2021/8/18 集成电路可测性设计 16

2021/8/18 集成电路可测性设计 16 BIST结构 Note: BIST cannot test wires and transistors: From PI pins to Input MUX From POs to output pins