● ● 基于总线的BIST结构 ●● ●● ●●@ CUT1 CUT2 CUTn Common Bus Self-Test Control 0 Self-test contro/broadcasts patterns to each CUT over bus parallel pattern generation Awaits bus transactions showing CUT's responses to the patterns:serialized compaction 2021/8/18 集成电路可测性设计 17

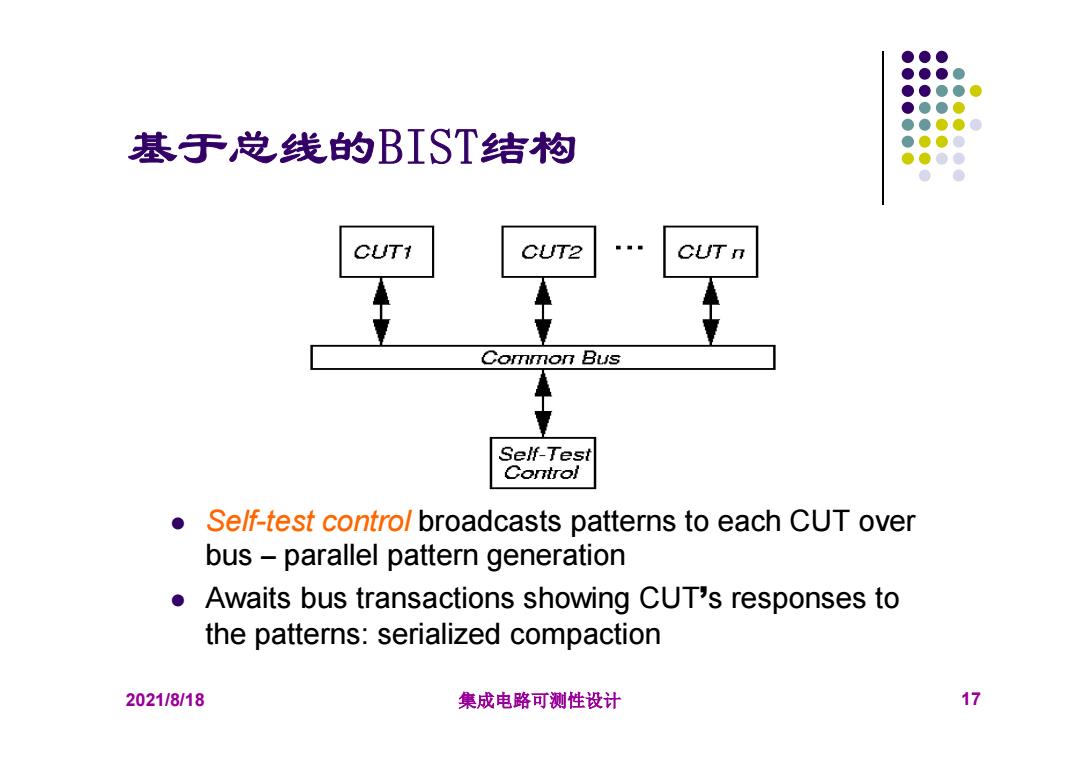

2021/8/18 集成电路可测性设计 17 基于总线的BIST结构 Self-test control broadcasts patterns to each CUT over bus – parallel pattern generation Awaits bus transactions showing CUT’s responses to the patterns: serialized compaction

●● ● ●●0 BIST过程 ●●●● Pattern Generator Syster Board Chip Test Test Test CUT Controller Controller Controller Response Analyzer Test controller-Hardware that activates self-test simultaneously on all PCBs ● Each board controller activates parallel chip BIST Diagnosis effective only if very high fault coverage 2021/8/18 集成电路可测性设计 18

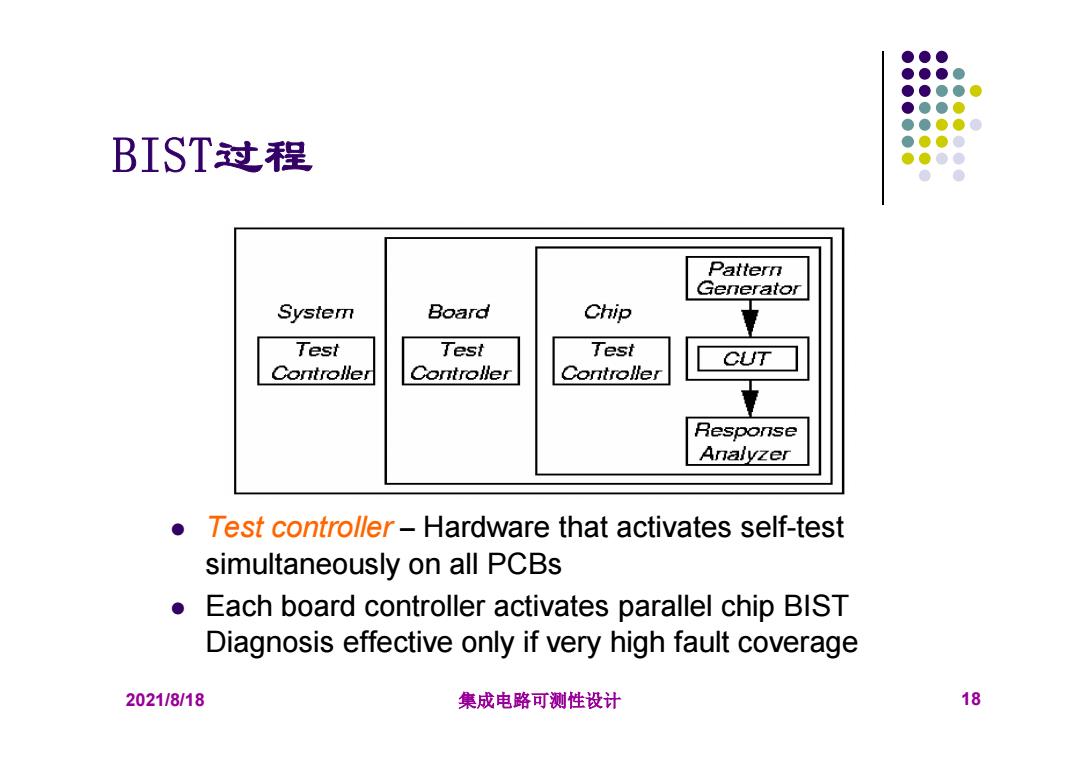

2021/8/18 集成电路可测性设计 18 BIST过程 Test controller – Hardware that activates self-test simultaneously on all PCBs Each board controller activates parallel chip BIST Diagnosis effective only if very high fault coverage

●●● ●●● ●●0 ●● ●●●● ●●0● ●●0● 3、BIST的激励 2021/8/18 集成电路可测性设计 19

2021/8/18 集成电路可测性设计 19 3、BIST的激励

●● ● ● BST的测试生成 ●●●● ●●●● 穷举测试 伪穷举测试 伪随机测试 症候群计数器 穷举TPG 加权TPG 加权常数计数器 L4FSR和移位寄存器结金 适应TPG LFSR和异或门结合 简化的LFSR 循环LFSR 2021/8/18 集成电路可测性设计 20

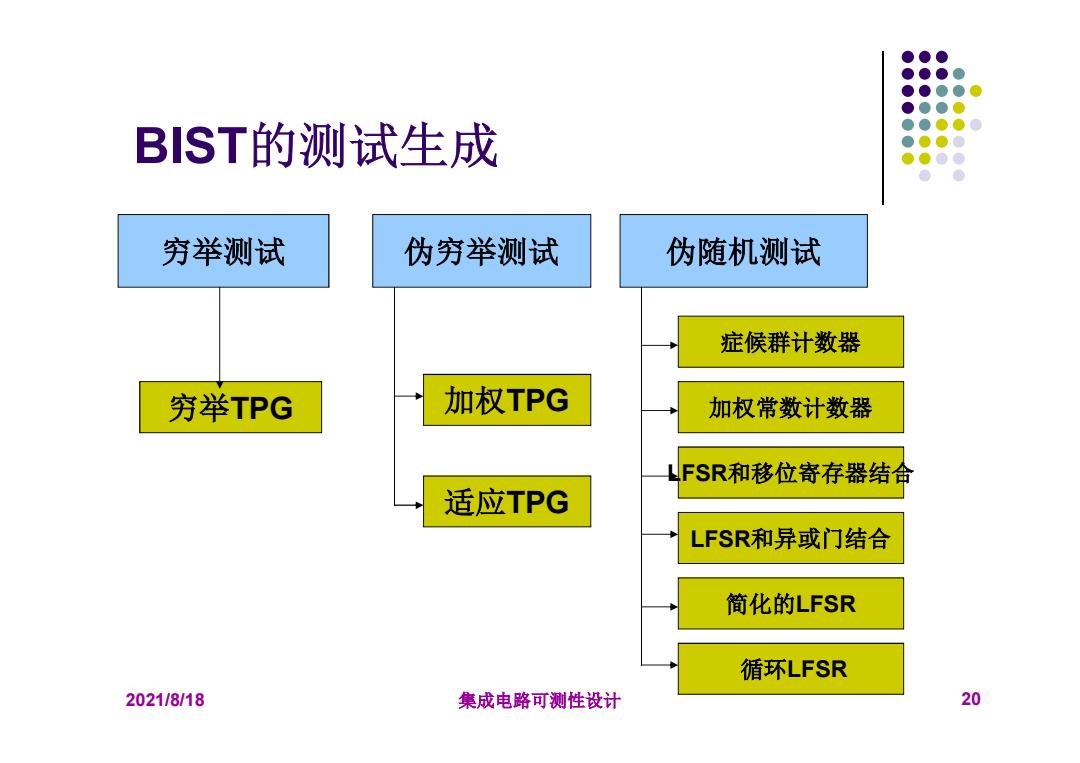

2021/8/18 集成电路可测性设计 20 BIST的测试生成 穷举测试 伪穷举测试 伪随机测试 症候群计数器 加权常数计数器 LFSR和移位寄存器结合 LFSR和异或门结合 简化的LFSR 循环LFSR 加权TPG 适应TPG 穷举TPG

●● ● ●● 穷举矢量生成 ●●●● ●●● 。表明每个状态和转变工作 。对于n-输入电路,总共要求2n矢量 n>20是不实际的 Q3 Clock Reset Q1 Q2 Q3 穷举测试矢量生成器 2021/8/18 集成电路可测性设计 21

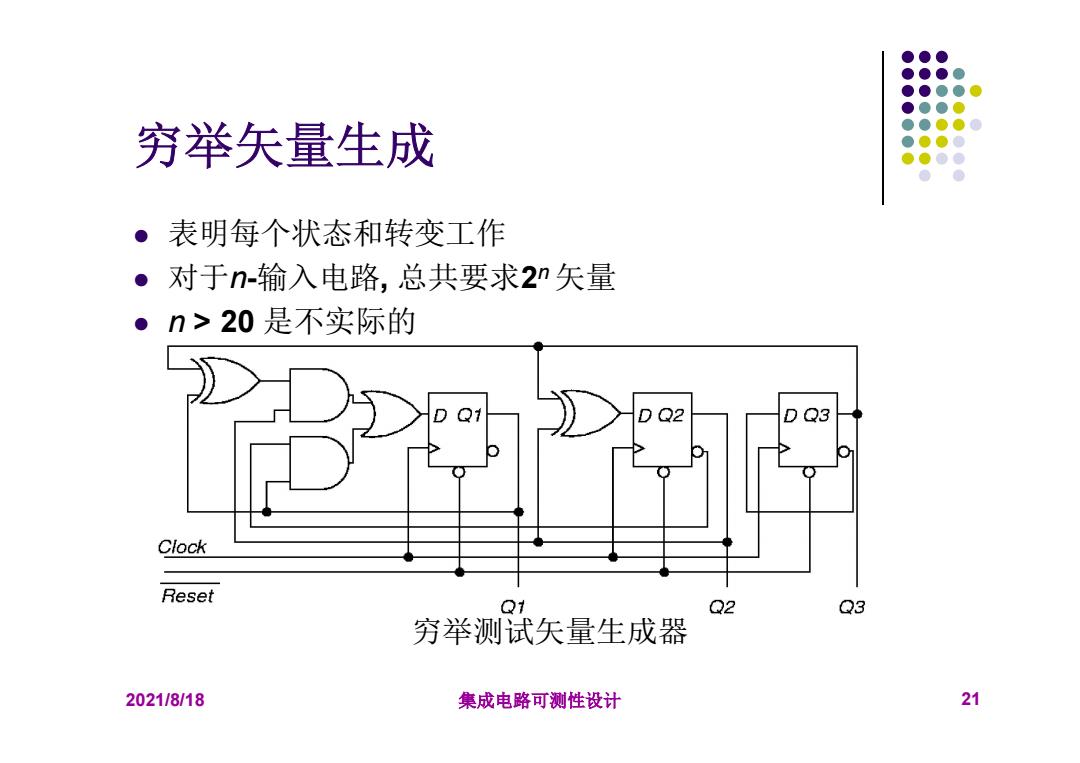

2021/8/18 集成电路可测性设计 21 穷举矢量生成 表明每个状态和转变工作 对于n-输入电路, 总共要求2n 矢量 n > 20 是不实际的 穷举测试矢量生成器