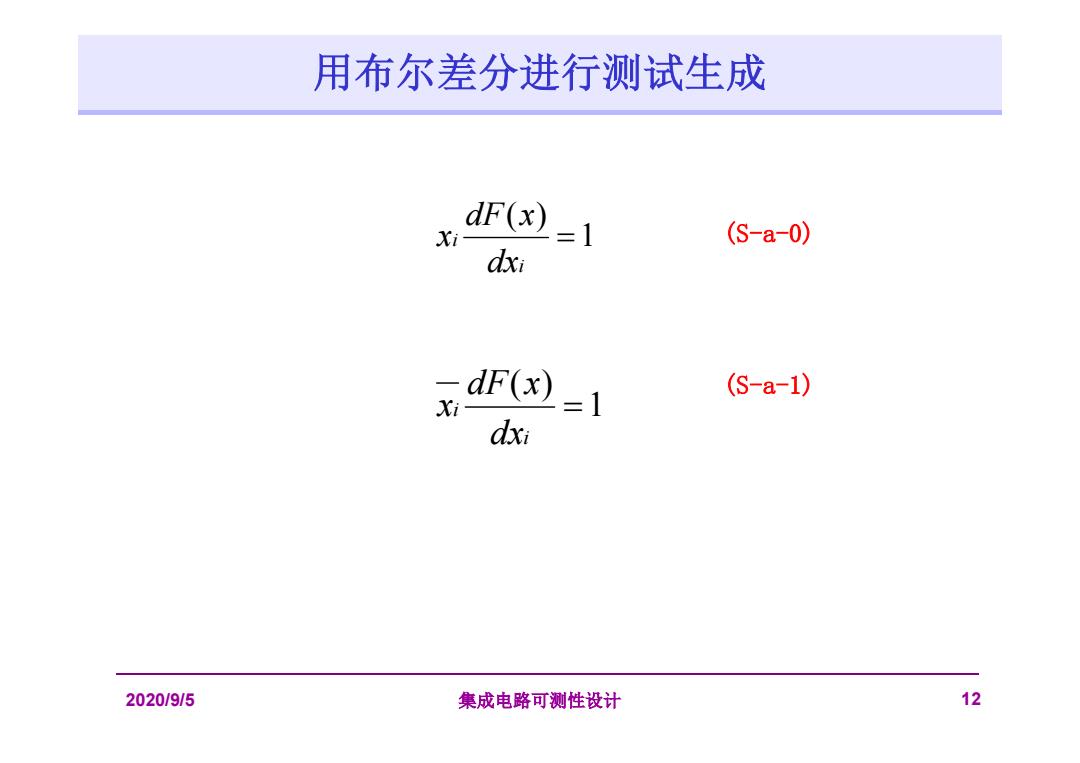

用布尔差分进行测试生成 Xi dF(x)=1 (S-a-0) dxi dF(x)=1 (S-a-1) Xi dxi 2020/9/5 集成电路可测性设计 12

2020/9/5 集成电路可测性设计 12 用布尔差分进行测试生成 1 )( i i dx xdF x 1 )( i i dx xdF x (S-a-0) (S-a-1)

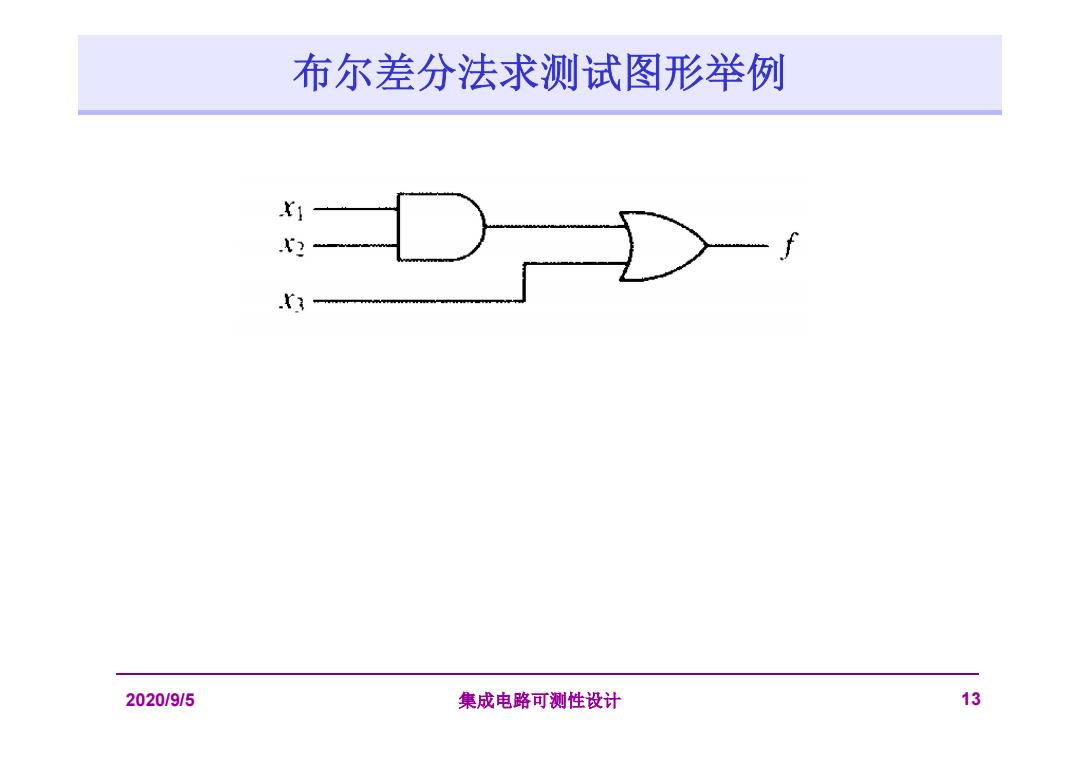

布尔差分法求测试图形举例 xi N2 3 2020/9/5 集成电路可测性设计 13

2020/9/5 集成电路可测性设计 13 布尔差分法求测试图形举例

优缺点 冬优点 -是进行理论研究的必要工具和基础 缺点: -占用存储空间大,当电路复杂时,不存在或难求得 布尔方程式 2020/9/5 集成电路可测性设计 14

2020/9/5 集成电路可测性设计 14 优缺点 优点 是进行理论研究的必要工具和基础 缺点: 占用存储空间大,当电路复杂时,不存在或难求得 布尔方程式

4.3路径敏化法 包子种皮女学 1/966 University of Electronic Science and Technology of China

4.3 路径敏化法

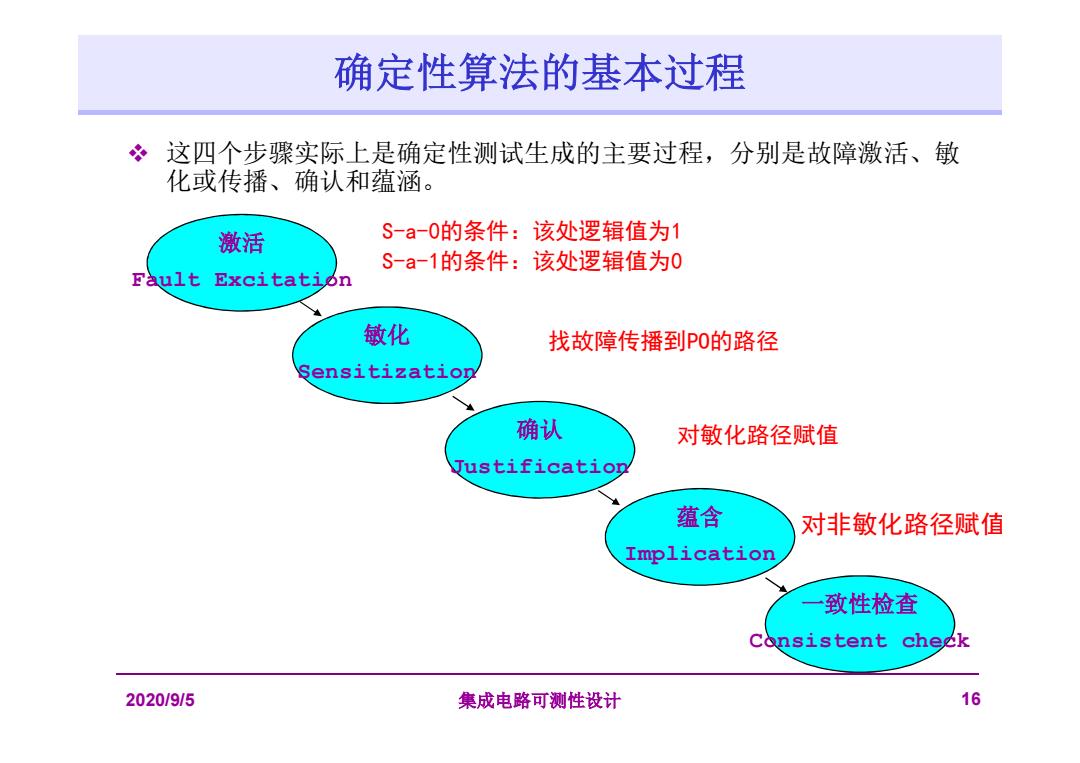

确定性算法的基本过程 冬这四个步骤实际上是确定性测试生成的主要过程,分别是故障激活、敏 化或传播、确认和蕴涵。 激活 S-a-0的条件:该处逻辑值为1 S-a-1的条件:该处逻辑值为0 Fault Excitation 敏化 找故障传播到PO的路径 Sensitization 确认 对敏化路径赋值 Justification 蕴含 对非敏化路径赋值 Implication 致性检查 Consistent check 2020/9/5 集成电路可测性设计 16

2020/9/5 集成电路可测性设计 16 这四个步骤实际上是确定性测试生成的主要过程,分别是故障激活、敏 化或传播、确认和蕴涵。 确定性算法的基本过程 激活 Fault Excitation 敏化 Sensitization 确认 Justification 蕴含 Implication 一致性检查 Consistent check S-a-0的条件:该处逻辑值为1 S-a-1的条件:该处逻辑值为0 找故障传播到PO的路径 对敏化路径赋值 对非敏化路径赋值