图示为由4个边沿D触发器组成的移位寄存器。 串行输入D一 串行输出 -0>CI -Q>CI CP Rp 2006年 新疆大学信息科学与工程学院 <数字电路课题组>

2006年 新疆大学信息科学与工程学院 <数字电路课题组> 图示为由4个边沿D触发器组成的移位寄存器

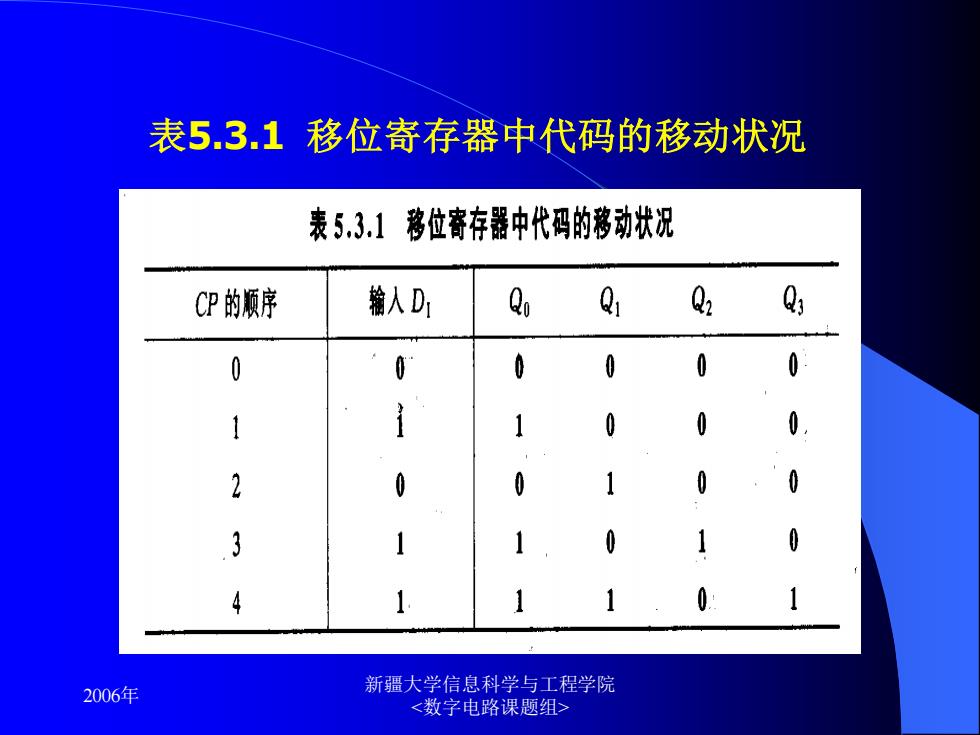

表5.3.1移位寄存器中代码的移动状况 表5,3,1移位寄存器中代码的移动状况 CP的顺序 输人D1 Q Q 0 0 0 0 0 1 1 0 0 0 2 0 0 1 0 0 1 1 0 1. 2006年 新疆大学信息科学与工程学院 <数字电路课题组>

2006年 新疆大学信息科学与工程学院 <数字电路课题组> 表5.3.1 移位寄存器中代码的移动状况

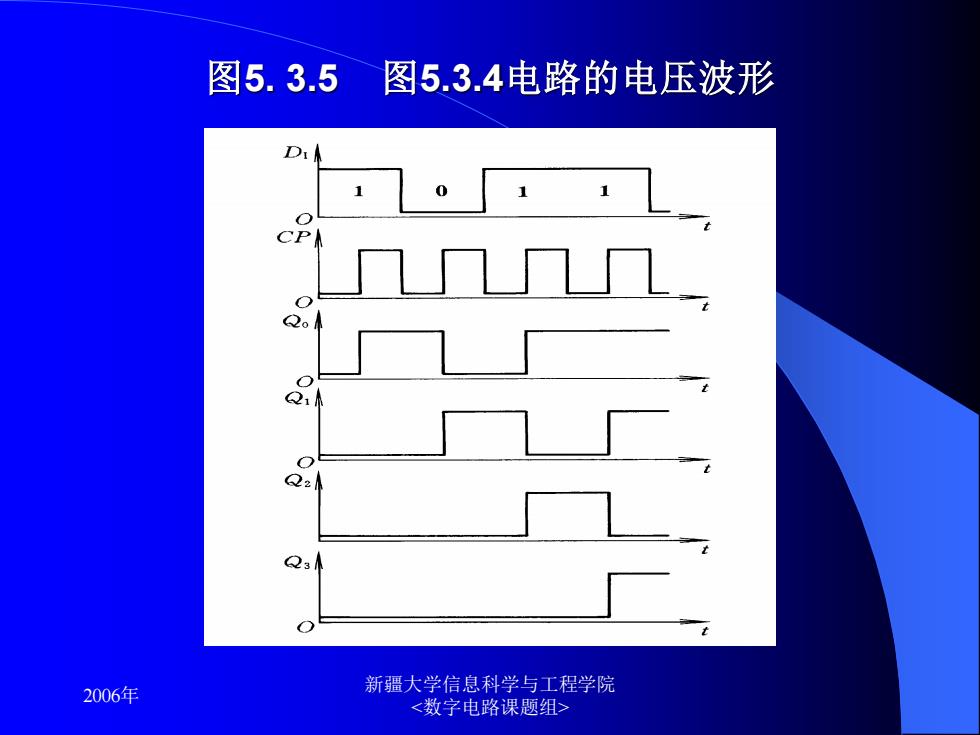

图5.3.5 图5.3.4电路的电压波形 0 Q3 2006年 新疆大学信息科学与工程学院 <数字电路课题组>

2006年 新疆大学信息科学与工程学院 <数字电路课题组> 图5. 3.5 图5.3.4电路的电压波形

图5.3.6 用JK触发器构成的移位寄存器 并 行 输 出 1Q, 1Q2 FF FF FF 串行D Do串行 输入 输出 >C1 >C1 >C1 K 1K 移位CP 脉冲 2006年 新疆大学信息科学与工程学院 <数字电路课题组>

2006年 新疆大学信息科学与工程学院 <数字电路课题组> 图5. 3.6 用JK触发器构成的移位寄存器

图5.3.7 4位双向移位寄存器74LS194A的逻辑图 并 行 输 D。 D D. D D 右移 左移 串行输入 串行输入 s CI CP Qo Qi Q: Q 并 行 输 出 2006年 新疆大学信息科学与工程学院 <数字电路课题组>

2006年 新疆大学信息科学与工程学院 <数字电路课题组> 图5. 3.7 4位双向移位寄存器74LS194A的逻辑图