第五章时序逻辑电路 。5.1概述☑ 。5.2时序逻辑电路的分析方法D 。5.3若干常用的时序逻辑电路 。5.4时序逻辑电路的设计方法) 。5.5时序逻辑电路中的竞争一冒险现象> 2006年 新疆大学信息科学与工程学院 <数字电路课题组>

2006年 新疆大学信息科学与工程学院 <数字电路课题组> 第五章 时序逻辑电路 ⚫ 5.1 概述 ⚫ 5.2 时序逻辑电路的分析方法 ⚫ 5.3 若干常用的时序逻辑电路 ⚫ 5.4 时序逻辑电路的设计方法 ⚫ 5.5 时序逻辑电路中的竞争-冒险现象

5.1概述 定义:时序逻辑电路在任一时刻的输出不仅取决 于当时的输入信号,而且还取决于电路的原来 状态(或者说,还与以前的输入有关 》 电路构成: 存储电路(主要是触发器,必不可少 组合逻辑电路(可选)。 时序逻辑电路的状态是由存储电路来记☑ 和表示的。 2006年 新疆大学信息科学与工程学院 <数字电路课题组> 返回目禄

2006年 新疆大学信息科学与工程学院 <数字电路课题组> 定义:时序逻辑电路在任一时刻的输出不仅取决 于当时的输入信号,而且还取决于电路的原来 状态(或者说,还与以前的输入有关)。 电路构成: ⚫ 存储电路(主要是触发器,必不可少) ⚫ 组合逻辑电路(可选)。 ⚫ 时序逻辑电路的状态是由存储电路来记忆 和表示的。 5.1概述

a 时序电路举例:串行加 Σ S 法器电路 Ci-1 co 串行加法:是指在将两 个多位数相加时,采用 从低位到高位逐位相加 的方式完成相加运算。 C1< CP 2006年 新疆大学信息科学与工程学院 <数字电路课题组>

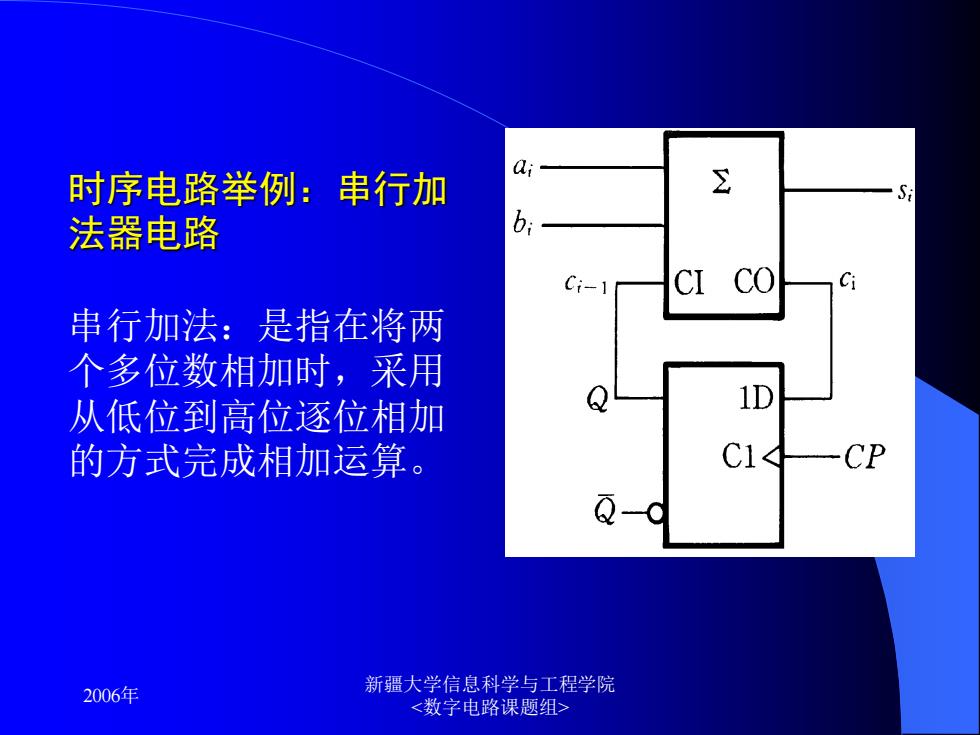

2006年 新疆大学信息科学与工程学院 <数字电路课题组> 时序电路举例:串行加 法器电路 串行加法:是指在将两 个多位数相加时,采用 从低位到高位逐位相加 的方式完成相加运算

时序逻辑电路的结构框图 其中: 组合逻辑电路 XX1,2.,X)代表输 入信号; Y(y1y2,y)代表输 出信号: 21 Z(Z1乙2,.乙)代表存 存储电路 储电路的输入信号: Q(q1,92,.q)代表存 储电路的输出; 2006年 新疆大学信息科学与工程学院 <数字电路课题组>

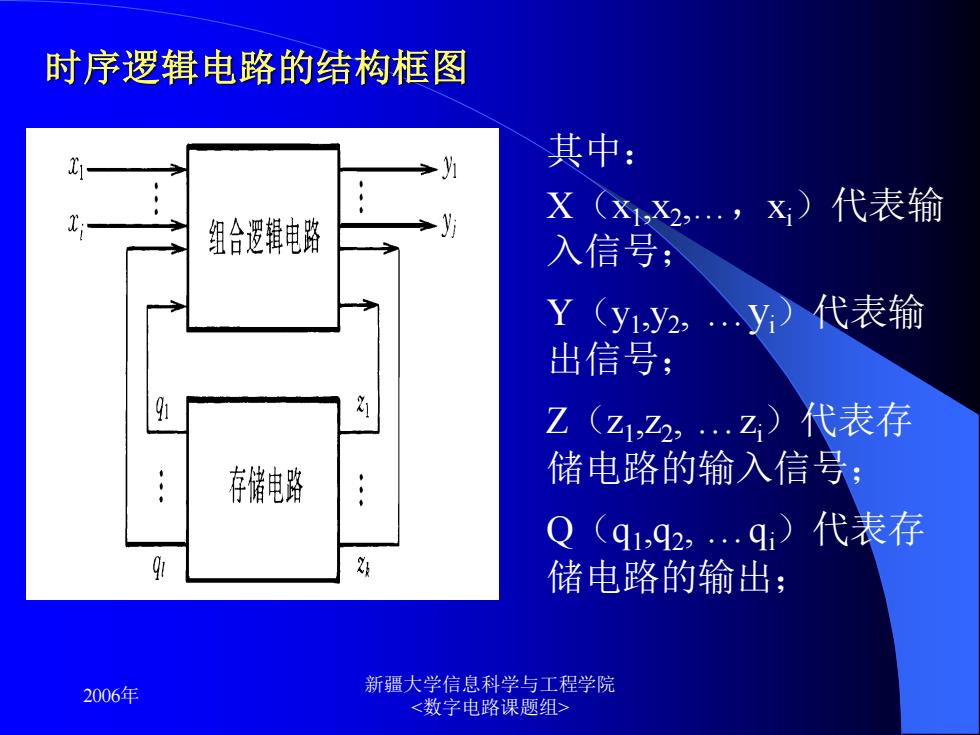

2006年 新疆大学信息科学与工程学院 <数字电路课题组> 时序逻辑电路的结构框图 其中: X(x1 ,x2 ,.,xi)代表输 入信号; Y(y1 ,y2 , .yi)代表输 出信号; Z(z1 ,z2 , .zi)代表存 储电路的输入信号; Q(q1 ,q2 , .qi)代表存 储电路的输出;

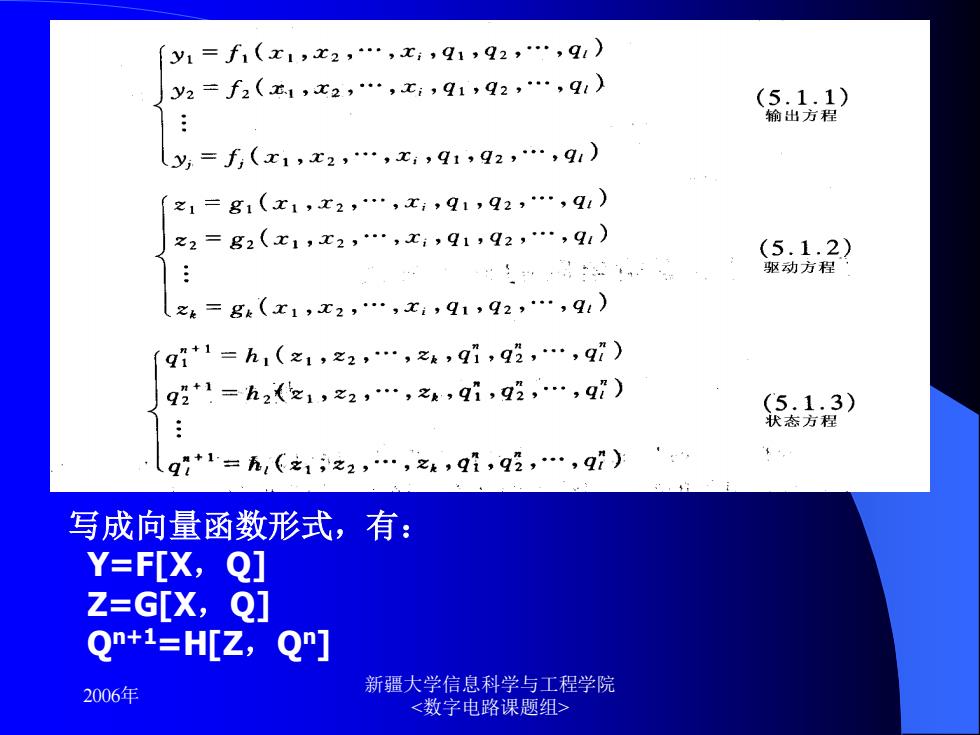

y1=f1(x1,x2,.,x,q1,q2,.,q) y2=f2(x1,x2,.,x,q1,q2,.,91) (5.1.1) 输出方程 y,=f(x1,x2,.,x,q1,q2,.,q1) 之1=81(x1,x2,.,x;,q1,92,q1) z2=g2(x1,x2,.,x;,91,q2,.,91) (5.1.2) 驱动方程 之k=gk(x1,x2,.,x,q1,92,.,91) q1*1=h(之1,之2,.,之4,qi,q2,.,q) g2*1=h2(之1,x2,.,2,q1,92,.,9) (5.1.3) 状态方程 q”+1=,(1之2,.,之,q1,q2,.,9i) 写成向量函数形式,有: Y=F[X,Q] Z=G[X,Q] Q+1=H[Z,Q] 2006年 新疆大学信息科学与工程学院 <数字电路课题组>

2006年 新疆大学信息科学与工程学院 <数字电路课题组> 写成向量函数形式,有: Y=F[X,Q] Z=G[X,Q] Qn+1=H[Z,Qn]