第四章 触发器 4.1概述 4.2触发器的电路结构与动作特点 4.3触发器的逻辑功能及其描述方法 4.4触发器的动态特性 4.5小结 2006年 新疆大学信息科学与工程学院 《数字电路课题组》

2006年 新疆大学信息科学与工程学院 《数字电路课题组》 第四章 触发器 ⚫ 4.1 概述 ⚫ 4.2 触发器的电路结构与动作特点 ⚫ 4.3 触发器的逻辑功能及其描述方法 ⚫ 4.4 触发器的动态特性 ⚫ 4.5小结

4.1概述 触发器是构成时序逻辑电路的基本单元电路。 触发器具有记忆功能,能存储一位二进制数码。 触发器有三个基本特性 (1)有两个稳态,分别表示二进制数码0和1,无外触发时可维 持稳态 (2)根据不同的输入信号可置1或0状态 按触发器的电路结构、触发方式、逻辑功能分别进行介绍。 2006年 新疆大学信息科学与工程学院 《数字电路课题组》

2006年 新疆大学信息科学与工程学院 《数字电路课题组》 4.1 概述 触发器是构成时序逻辑电路的基本单元电路。 触发器具有记忆功能,能存储一位二进制数码。 触发器有三个基本特性: (1)有两个稳态,分别表示二进制数码0和1,无外触发时可维 持稳态; (2)根据不同的输入信号可置1或0状态. 按触发器的电路结构、触发方式、逻辑功能分别进行介绍

4.2触发器的电路结构与动作特点 4.2.1基本R5触发器 与非门实现的基本RS触发器 或非门组成的基本RS触发器 2006年 新疆大学信息科学与工程学院 《数字电路课题组》

2006年 新疆大学信息科学与工程学院 《数字电路课题组》 4.2 触发器的电路结构与动作特点 1 与非门实现的基本RS触发器 2 或非门组成的基本RS触发器 4.2.1 基本RS触发器

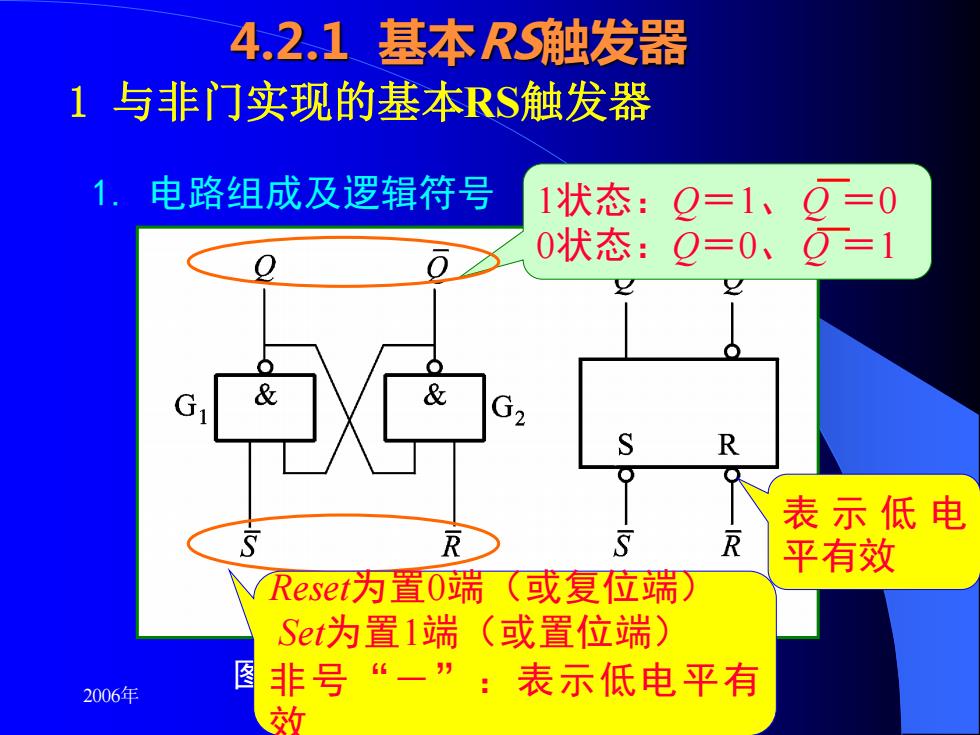

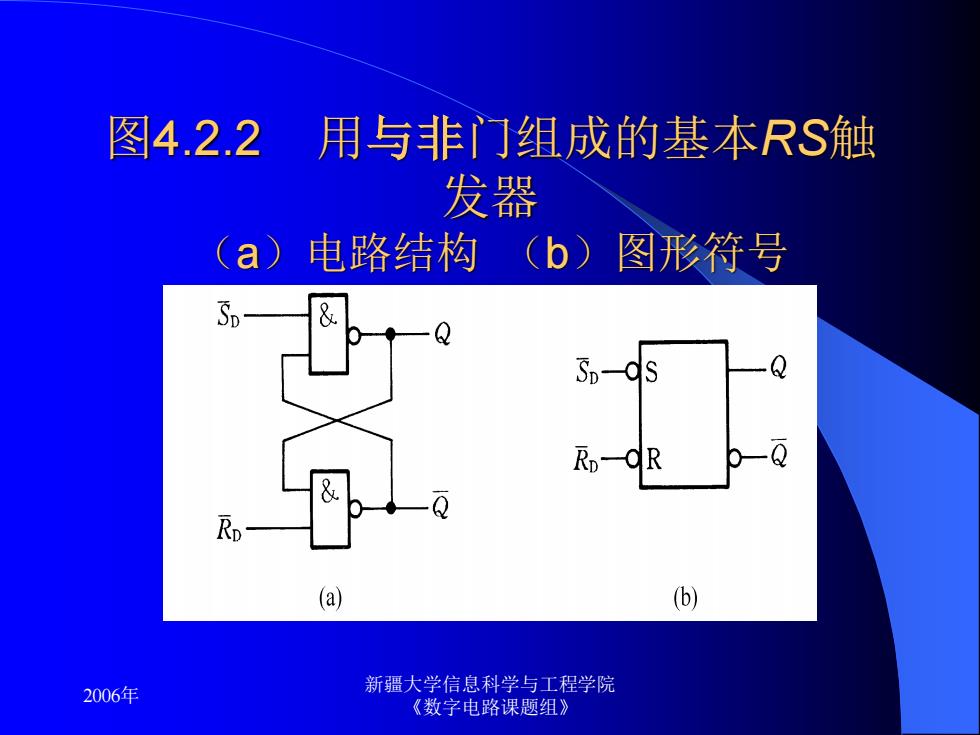

4.2.1基本RS触发器 1与非门实现的基本RS触发器 1.电路组成及逻辑符号 1状态:Q=1、 Q=0 0状态:Q=0、 0=1 & R 表示低电 R 平有效 Reset为置0端(或复位端) Set为置1端(或置位端) 图 2006年 非号“一”:表示低电平有 效

2006年 新疆大学信息科学与工程学院 《数字电路课题组》 4.2.1 基本RS触发器 图4-1 与非门组成的基本RS触发器 (a) 逻辑电路 (b)逻辑符号 1状态:Q=1、Q =0 0状态:Q=0、Q =1 Reset为置0端(或复位端) Set为置1端(或置位端) 非号“-”:表示低电平有 效 表 示 低 电 平有效 1. 电路组成及逻辑符号 1 与非门实现的基本RS触发器

图4.2.2 用与非门组成的基本RS触 发器 (a)电路结构 (b)图形符号 ③dS Rp-R p-Q Rp (a) (b) 2006年 新疆大学信息科学与工程学院 《数字电路课题组》

2006年 新疆大学信息科学与工程学院 《数字电路课题组》 图4.2.2 用与非门组成的基本RS触 发器 (a)电路结构 (b)图形符号