第七章半导体存储器 7.1 概述 7.2 只读存储器 (ROM) 27.3 随机存储器(RAM) D7.4 存储器容量的扩展 7.5用存储器实现组合逻辑函数 )7.6串行存储器 2006年 新疆大学信息科学与工程学院 《数字电路课题组》

2006年 新疆大学信息科学与工程学院 《数字电路课题组》 第七章 半导体存储器 ⚫ 7.1 概述 ⚫ 7.2 只读存储器(ROM) ⚫ 7.3 随机存储器(RAM) ⚫ 7.4 存储器容量的扩展 ⚫ 7.5 用存储器实现组合逻辑函数 ⚫ 7.6 串行存储器

7.1概述 从存、取功能上可以分为只读存储器(Read-Only Memory,简称ROM)和随机存储器(Random Access Memory,简称RAM)两大类。 随机存储器和只读存储器的根本区别在于,正常 工作状态下可以随时向存储器里写入数据或从中读出 数据。 根据所采用的存储单元工作原理的不同,又将随 机存储器分为静态存储器(Static Random Access Memory,简称SRAM)和动态存储器(Dynamic Random Access Memory,简称DRAM) 从制造工艺上有可以把存储器分为双极型和MOS型。 2006年 新疆大学信息科学与工程学院 返回 《数字电路课题组》

2006年 新疆大学信息科学与工程学院 《数字电路课题组》 7.1 概述 从存、取功能上可以分为只读存储器(Read-Only Memory,简称ROM)和随机存储器(Random Access Memory,简称RAM)两大类。 随机存储器和只读存储器的根本区别在于,正常 工作状态下可以随时向存储器里写入数据或从中读出 数据。 根据所采用的存储单元工作原理的不同,又将随 机存储器分为静态存储器(Static Random Access Memory,简称SRAM)和动态存储器(Dynamic Random Access Memory,简称DRAM)。 从制造工艺上有可以把存储器分为双极型和MOS型。 返回

7.2只读存储器 (ROM) 7.2.1掩模只读存储器 址输 地址译码器 存储矩阵 输出缓冲器 数据输出 三态 控制 图7.2.1 ROM的电路结构框图 返回 2006年 新疆大学信息科学与工程学院 《数字电路课题组》

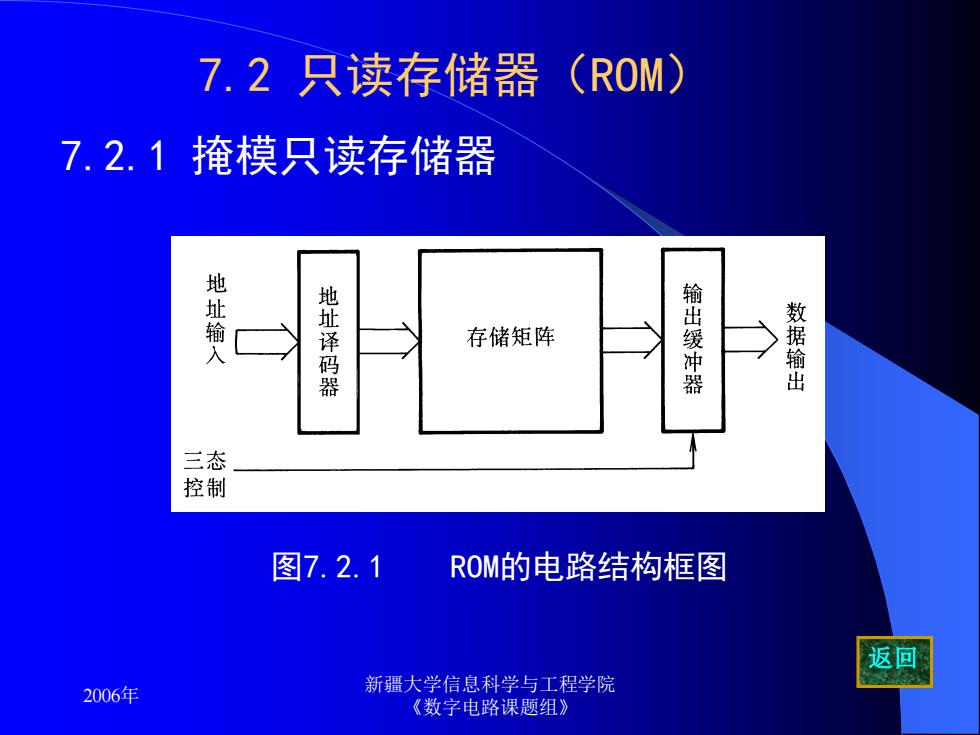

2006年 新疆大学信息科学与工程学院 《数字电路课题组》 7.2 只读存储器(ROM) 7.2.1 掩模只读存储器 图7.2.1 ROM的电路结构框图 返回

7.2.1掩模只读存储器 ROM的电路结构包含存储矩阵、地址译码器和输出 缓冲器三个部分。 存储矩阵由许多存储单元排列而成。存储单元可以 用二极管构成,也可以用二极型三极管或MOS管构成。 每个单元存放1位二值代码(0或1)。每一个或一组存 储单元有一个对应的地址代码。 地址译码器的作用是将输入的地址代码译成相应的 控制信号,利用这个控制信号从存储矩阵中把指定的单 元选出,并把其中的数据送到输出缓冲器。 输出缓冲器的作用有两个,一是能提高存储器的带 负载能力,而是实现对输出状态的三态控制,以便于系 统的总线教联接。 2006年 新疆大学信息科学与工程学院 《数字电路课题组》

2006年 新疆大学信息科学与工程学院 《数字电路课题组》 7.2.1 掩模只读存储器 ROM的电路结构包含存储矩阵、地址译码器和输出 缓冲器三个部分。 存储矩阵由许多存储单元排列而成。存储单元可以 用二极管构成,也可以用二极型三极管或MOS管构成。 每个单元存放1位二值代码(0或1)。每一个或一组存 储单元有一个对应的地址代码。 地址译码器的作用是将输入的地址代码译成相应的 控制信号,利用这个控制信号从存储矩阵中把指定的单 元选出,并把其中的数据送到输出缓冲器。 输出缓冲器的作用有两个,一是能提高存储器的带 负载能力,而是实现对输出状态的三态控制,以便于系 统的总线教联接

地址译码器有n个输入端,有2n个输出信息,每 个输出信息对应一个信息单元,而每个单元存放一 个字,共有2个字(W。、W、W2”-称为字线) 每个字有m位,每位对应从Do、D、 D输出 (称为位线)。 存储器的容量是2n×m(字线×位线)。 ROM中的存储体可以由二极管、三极管和MOS管 来实现。 2006年 新疆大学信息科学与工程学院 《数字电路课题组》

2006年 新疆大学信息科学与工程学院 《数字电路课题组》 地址译码器有n个输入端,有2 n个输出信息,每 个输出信息对应一个信息单元,而每个单元存放一 个字,共有2 n个字(W0、W1、.W2 n -1称为字线)。 每个字有m位,每位对应从D0、D1、.Dm-1输出 (称为位线)。 存储器的容量是2 n×m(字线×位线)。 ROM中的存储体可以由二极管、三极管和MOS管 来实现