第一章绪论 相应的推导过程。 第三章“分数分频频率综合器非线性分析”首先分析了Σ△型分数分频频 率综合器的基本结构,确定了∑△调制器的噪声模型。结合Σ△调制器量化噪声 的模型给出了Σ△型分数分频频率综合器噪声模型并分析了调制器量化噪声到环 路输出相位噪声的转换过程。重点分析了噪声折叠的机制,定量分析了由于电路 非线性导致调制器高频处量化噪声折叠到带内对低频相位噪声的恶化。 第四章“电路设计”主要给出了提出的线性化PFD和分频器链的电路设计。 首先从PFD/CP的δkQk传输曲线入手,分析了电路的非线性的来源,并且介绍 了现有的线性化技术的优缺点,引出了设计的线性PFD电路。其次分析了分频 器链对于相位噪声优化的特点,及分频器的电路设计,最后给出了我们对于优化 分数杂散性能上的设计考虑。 第五章“芯片设计及芯片测试”给出了芯片的照片,及详细的芯片测试结 果,验证了前几章的理论分析及电路设计

第一章 绪论 3 相应的推导过程。 第三章 “分数分频频率综合器非线性分析” 首先分析了 ΣΔ 型分数分频频 率综合器的基本结构,确定了 ΣΔ 调制器的噪声模型。结合 ΣΔ 调制器量化噪声 的模型给出了ΣΔ型分数分频频率综合器噪声模型并分析了调制器量化噪声到环 路输出相位噪声的转换过程。重点分析了噪声折叠的机制,定量分析了由于电路 非线性导致调制器高频处量化噪声折叠到带内对低频相位噪声的恶化。 第四章“电路设计”主要给出了提出的线性化 PFD 和分频器链的电路设计。 首先从 PFD/CP 的 δk-Qk 传输曲线入手,分析了电路的非线性的来源,并且介绍 了现有的线性化技术的优缺点,引出了设计的线性 PFD 电路。其次分析了分频 器链对于相位噪声优化的特点,及分频器的电路设计,最后给出了我们对于优化 分数杂散性能上的设计考虑。 第五章 “芯片设计及芯片测试”给出了芯片的照片,及详细的芯片测试结 果,验证了前几章的理论分析及电路设计

第二章锁相环型频率综合器概述 第二章锁相环型频率综合器概述 2.1引言 频率综合器作为电子系统的“心脏”随着电子技术的发展得到了日益广泛的 应用,并且随着应用的广泛,对频率综合器性能的要求也越来越高。频率综合器 按照实现方式的不同可以分为直接模拟频率综合器、直接数字频率综合器和锁相 环型频率综合器三种。由于锁相环型频率综合器具有锁定捕获范围大、输出信号 频谱纯度高、功耗低、输出频率容易调谐的特点,成为射频接收机中本振时钟产 生的最常用方式。 频率综合器的性能指标包括:频率分辨率、调谐范围、锁定时间、相位噪声 或者时钟抖动、杂散、功耗等几个方面。而且对于不同的应用,对于频率综合器 性能的要求各不相同。通常频率综合器的结构和复杂程度也随着应用系统的不同 要求而存在着差异,本文主要研究用于数字电视接收机的锁相环型频率综合器, 而由于数字电视标准的发展及对本振信号要求的增高,我们主要关注频率综合器 的输出信号的频谱纯度即相位噪声和杂散性能,力求在不影响其他性能的同时对 这两个性能进行优化。 本章主要做了以下工作:首先介绍了整数分频和分数分频频率综合器的基本 结构,并以整数分频器为例讨论了环路的参数设计。接着介绍了相位噪声以及杂 散这两个重要的参数。 2.2整数分频频率综合器的基本结构 锁相环型整数分频频率综合器的结构框图如图21所示2],它主要由鉴频 鉴相器(Phase-Frequency Detector,PFD)、电荷泵(Charge Pump,CP)、环路 滤波器(Loop Filter,LPF)、压控振荡器Voltage Controlled Oscillator,.VCO)和 分频器(Divider)组成。 PFD CP LPF VCO up 鉴频 环路 Tdiv 鉴相器 电荷泵 滤波器 dn Divider 压控振荡器 N分频器 图2-1整数分频频率综合器结构框图 5

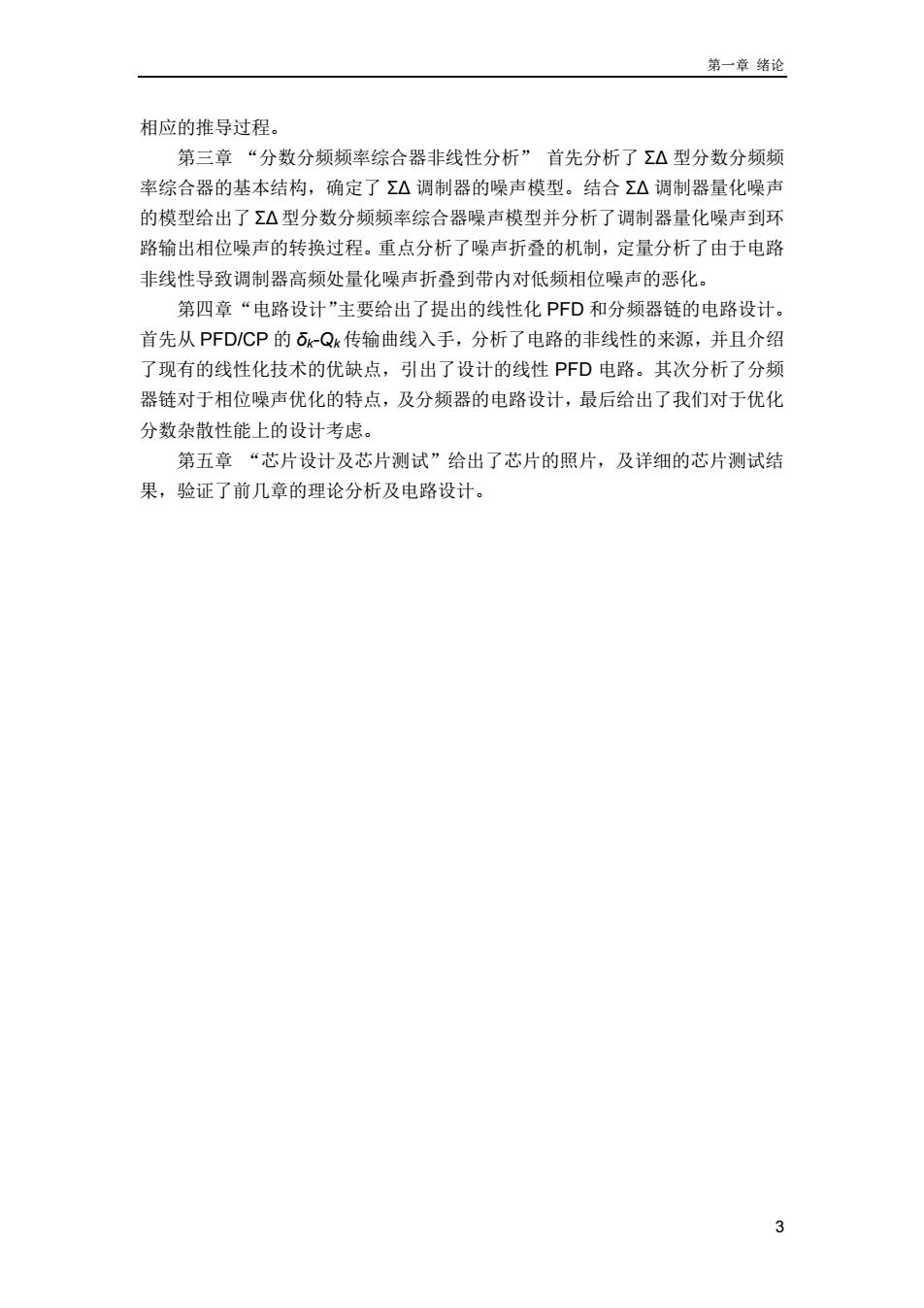

第二章 锁相环型频率综合器概述 5 第二章 锁相环型频率综合器概述 2.1 引言 频率综合器作为电子系统的“心脏”随着电子技术的发展得到了日益广泛的 应用,并且随着应用的广泛,对频率综合器性能的要求也越来越高。频率综合器 按照实现方式的不同可以分为直接模拟频率综合器、直接数字频率综合器和锁相 环型频率综合器三种。由于锁相环型频率综合器具有锁定捕获范围大、输出信号 频谱纯度高、功耗低、输出频率容易调谐的特点,成为射频接收机中本振时钟产 生的最常用方式。 频率综合器的性能指标包括:频率分辨率、调谐范围、锁定时间、相位噪声 或者时钟抖动、杂散、功耗等几个方面。而且对于不同的应用,对于频率综合器 性能的要求各不相同。通常频率综合器的结构和复杂程度也随着应用系统的不同 要求而存在着差异,本文主要研究用于数字电视接收机的锁相环型频率综合器, 而由于数字电视标准的发展及对本振信号要求的增高,我们主要关注频率综合器 的输出信号的频谱纯度即相位噪声和杂散性能,力求在不影响其他性能的同时对 这两个性能进行优化。 本章主要做了以下工作:首先介绍了整数分频和分数分频频率综合器的基本 结构,并以整数分频器为例讨论了环路的参数设计。接着介绍了相位噪声以及杂 散这两个重要的参数。 2.2 整数分频频率综合器的基本结构 锁相环型整数分频频率综合器的结构框图如图 2-1 所示[2],它主要由鉴频 鉴相器(Phase-Frequency Detector,PFD)、电荷泵(Charge Pump,CP)、环路 滤波器(Loop Filter,LPF)、压控振荡器(Voltage Controlled Oscillator,VCO)和 分频器(Divider)组成。 PFD CP LPF up dn Vctrl VCO Divider fdiv fref 鉴频 fvco 鉴相器 电荷泵 环路 滤波器 压控振荡器 N分频器 图 2-1 整数分频频率综合器结构框图

分数分频频率综合器中噪声折叠问题的研究与电路设计 鉴频鉴相器将参考时钟fer和分频器输出时钟fiv的相位进行比较,把两个信 号的相位差转换成时间差控制电荷泵产生误差电流对滤波器进行充放电,滤波器 将误差电流转换成稳定的电压信号控制压控振荡器的输出频率,分频器对VCO 输出信号进行N分频得到fv与参考时钟fef进行比较,各个模块组成一个负反 馈的环路,在负反馈的作用下,fiv与fet的频率和相位最终达到相等的状态,整 个系统达到锁定状态,输出信号频率与输入信号频率满足: fico =N.fret (2-1) 其中N为分频器的分频比,这样我们通过调节N的值就可以得到我们所需 要的输出频率。但由于鉴频鉴相器和电荷泵的开关特性,锁相环型频率综合器实 际上是一个离散系统,为了环路的稳定性,环路带宽一般选择小于参考时钟频率 的十分之一3][4]。在整数分频频率综合器中,由于输出时钟是严格的输入参考 时钟的整数倍,因此fvco的相对精度与fef的相等,一般fet通常源自一个稳定的、 低噪声的石英振荡器。由式(2-1)可知整数分频频率综合器中输出频率的分辨率 由参考时钟fef决定,在GSM系统中,信道间距为200KHz,这就要求频率综 合器至少有200KHz的分辨率,只能选择小的输入参考时钟,因此就需要更加 小的环路带宽,而小的环路带宽会使整个系统的动态响应速度变慢并会使锁定时 间变得很长,这显然不是我们希望的。因为整数分频器存在的环路带宽和分辨率 之间的折衷限制了其在高性能射频接收机领域的应用。 2.3整数分频频率综合器的基本结构 为了打破存在于整数分频频率综合器中的环路带宽和分辨率之间的折衷,分 数分频频率综合器被发明出来[5],整数分频频率综合器在锁定情况下输出信号 fvco和参考时钟信号fret的频率严格相等、fef和分频器时钟fav的边沿严格对齐。 而分数分频频率综合器通过一个多模分频器实现分频比的变化,时而N分频时 而(N+1)分频,在输出信号频率不便的情况下f的频率不停的变化,在锁定的情 况下fer和fv的边沿不是对齐的,时而超前时而滞后,但是fav的平均值是和fef 对齐的。所以分数分频频率综合器实现的是一种“动态锁定”。 2.3.1累加器型分数分频频率综合器 图2-2是一种经典的基于累加器(Accumulator)的分数分频频率综合器的结 构框图。它采用了一个累加器来实现分频比的动态选择。累加器的输入是分频比 中的小数部分,我们可以楚的看到累加器的残余量(residue)每经过一个参考时钟 信号周期Trer增加a(小数分频比),当累加器发生溢出时产生一个进位信号(carry out)来选择分频比从N变为N+1,在经过一个Tet后分频比变回为N。这样就实 现了分数分频的效果: 6

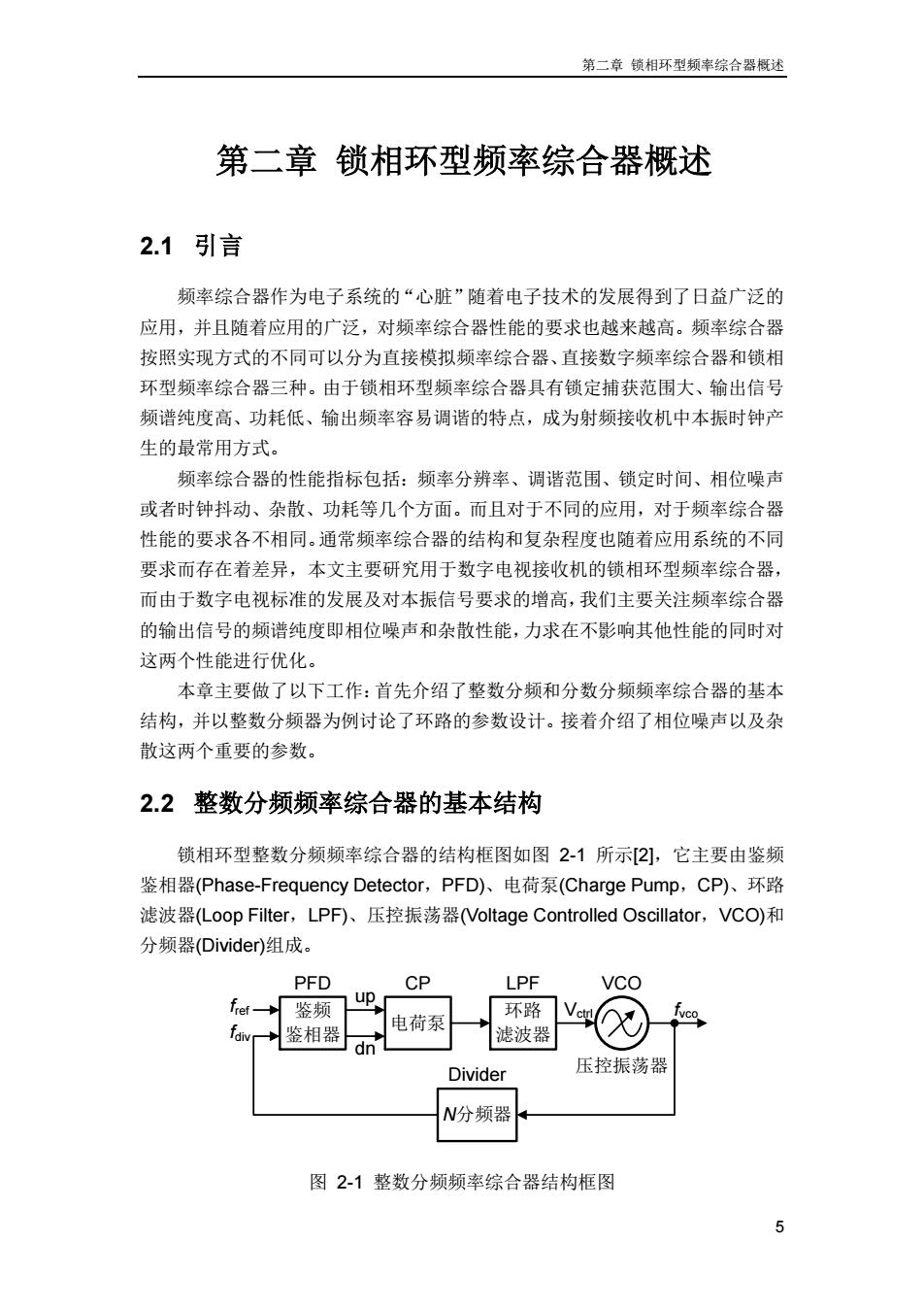

分数分频频率综合器中噪声折叠问题的研究与电路设计 6 鉴频鉴相器将参考时钟 fref 和分频器输出时钟 fdiv的相位进行比较,把两个信 号的相位差转换成时间差控制电荷泵产生误差电流对滤波器进行充放电,滤波器 将误差电流转换成稳定的电压信号控制压控振荡器的输出频率,分频器对 VCO 输出信号进行 N 分频得到 fdiv与参考时钟 fref 进行比较,各个模块组成一个负反 馈的环路,在负反馈的作用下,fdiv与 fref 的频率和相位最终达到相等的状态,整 个系统达到锁定状态,输出信号频率与输入信号频率满足: vco ref f N f (2-1) 其中 N 为分频器的分频比,这样我们通过调节 N 的值就可以得到我们所需 要的输出频率。但由于鉴频鉴相器和电荷泵的开关特性,锁相环型频率综合器实 际上是一个离散系统,为了环路的稳定性,环路带宽一般选择小于参考时钟频率 的十分之一[3][4]。在整数分频频率综合器中,由于输出时钟是严格的输入参考 时钟的整数倍,因此 fvco的相对精度与 fref 的相等,一般 fref 通常源自一个稳定的、 低噪声的石英振荡器。由式 (2-1)可知整数分频频率综合器中输出频率的分辨率 由参考时钟 fref 决定,在 GSM 系统中,信道间距为 200 KHz,这就要求频率综 合器至少有 200 KHz 的分辨率,只能选择小的输入参考时钟,因此就需要更加 小的环路带宽,而小的环路带宽会使整个系统的动态响应速度变慢并会使锁定时 间变得很长,这显然不是我们希望的。因为整数分频器存在的环路带宽和分辨率 之间的折衷限制了其在高性能射频接收机领域的应用。 2.3 整数分频频率综合器的基本结构 为了打破存在于整数分频频率综合器中的环路带宽和分辨率之间的折衷,分 数分频频率综合器被发明出来[5],整数分频频率综合器在锁定情况下输出信号 fvco 和参考时钟信号 fref 的频率严格相等、fref 和分频器时钟 fdiv 的边沿严格对齐。 而分数分频频率综合器通过一个多模分频器实现分频比的变化,时而 N 分频时 而(N+1)分频,在输出信号频率不便的情况下 fdiv 的频率不停的变化,在锁定的情 况下 fref 和 fdiv的边沿不是对齐的,时而超前时而滞后,但是 fdiv的平均值是和 fref 对齐的。所以分数分频频率综合器实现的是一种“动态锁定”。 2.3.1 累加器型分数分频频率综合器 图 2-2 是一种经典的基于累加器(Accumulator)的分数分频频率综合器的结 构框图。它采用了一个累加器来实现分频比的动态选择。累加器的输入是分频比 中的小数部分,我们可以楚的看到累加器的残余量(residue)每经过一个参考时钟 信号周期 Tref 增加 α(小数分频比),当累加器发生溢出时产生一个进位信号(carry out)来选择分频比从 N 变为 N+1,在经过一个 Tref 后分频比变回为 N。这样就实 现了分数分频的效果:

第二章锁相环型频率综合器概述 fico =(N+a)-fet (2-2) 同时打破了环路带宽和参考时钟之间的折衷关系,参考时钟可以不用考虑输 出信号分辨率来进行选择,带宽也就可以根据相位噪声和锁定时间来选择,这样 就在设计上有了较大的自由度。 几几fref e(f) PFD Charge LPF nu几fav Pump VCO Divider (NIN+1) carry out Fraction (a)- Accumulator residue 图2-2基于累加器的分数分频频率综合器结构框图 但分数分频频率综合器在实现分数分频的同时不可避免的引入了量化噪声 (Quantization Noise)。我们通过图2-3来解释量化噪声所带来的问题。 fvco(⑤ faiv(f) frer(f) uT几几TΠTTTΠ e() 可o22 phase error residue carry out Divide value 444544454445 图2-3分频比在4.25时分数分频频率综合器中的量化噪声 我们以4.25分频为例,当环路处于锁定状态时,输出信号co=4.25·fef, 但是在前三个周期内为4分频,分频器输出信号Tv周期会稍稍小于参考时钟 信号周期Te,在环路负反馈的作用下,相应的相位误差也在逐渐累积,在第四 个参考时钟周期到来时累加器产生进位信号,分频比变为5,鉴频鉴相器产生一 个宽的脉冲信号来纠正前面积累的相位误差,这样在每四个参考时钟周期就会产 7

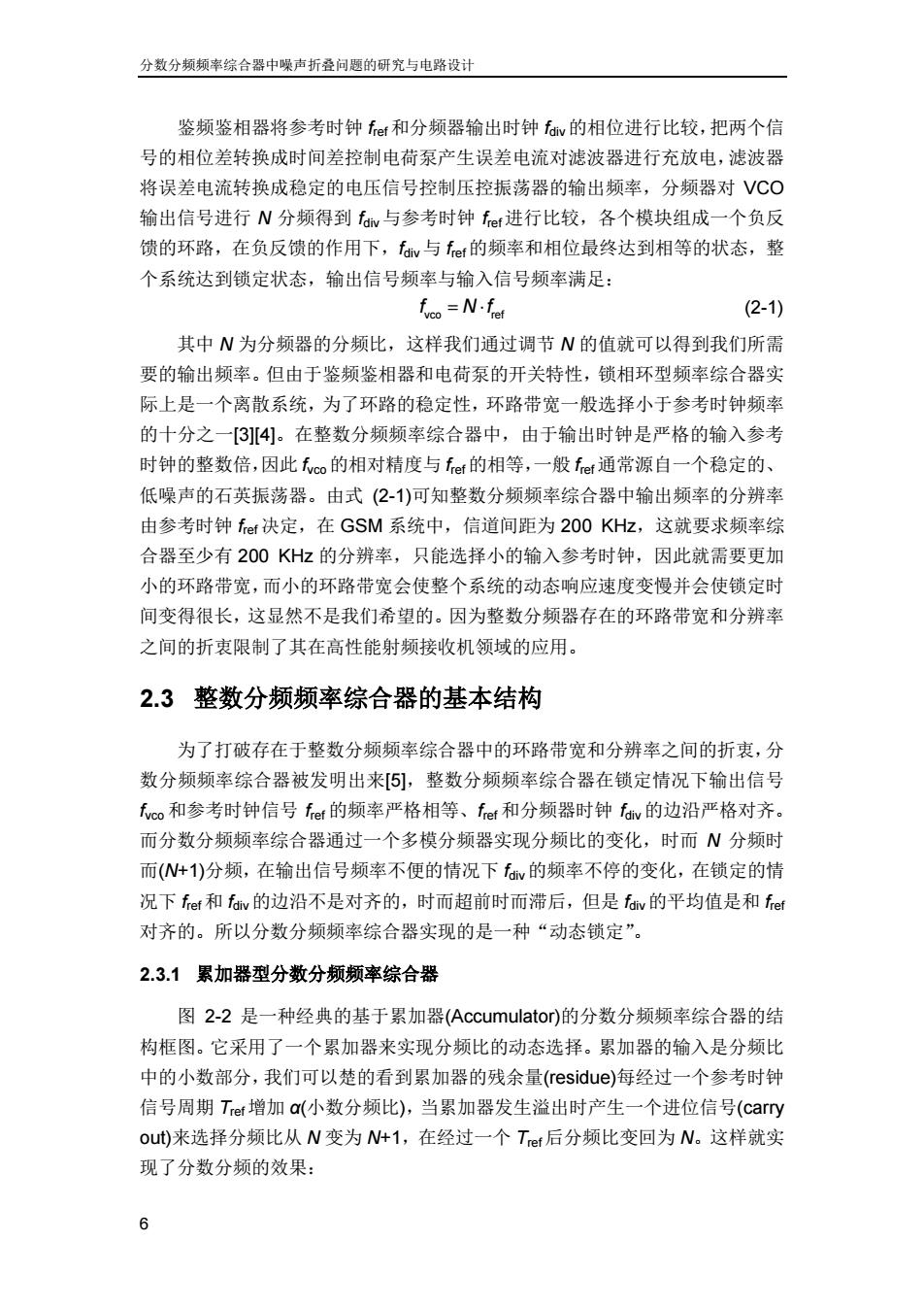

第二章 锁相环型频率综合器概述 7 vco ref f N ( ) α f (2-2) 同时打破了环路带宽和参考时钟之间的折衷关系,参考时钟可以不用考虑输 出信号分辨率来进行选择,带宽也就可以根据相位噪声和锁定时间来选择,这样 就在设计上有了较大的自由度。 PFD Charge Pump LPF e(t) vctrl VCO Divider (N/N+1) fdiv fref fvco Fraction (α) Accumulator carry out residue 图 2-2 基于累加器的分数分频频率综合器结构框图 但分数分频频率综合器在实现分数分频的同时不可避免的引入了量化噪声 (Quantization Noise)。我们通过图 2-3 来解释量化噪声所带来的问题。 δ[1] δ[2] δ[2] 4 4 4 5 4 4 4 5 4 4 4 5 Tvco fvco(t) fdiv(t) fref(t) e(t) phase error residue carry out Divide value 图 2-3 分频比在 4.25 时分数分频频率综合器中的量化噪声 我们以 4.25 分频为例,当环路处于锁定状态时,输出信号 fvco=4.25·fref, 但是在前三个周期内为 4 分频,分频器输出信号 Tvco 周期会稍稍小于参考时钟 信号周期 Tref,在环路负反馈的作用下,相应的相位误差也在逐渐累积,在第四 个参考时钟周期到来时累加器产生进位信号,分频比变为 5,鉴频鉴相器产生一 个宽的脉冲信号来纠正前面积累的相位误差,这样在每四个参考时钟周期就会产

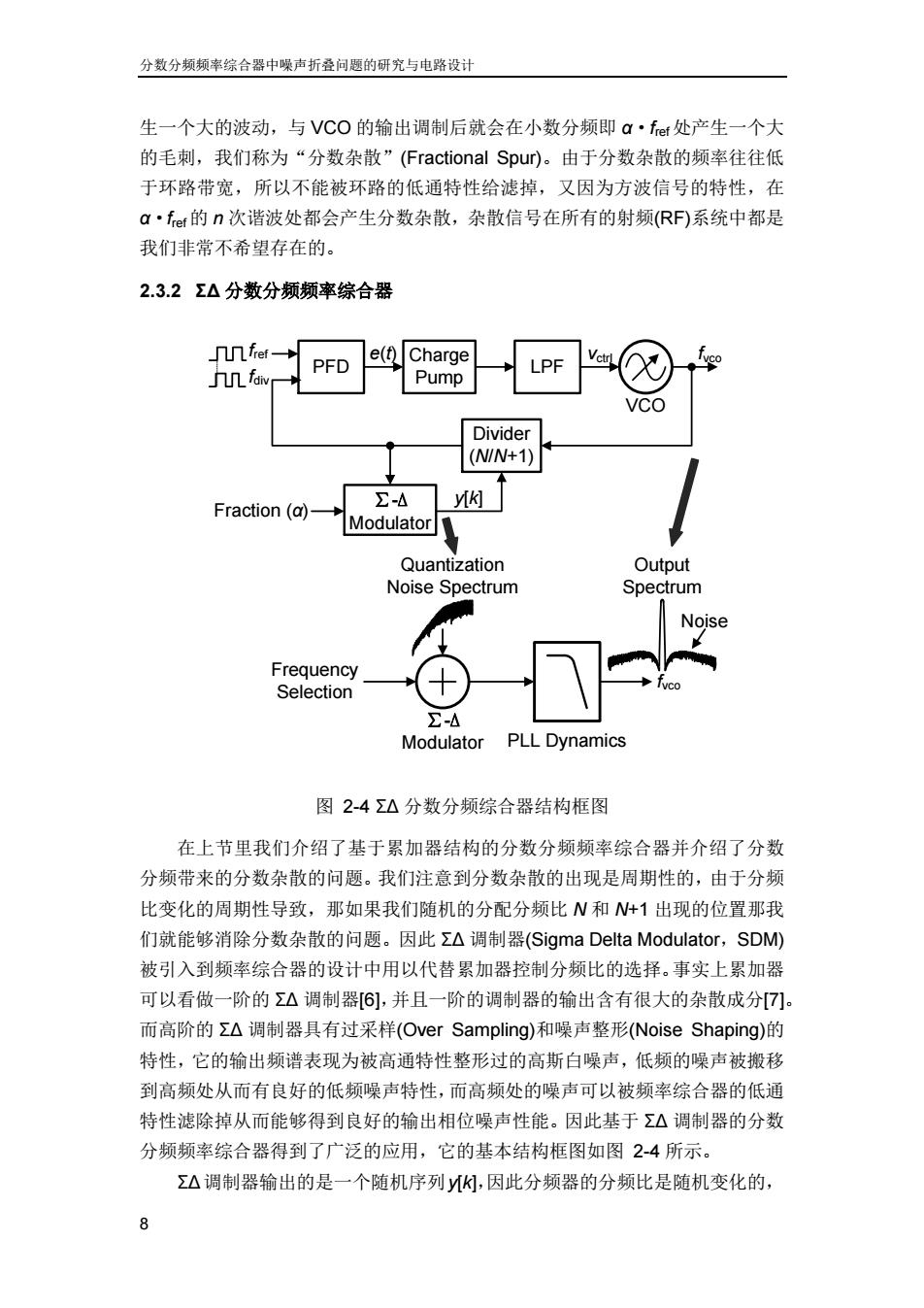

分数分频频率综合器中噪声折叠问题的研究与电路设计 生一个大的波动,与VCO的输出调制后就会在小数分频即a·fef处产生一个大 的毛刺,我们称为“分数杂散”(Fractional Spur)。由于分数杂散的频率往往低 于环路带宽,所以不能被环路的低通特性给滤掉,又因为方波信号的特性,在 a·fer的n次谐波处都会产生分数杂散,杂散信号在所有的射频(RF)系统中都是 我们非常不希望存在的。 2.3.2Σ△分数分频频率综合器 几几fef e(t) PFD Charge LPF Pump VCo Divider (NIN+1) Fraction (a) ∑-A 内 Modulator Quantization Output Noise Spectrum Spectrum Noise Frequency Selection ∑-A Modulator PLL Dynamics 图2-4∑△分数分频综合器结构框图 在上节里我们介绍了基于累加器结构的分数分频频率综合器并介绍了分数 分频带来的分数杂散的问题。我们注意到分数杂散的出现是周期性的,由于分频 比变化的周期性导致,那如果我们随机的分配分频比N和N+1出现的位置那我 们就能够消除分数杂散的问题。因此Σ△调制器(Sigma Delta Modulator,SDM) 被引入到频率综合器的设计中用以代替累加器控制分频比的选择。事实上累加器 可以看做一阶的Σ△调制器6],并且一阶的调制器的输出含有很大的杂散成分[7]。 而高阶的Σ△调制器具有过采样(Over Sampling)和噪声整形(Noise Shaping)的 特性,它的输出频谱表现为被高通特性整形过的高斯白噪声,低频的噪声被搬移 到高频处从而有良好的低频噪声特性,而高频处的噪声可以被频率综合器的低通 特性滤除掉从而能够得到良好的输出相位噪声性能。因此基于Σ△调制器的分数 分频频率综合器得到了广泛的应用,它的基本结构框图如图24所示。 Σ△调制器输出的是一个随机序列yK],因此分频器的分频比是随机变化的, 8

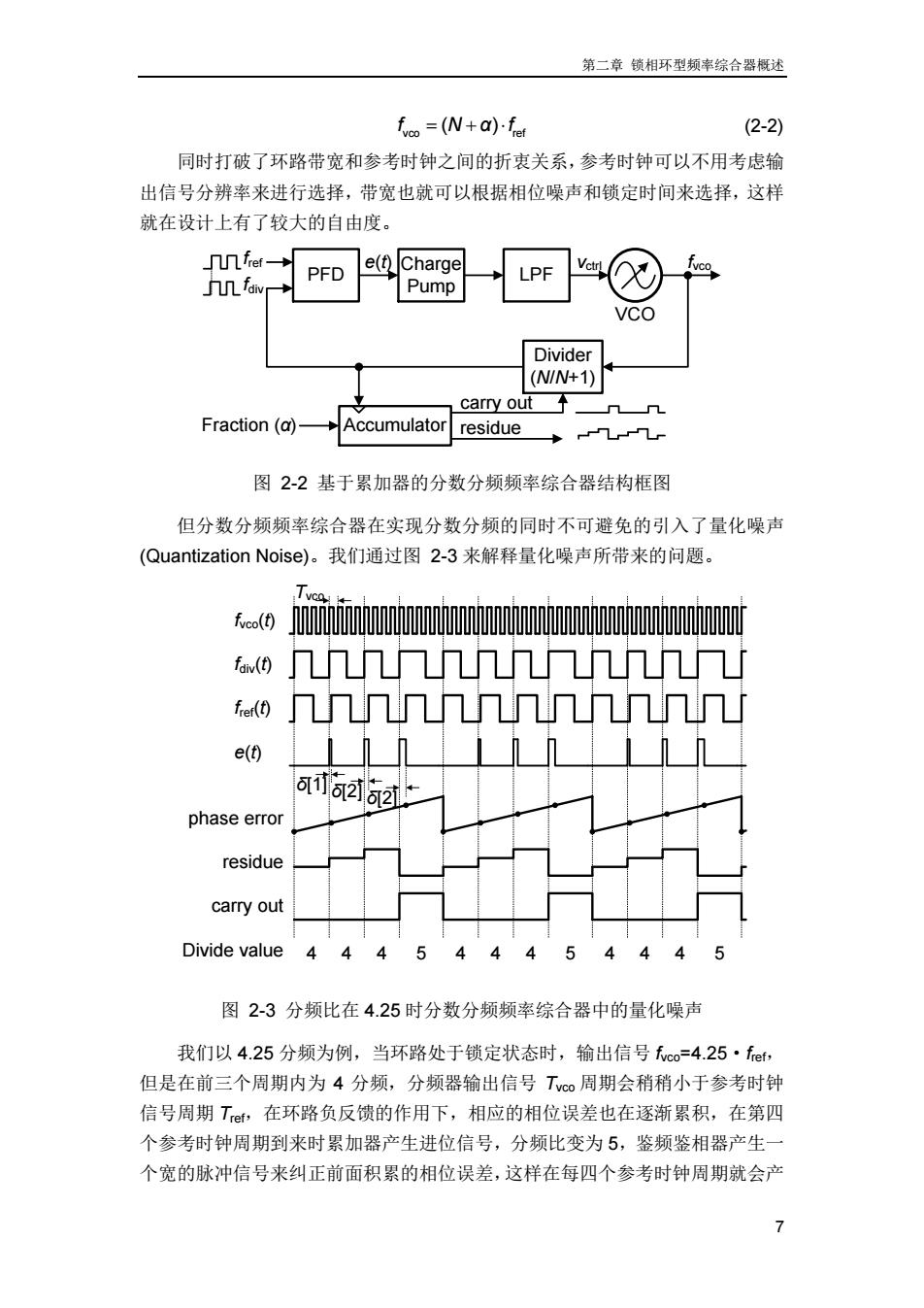

分数分频频率综合器中噪声折叠问题的研究与电路设计 8 生一个大的波动,与 VCO 的输出调制后就会在小数分频即 α·fref 处产生一个大 的毛刺,我们称为“分数杂散”(Fractional Spur)。由于分数杂散的频率往往低 于环路带宽,所以不能被环路的低通特性给滤掉,又因为方波信号的特性,在 α·fref 的 n 次谐波处都会产生分数杂散,杂散信号在所有的射频(RF)系统中都是 我们非常不希望存在的。 2.3.2 ΣΔ 分数分频频率综合器 PFD Charge Pump LPF vctrl VCO fdiv fref fvco ∑-∆ Modulator y[k] e(t) Divider (N/N+1) Fraction (α) ∑-∆ Modulator Quantization Noise Spectrum PLL Dynamics fvco Output Spectrum Noise Frequency Selection 图 2-4 ΣΔ 分数分频综合器结构框图 在上节里我们介绍了基于累加器结构的分数分频频率综合器并介绍了分数 分频带来的分数杂散的问题。我们注意到分数杂散的出现是周期性的,由于分频 比变化的周期性导致,那如果我们随机的分配分频比 N 和 N+1 出现的位置那我 们就能够消除分数杂散的问题。因此 ΣΔ 调制器(Sigma Delta Modulator,SDM) 被引入到频率综合器的设计中用以代替累加器控制分频比的选择。事实上累加器 可以看做一阶的 ΣΔ 调制器[6],并且一阶的调制器的输出含有很大的杂散成分[7]。 而高阶的 ΣΔ 调制器具有过采样(Over Sampling)和噪声整形(Noise Shaping)的 特性,它的输出频谱表现为被高通特性整形过的高斯白噪声,低频的噪声被搬移 到高频处从而有良好的低频噪声特性,而高频处的噪声可以被频率综合器的低通 特性滤除掉从而能够得到良好的输出相位噪声性能。因此基于 ΣΔ 调制器的分数 分频频率综合器得到了广泛的应用,它的基本结构框图如图 2-4 所示。 ΣΔ调制器输出的是一个随机序列y[k],因此分频器的分频比是随机变化的