复旦大学硕士学位论文 绪论 第一章绪论 1.1研究背景: 上世纪九十年代,欧洲电信标准研究院ETSI(Europe Telecommunication Standard Institue)最先提出DVB系列数字电视标准,随后美国和日本也相继出台 了各自的数字电视标准。2006年,随着中国地面数字电视传输技术标准 DMB-T/H(Terrestrial Digital Multimedia TV/Handle Broadcasting)的官方发布,数 字电视广播技术呈现更加迅猛的发展势头,其中包括复旦微纳推出的“中视一号” 数字信号解调芯片以及海尔推出的“爱国者”系列MPEG解码芯片。但是单片集 成的电缆电视调谐器(Cable TV Tuner)芯片却还是完全依赖进口.这主要是因为电 视信号宽频谱和低噪声性能的要求使得调谐器中的某些电路在标准CMOS工艺 下设计实现难度很大,其中主要包括宽带低噪声放大器和低相位噪声、低杂散的 频率综合器的设计和实现。本文的研究重点就是标准CMOS工艺下低相位噪声、 低杂散的频率综合器的设计和实现。 在采用二次变频技术的电缆电视调谐器中,下变频混频器要求本振信号具有 200MHz左右的频率调谐范围,输出信号正交,同时要具有较低的相位噪声 (-80dBc@10KHz,-100dBc@100KHz,-130dBc@1MHz)2.。因此往往只有采用 GaAs或BiCMOS工艺实现。随着CMOS工艺的发展以及研究人员的努力,设计低 相位噪声的压控振荡器已经成为可能,但是要想同时实现很好的杂散抑制性能、 较低的带内相位噪声以及单片集成却具有很大的挑战性,这需要我们改进现有的 电路或者提出新的电路结构。然而现有的商业软件不可能精确仿真频率综合器系 统的相位噪声以及杂散性能,使得我们在设计过程中不可能利用仿真手段来验证 所设计的电路是否符合系统要求,因此在电路设计之前必须建立精确的相位噪声 分析模型来对整个频率综和器系统的噪声进行估计。所以,本论文将着重于频率 综合器相位噪声分析模型的建立和低杂散、低相位噪声频率综合器的设计。 1.2论文的主要工作和贡献: 本论文的主要工作和贡献包括: 1)通过分析DVB-CT标准的射频电视调谐器接收机架构,得到频率综合器 的性能指标,根据性能指标进而确定频率综合器的系统架构。在几种分数杂散抑 制技术的分析基础上,最终选取sigma-delta结构的分数分频频率综合器结构。 2)对四阶环路实现了基于稳定性优化的环路分析与设计,并且采用加倍减 半电流补偿单元使环路的稳定性得到拓展。归纳总结了四阶锁相环路参数设计的 具体流程。 3)详细分析了传统全差分电荷泵电路和共模负反馈电路中存在的缺陷,提出

复旦大学硕士学位论文 绪论 第一章 绪论 1.1 研究背景: 上世纪九十年代,欧洲电信标准研究院ETSI(Europe Telecommunication Standard Institue)最先提出DVB系列数字电视标准,随后美国和日本也相继出台 了各自的数字电视标准。2006 年,随着中国地面数字电视传输技术标准 DMB-T/H(Terrestrial Digital Multimedia TV/Handle Broadcasting)的官方发布[1],数 字电视广播技术呈现更加迅猛的发展势头,其中包括复旦微纳推出的“中视一号” 数字信号解调芯片以及海尔推出的“爱国者”系列MPEG解码芯片。但是单片集 成的电缆电视调谐器(Cable TV Tuner)芯片却还是完全依赖进口。这主要是因为电 视信号宽频谱和低噪声性能的要求使得调谐器中的某些电路在标准CMOS工艺 下设计实现难度很大,其中主要包括宽带低噪声放大器和低相位噪声、低杂散的 频率综合器的设计和实现。本文的研究重点就是标准CMOS工艺下低相位噪声、 低杂散的频率综合器的设计和实现。 在采用二次变频技术的电缆电视调谐器中,下变频混频器要求本振信号具有 200MHz左右的频率调谐范围,输出信号正交,同时要具有较低的相位噪声 (-80dBc@10KHz,-100dBc@100KHz,-130dBc@1MHz)[2,3]。因此往往只有采用 GaAs或BiCMOS工艺实现。随着CMOS工艺的发展以及研究人员的努力,设计低 相位噪声的压控振荡器已经成为可能,但是要想同时实现很好的杂散抑制性能、 较低的带内相位噪声以及单片集成却具有很大的挑战性,这需要我们改进现有的 电路或者提出新的电路结构。然而现有的商业软件不可能精确仿真频率综合器系 统的相位噪声以及杂散性能,使得我们在设计过程中不可能利用仿真手段来验证 所设计的电路是否符合系统要求,因此在电路设计之前必须建立精确的相位噪声 分析模型来对整个频率综和器系统的噪声进行估计。所以,本论文将着重于频率 综合器相位噪声分析模型的建立和低杂散、低相位噪声频率综合器的设计。 1.2 论文的主要工作和贡献: 本论文的主要工作和贡献包括: 1) 通过分析 DVB-C/T 标准的射频电视调谐器接收机架构,得到频率综合器 的性能指标,根据性能指标进而确定频率综合器的系统架构。在几种分数杂散抑 制技术的分析基础上,最终选取 sigma-delta 结构的分数分频频率综合器结构。 2) 对四阶环路实现了基于稳定性优化的环路分析与设计,并且采用加倍-减 半电流补偿单元使环路的稳定性得到拓展。归纳总结了四阶锁相环路参数设计的 具体流程。 3) 详细分析了传统全差分电荷泵电路和共模负反馈电路中存在的缺陷,提出 1

复旦大学硕士学位论文 绪论 了一种高匹配性的宽输出摆幅全差分电荷泵电路及轨到轨输入共模电平范围的 共模负反馈电路,同时又设计了一种输出信号完全对称的鉴频鉴相器来有效地克 服时钟效应对电荷泵性能的影响。采用新电路结构的频率综合器的杂散抑制性能 可以比传统结构提高了18dB。 4)分析并推导了各个模块电路的输出等效噪声的解析表达式,计算结果和测 试结果相当接近,从而验证了我们噪声分析模型的准确性。 5)提出了一种新型测试方法,采用此方法可以精确地测出电荷泵等所有模块 电路的相位噪声贡献。 1.3论文的组织结构: 第二章,“频率综合器架构的确定及环路参数设计”。介绍了频率综合器性能 指标和体系架构的确定。详细阐述了如何应用基于稳定性优化的环路设计方法来 设计四阶锁相系统。 第三章,“电路设计”。详细介绍了高匹配性宽输出摆幅全差分电荷泵、输出 信号完全对称的鉴频鉴相器以及三阶无源环路滤波器等电路的设计。 第四章,“频率综合器相位噪声分析及优化”。分析推导了各模块电路的等效 输出噪声、噪声传递函数以及频率综合器的相位噪声模型,依此模型进行噪声优 化设计。 第五章,“芯片实现与测试”。在SMIC0.18 um Mixed-signal1P6 M CMOS 工艺下设计并实现了sigma-delta结构的分数分频频率综合器电路,并完成对芯 片的测试。 第六章,“总结与未来展望”。给出对本论文的总结与对未来的展望。 参考文献 [1]DMB-TH地面数字电视传输技术白皮书(第二版)2006年5月 [2]Microtune Inc.MicrotunerTM2040 Data Sheet. [3]Motorola Inc.Silicon Tuner MC44C800/MC44C801 Fact Sheet 2

复旦大学硕士学位论文 绪论 了一种高匹配性的宽输出摆幅全差分电荷泵电路及轨到轨输入共模电平范围的 共模负反馈电路,同时又设计了一种输出信号完全对称的鉴频鉴相器来有效地克 服时钟效应对电荷泵性能的影响。采用新电路结构的频率综合器的杂散抑制性能 可以比传统结构提高了 18dB。 4) 分析并推导了各个模块电路的输出等效噪声的解析表达式,计算结果和测 试结果相当接近,从而验证了我们噪声分析模型的准确性。 5) 提出了一种新型测试方法,采用此方法可以精确地测出电荷泵等所有模块 电路的相位噪声贡献。 1.3 论文的组织结构: 第二章,“频率综合器架构的确定及环路参数设计”。介绍了频率综合器性能 指标和体系架构的确定。详细阐述了如何应用基于稳定性优化的环路设计方法来 设计四阶锁相系统。 第三章,“电路设计”。详细介绍了高匹配性宽输出摆幅全差分电荷泵、输出 信号完全对称的鉴频鉴相器以及三阶无源环路滤波器等电路的设计。 第四章,“频率综合器相位噪声分析及优化”。分析推导了各模块电路的等效 输出噪声、噪声传递函数以及频率综合器的相位噪声模型,依此模型进行噪声优 化设计。 第五章,“芯片实现与测试”。在 SMIC 0.18µm Mixed-signal 1P6M CMOS 工艺下设计并实现了 sigma-delta 结构的分数分频频率综合器电路,并完成对芯 片的测试。 第六章,“总结与未来展望”。给出对本论文的总结与对未来的展望。 参考文献 [1] DMB-TH 地面数字电视传输技术白皮书(第二版) 2006 年 5 月 [2] Microtune Inc.MicrotunerTM 2040 Data Sheet. [3] Motorola Inc.Silicon Tuner MC44C800/MC44C801 Fact Sheet. 2

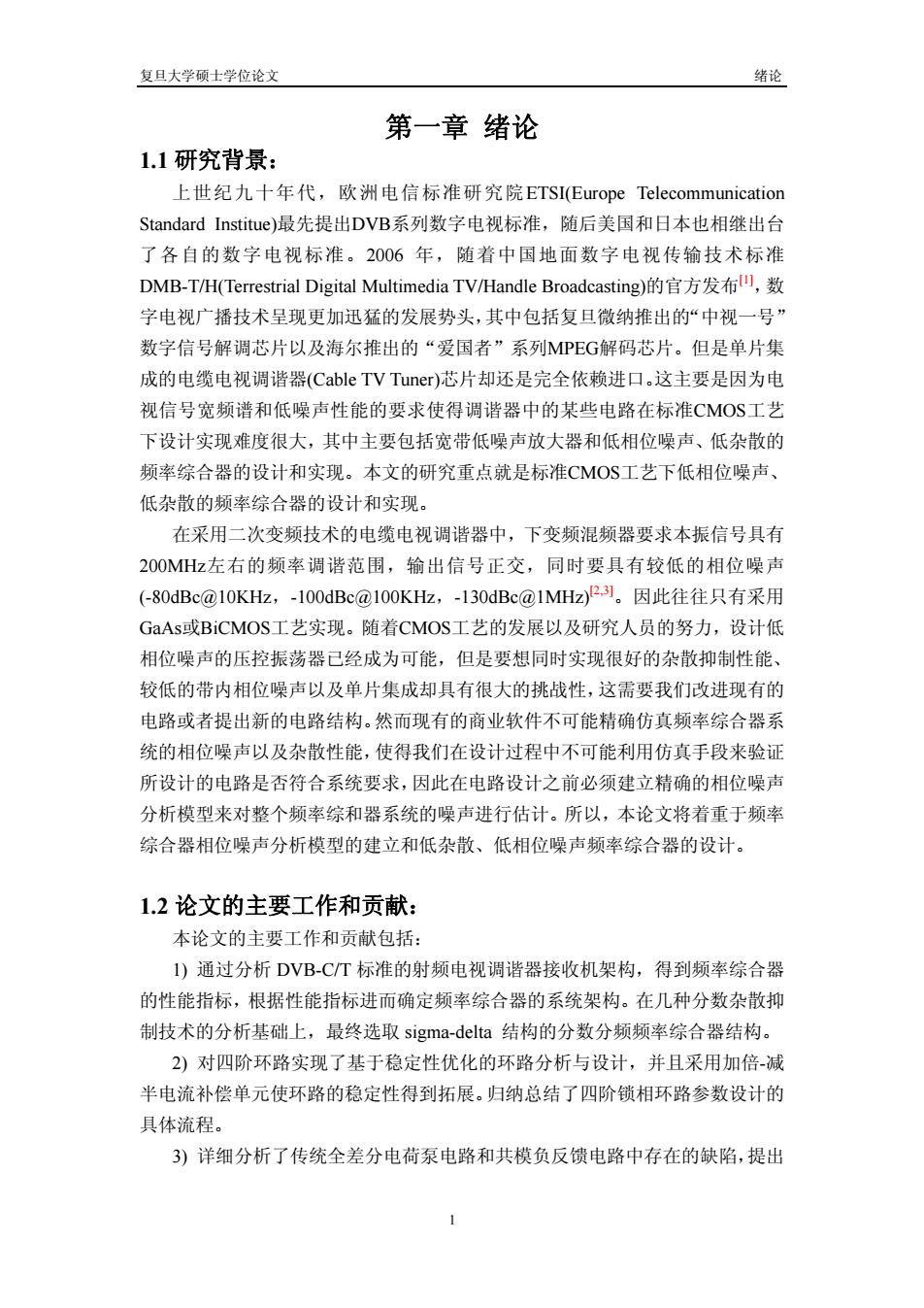

复旦大学硕士学位论文 第二章频率综合器架构的确定及环路参数设计 第二章频率综合器架构的确定及环路参数设计 “般情况下,对应于不同的无线通信协议标准,所需要的频率综合器的性能 指标将会有很大差异。例如,欧洲数字电视标准DVB对频率综合器的相位噪声 和杂散抑制程度的要求相当苛刻,而在WLAN和GSM中的要求就宽松得多。 本章首先根据电缆电视调谐器的系统分析确定频率综合器的系统指标,然后根据 所确定的系统指标来选择频率综合器的体系架构,最后再根据具体的系统结构来 设计频率综合器的环路参数。 2.1频率综合器的性能指标 750 JpMixer DnMixer: Band Limit VGLNA Filter Second LO (Quadrature) First LO RF Front-end 图2.1DVB-CT标准的射频电视调谐器系统框图 DVB-CT标准的射频电视调谐器如图2.1所示。它的主要作用是将 50-860MHz信道中的带宽8MHz的数字电视信号下变频到低中频(7.2MHz)。为了 克服CMOS工艺中较大的直流失调(DC-offset)和闪烁噪声((flicker noise)性能较差 的缺点,接收机采用低中频架构;由于电视信号的宽频谱范围,为了降低压控振 荡器的设计难度以及减小芯片面积,需要采用两次变频(Double conversion)技术, 即射频信号先上变频到高中频(F=1120MHz),然后再下变频到低中频;为了抑 制低中频接收机镜像抑制mage rejection)较差的缺点,可以采用正交下变频技 术。本文研究的着眼点就是正交输出的频率综合器。它必须有很高的频率分辨率, 很小的/Q失配,很好的相位噪声性能和杂散性能,较快的锁定速度及合适的功 耗。参考一些商用的射频电视调谐器,2),我们可以得到应用于图2.2所示调谐器 中的频率综合器的系统指标,如表2-1所示

复旦大学硕士学位论文 第二章 频率综合器架构的确定及环路参数设计 第二章 频率综合器架构的确定及环路参数设计 一般情况下,对应于不同的无线通信协议标准,所需要的频率综合器的性能 指标将会有很大差异。例如,欧洲数字电视标准 DVB 对频率综合器的相位噪声 和杂散抑制程度的要求相当苛刻,而在 WLAN 和 GSM 中的要求就宽松得多。 本章首先根据电缆电视调谐器的系统分析确定频率综合器的系统指标,然后根据 所确定的系统指标来选择频率综合器的体系架构,最后再根据具体的系统结构来 设计频率综合器的环路参数。 2.1 频率综合器的性能指标 图 2.1 DVB-C/T 标准的射频电视调谐器系统框图 DVB-C/T标准的射频电视调谐器如图 2.1 所示。它的主要作用是将 50-860MHz信道中的带宽 8MHz的数字电视信号下变频到低中频(7.2MHz)。为了 克服CMOS工艺中较大的直流失调(DC-offset)和闪烁噪声(flicker noise)性能较差 的缺点,接收机采用低中频架构;由于电视信号的宽频谱范围,为了降低压控振 荡器的设计难度以及减小芯片面积,需要采用两次变频(Double conversion)技术, 即射频信号先上变频到高中频(IF=1120MHz),然后再下变频到低中频;为了抑 制低中频接收机镜像抑制(Image rejection)较差的缺点,可以采用正交下变频技 术。本文研究的着眼点就是正交输出的频率综合器。它必须有很高的频率分辨率, 很小的I/Q失配,很好的相位噪声性能和杂散性能,较快的锁定速度及合适的功 耗。参考一些商用的射频电视调谐器[1,2],我们可以得到应用于图 2.2 所示调谐器 [3]中的频率综合器的系统指标,如表 2-1 所示。 3

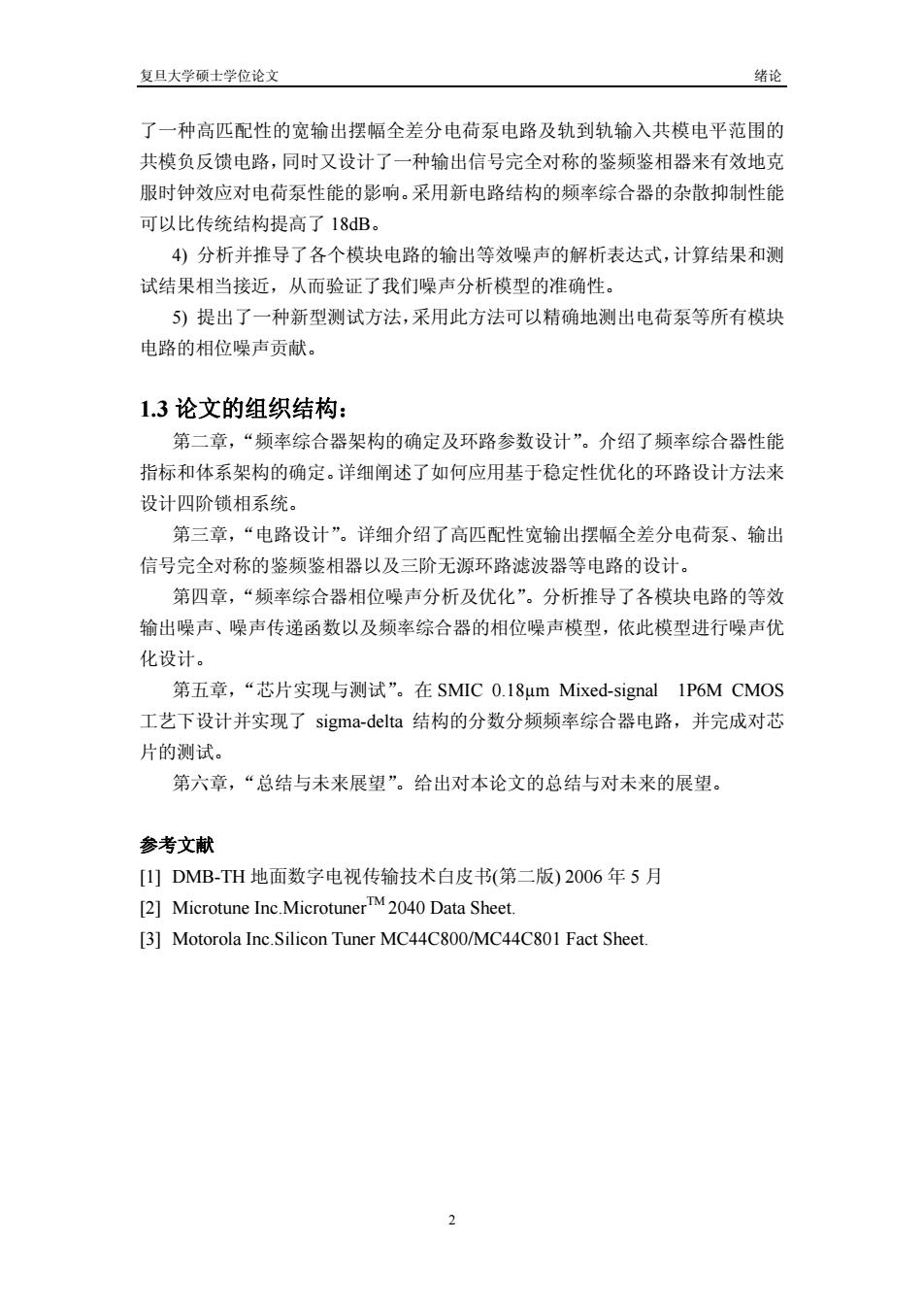

复旦大学硕士学位论文 第二章频率综合器架构的确定及环路参数设计 IF1:1120MHz Mixer VGA 50-860MHz /GLNA IF2:7.2MHz AA Filter F VGA vco e oop hase cale Phase AFC AFC Detector 45 ounte 1150-2000MHz 1050-1190MHz Ref Divider Control 3Bits ZA osc Bandgap &LDO 25MHz SCLSDA 图2.2射频电视调谐器 表2-1频率综合器的一些设计指标 调谐范围 1.02GHz-1.18GHz 参考时钟 25MHz 频率阶跃 <62.5KHz 锁定时间 <100μs 相位噪声 <-80dBc/Hz@10kHz <-100dBc/Hz@100kHz <-130dBc/Hz@1MHz 杂散 <-80dBc 功耗 25mW 2.2频率综合器的系统架构 频率综合器主要分为整数分频(integer-.N)和分数分频(fractional-.N)两种,对于 整数分频来说,频率分辨率为参考时钟的频率,环路带宽的最大值是参考时钟频 率的1/10。对于分频比为Nf的分数分频来说,其频率分辨率可以为fxfref。电视 调谐器系统要求的频率分辨率小于62.5KHz,如果选取整数分频的话,环路带宽 最大只能为6.25KHz,这样环路的锁定时间约为160μs,而且相位噪声性能会很 差,因此整数分频的方案是根本不可行的。最终频率综合器将采用分数分频架构。 4

复旦大学硕士学位论文 第二章 频率综合器架构的确定及环路参数设计 Mixer VCO AFC Loop Filter Phase Detector Charge Pump Prescaler 1/8 Divider 40-80 Ref Divider 1/2 Quad. VCO Prescaler 1/4 AFC Prescaler 4/5 PS Counter 3Bits ΣΔ Modulator Loop Filter Charge Pump Phase Detector Control Registers I2C IF Amp IF Amp Mixer Mixer AA Filter AA Filter Prescaler 2/3 25MHz OSC SCLSDA 1150-2000MHz 1050-1190MHz 50-860MHz IF1:1120MHz IF2:7.2MHz Bandgap & LDO VGLNA RF VGA IF VGA IF VGA 图 2.2 射频电视调谐器 表 2-1 频率综合器的一些设计指标 调谐范围 1.02GHz-1.18GHz 参考时钟 25MHz 频率阶跃 <62.5KHz 锁定时间 <100µs 相位噪声 <-80dBc/Hz@10kHz <-100dBc/Hz@100kHz <-130dBc/Hz@1MHz 杂散 <-80dBc 功耗 25mW 2.2 频率综合器的系统架构 频率综合器主要分为整数分频(integer-N)和分数分频(fractional-N)两种,对于 整数分频来说,频率分辨率为参考时钟的频率,环路带宽的最大值是参考时钟频 率的 1/10。对于分频比为N.f的分数分频来说,其频率分辨率可以为f×fref。电视 调谐器系统要求的频率分辨率小于 62.5KHz,如果选取整数分频的话,环路带宽 最大只能为 6.25KHz,这样环路的锁定时间约为 160µs,而且相位噪声性能会很 差,因此整数分频的方案是根本不可行的。最终频率综合器将采用分数分频架构。 4

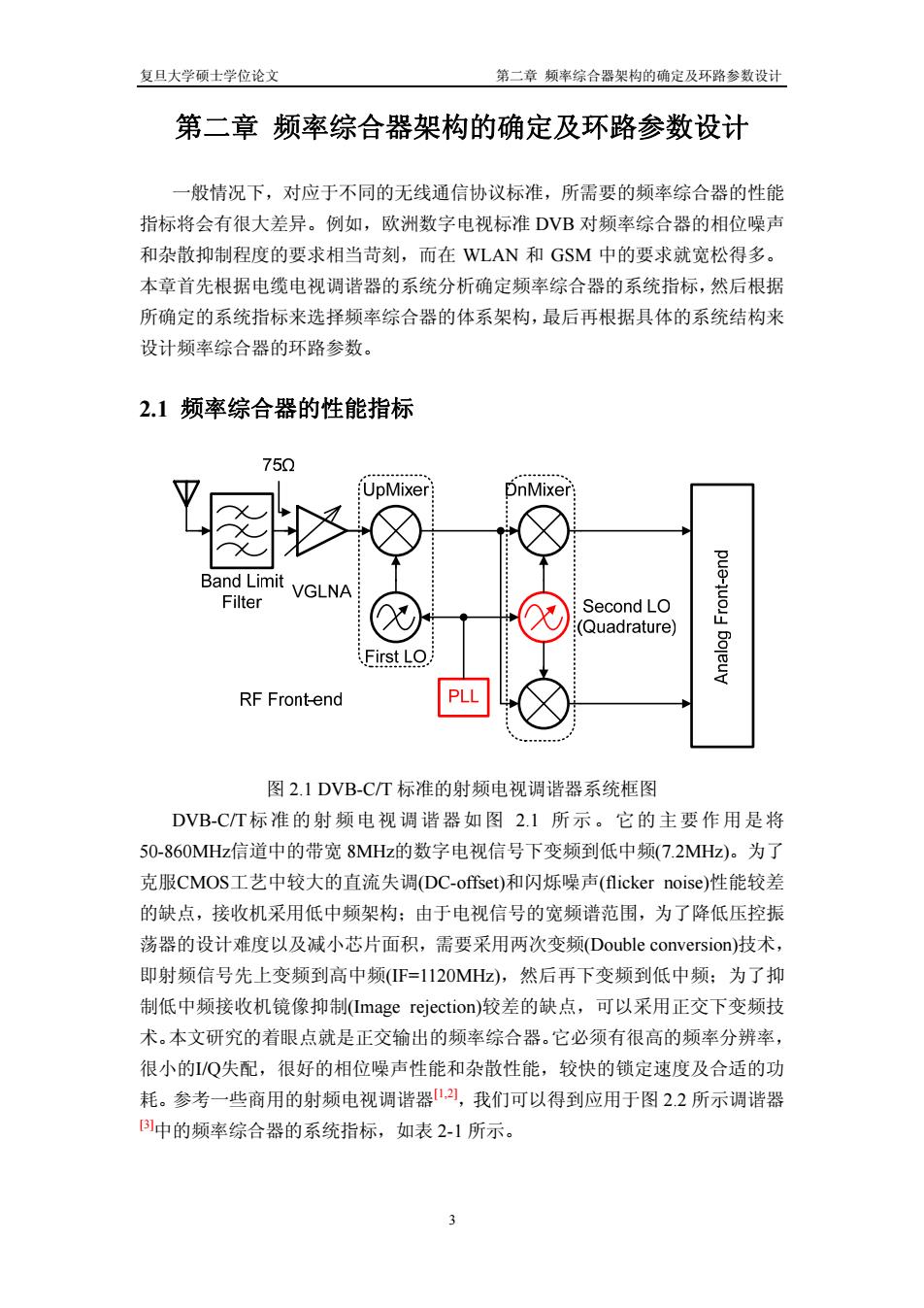

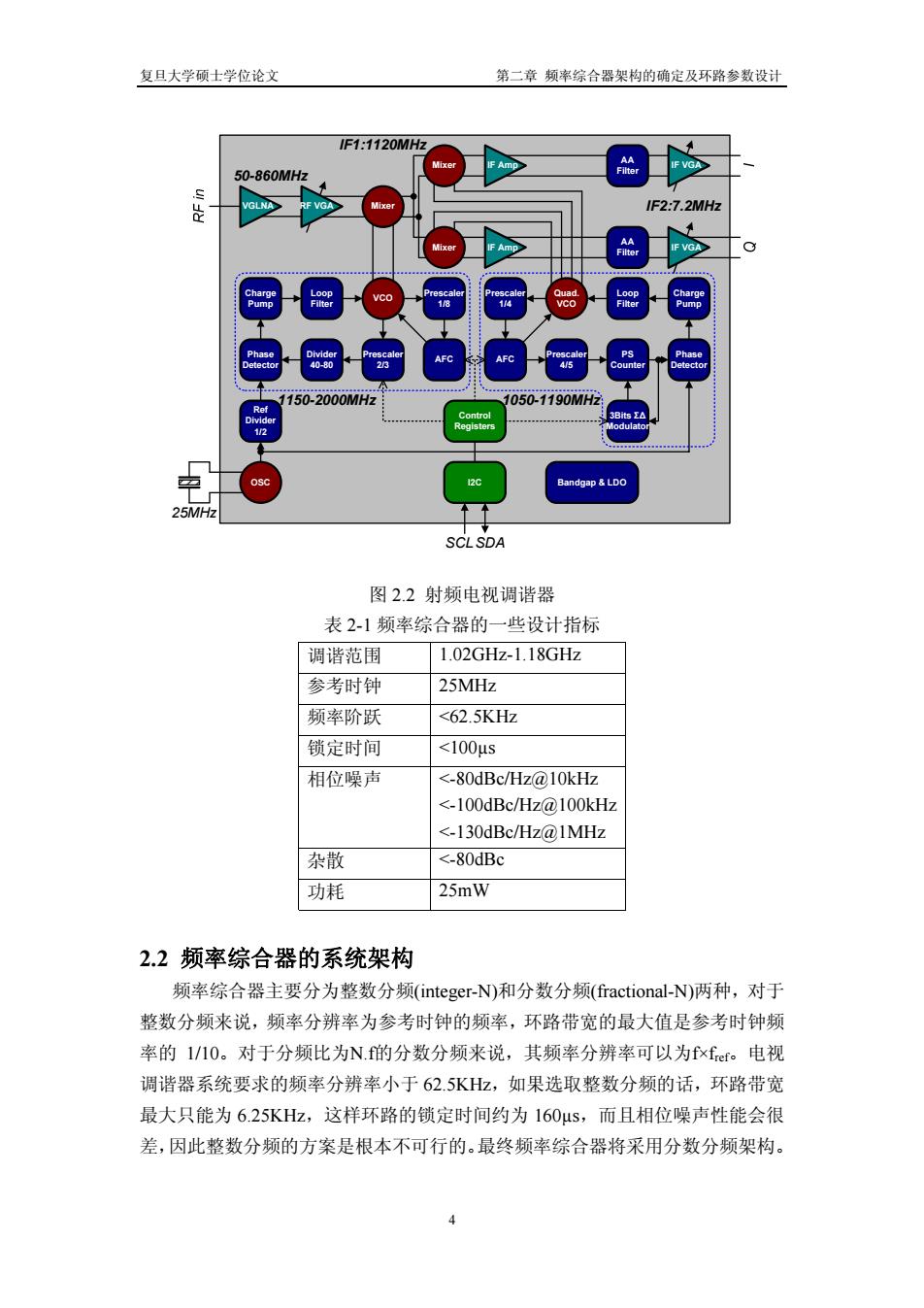

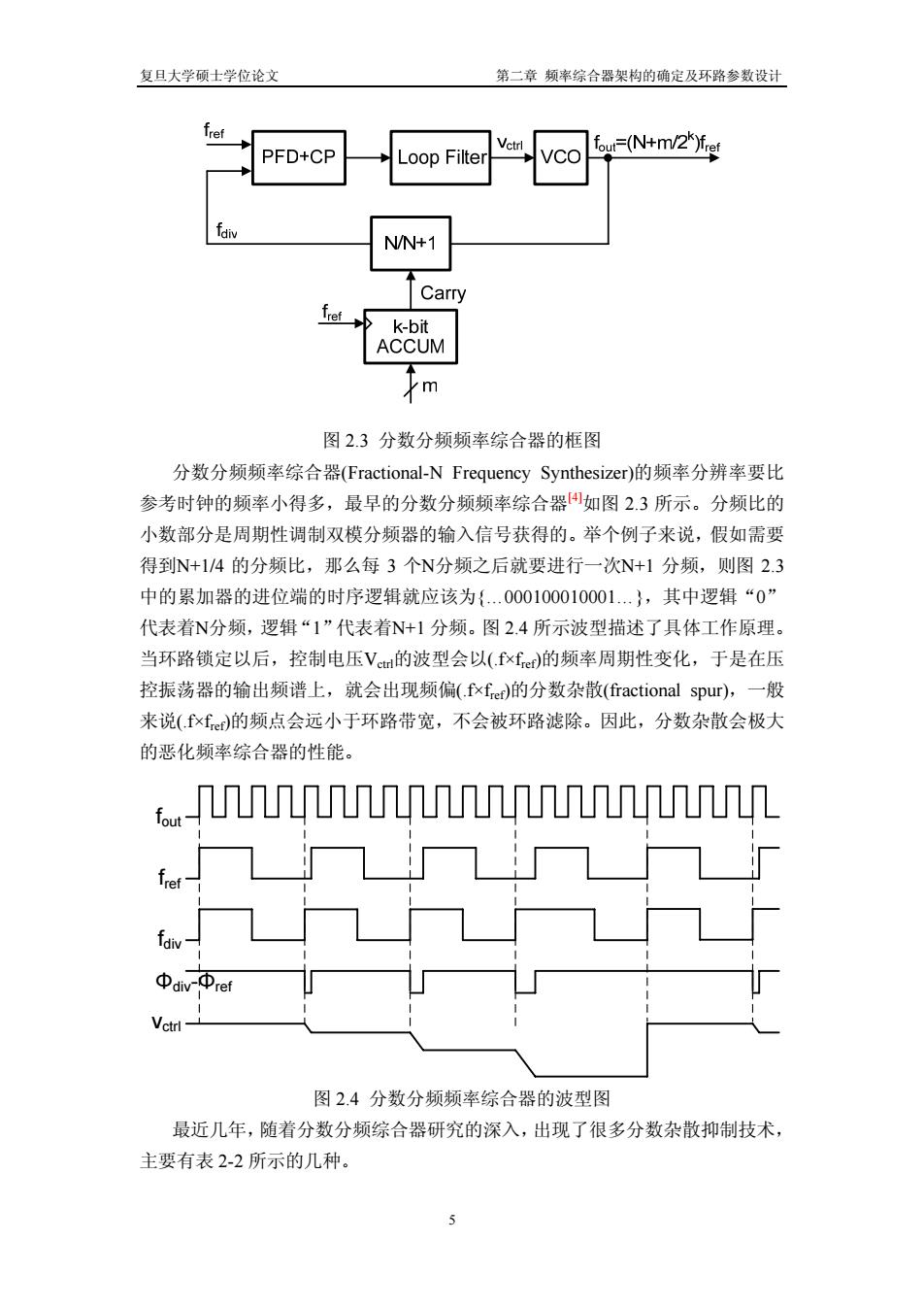

复旦大学硕士学位论文 第二章频率综合器架构的确定及环路参数设计 fref Vctrl PFD+CP Loop Filter fou=(N+m/2)frer faliv N/N+1 Carry k-bit ACCUM m 图2.3分数分频频率综合器的框图 分数分频频率综合器(Fractional-N Frequency Synthesizer)的频率分辨率要比 参考时钟的频率小得多,最早的分数分频频率综合器如图2.3所示。分频比的 小数部分是周期性调制双模分频器的输入信号获得的。举个例子来说,假如需要 得到N+1/4的分频比,那么每3个N分频之后就要进行一次N+1分频,则图2.3 中的累加器的进位端的时序逻辑就应该为{.000100010001..},其中逻辑“0” 代表着N分频,逻辑“1”代表着N+1分频。图2.4所示波型描述了具体工作原理。 当环路锁定以后,控制电压Vc的波型会以(.f×fe)的频率周期性变化,于是在压 控振荡器的输出频谱上,就会出现频偏(.f×fef)的分数杂散(fractional spur),一般 来说(f×fe)的频点会远小于环路带宽,不会被环路滤除。因此,分数杂散会极大 的恶化频率综合器的性能。 ref 中div-pref Vctrl- 图2.4分数分频频率综合器的波型图 最近几年,随着分数分频综合器研究的深入,出现了很多分数杂散抑制技术, 主要有表2-2所示的几种。 5

复旦大学硕士学位论文 第二章 频率综合器架构的确定及环路参数设计 图 2.3 分数分频频率综合器的框图 分数分频频率综合器(Fractional-N Frequency Synthesizer)的频率分辨率要比 参考时钟的频率小得多,最早的分数分频频率综合器[4]如图 2.3 所示。分频比的 小数部分是周期性调制双模分频器的输入信号获得的。举个例子来说,假如需要 得到N+1/4 的分频比,那么每 3 个N分频之后就要进行一次N+1 分频,则图 2.3 中的累加器的进位端的时序逻辑就应该为{…000100010001…},其中逻辑“0” 代表着N分频,逻辑“1”代表着N+1 分频。图 2.4 所示波型描述了具体工作原理。 当环路锁定以后,控制电压Vctrl的波型会以(.f×fref)的频率周期性变化,于是在压 控振荡器的输出频谱上,就会出现频偏(.f×fref)的分数杂散(fractional spur),一般 来说(.f×fref)的频点会远小于环路带宽,不会被环路滤除。因此,分数杂散会极大 的恶化频率综合器的性能。 fref fout fdiv vctrl Φdiv-Φref 图 2.4 分数分频频率综合器的波型图 最近几年,随着分数分频综合器研究的深入,出现了很多分数杂散抑制技术, 主要有表 2-2 所示的几种。 5