3.2标准的目的 使测试指令和测试数据串行施加到被测元件(CUT) -可读出测试结果 可采用RUNBIST命令 >避免外测试下太多的移位 冬JTAG可应用于芯片级,PCB,&系统级 冬在测试时,可进行三态信号控制 。来自其它芯片收集CUT的响应 ·从元件分别测试系统互连 冬从连线分别测试元件 2020/9/5 集成电路可测性设计 12

3.2 标准的目的 使测试指令和测试数据串行施加到被测元件(CUT) 可读出测试结果 可采用RUNBIST 命令 避免外测试下太多的移位 JTAG 可应用于芯片级, PCB, &系统级 在测试时, 可进行三态信号控制 来自其它芯片收集CUT的响应 从元件分别测试系统互连 从连线分别测试元件 2020/9/5 集成电路可测性设计 12

3.3边界扫描测试基本原理 冬在靠近器件的每个输入/输出(I/0)引腿处增加一 个移位寄存器单元.在测试期间,这些寄存器单 元用于控制输入引腿的状态(高或低),并读出 输出引腿的状态 。以此来判断器件的好坏及互连的正确性.在正常工 作期间,这些附加的移位寄存器单元是“透明 的”,即它不影响电路的正常工作. 2020/9/5 集成电路可测性设计 13

3.3 边界扫描测试基本原理 在靠近器件的每个输入/输出(I/O)引腿处增加一 个 移位寄存器单元. 在测试期间, 这些寄存器单 元用于控 制输入引腿的状态(高或低), 并读出 输出引腿的状态 以此来判断器件的好坏及互连的正确性. 在正常工 作 期间, 这些附加的移位寄存器单元是“透明 的”, 即它不 影响电路的正常工作. 2020/9/5 集成电路可测性设计 13

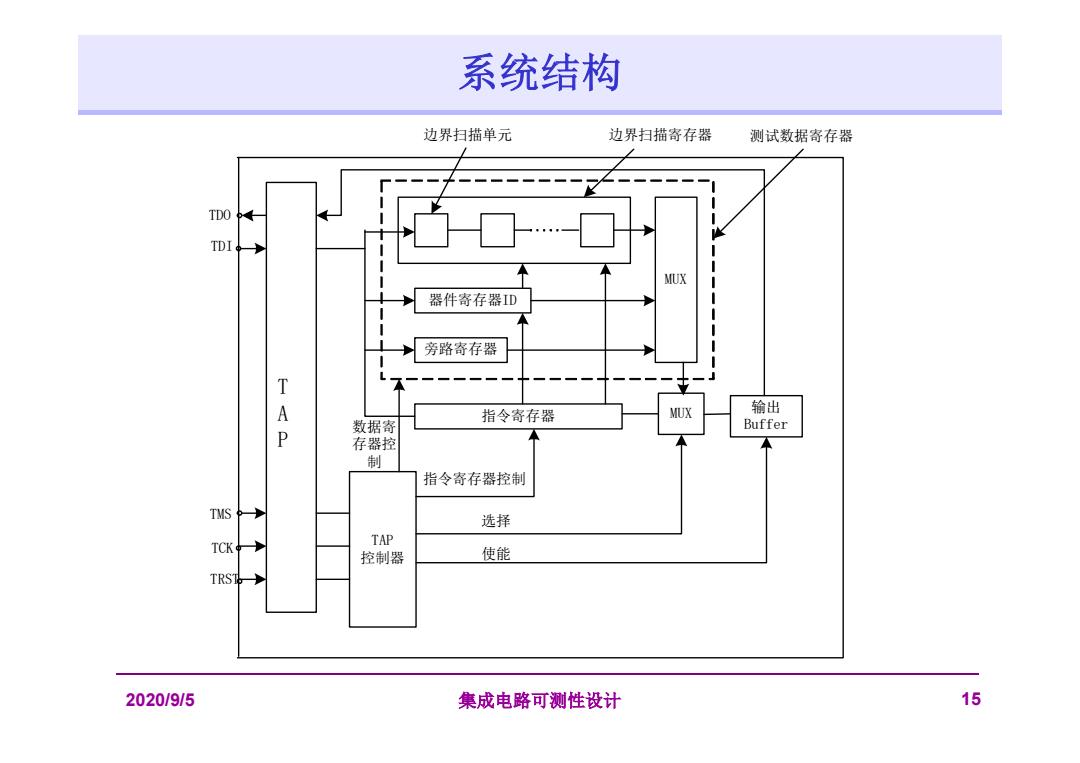

3.5边界扫描结构 必测试访问端口 (TAP) (4-5额外引腿) 测试数据输入(TDI) -测试数据输出(TDO) -测试时钟(TCK) -测试模式选择(TMS) ”寄存器组 -指令寄存器 (IR) -数据寄存器(DR):旁路寄存器,边界扫描寄存器,ID寄存器 Mandatory:Boundary scan register and Bypass register Optional:Device-ID register,Design-Specific registers, etc. TAP控制器 一 A finite state machine with 16 states Input TCK,TMS Output 9 or 10 signals included ClockDR, UpdateDR, ShiftDR,ClockIR,UpdateIR,ShiftIR, Select,Enable, TCK and the optional TRST*. 2020/9/5 集成电路可测性设计 14

3.5 边界扫描结构 测试访问端口 (TAP) ( 4 - 5额外引腿) 测试数据输入 (TDI) 测试数据输出 (TDO) 测试时钟 (TCK) 测试模式选择 (TMS) 寄存器组 指令寄存器 (IR) 数据寄存器 (DR): 旁路寄存器, 边界扫描寄存器, ID寄存器 Mandatory: Boundary scan register and Bypass register Optional: Device-ID register, Design-Specific registers, etc. TAP 控制器 A finite state machine with 16 states Input : TCK, TMS Output : 9 or 10 signals included ClockDR, UpdateDR, ShiftDR, ClockIR, UpdateIR, ShiftIR, Select, Enable, TCK and the optional TRST*. 2020/9/5 集成电路可测性设计 14

系统结构 边界扫描单元 边界扫描寄存器 测试数据寄存器 TDO TDI MUX 器件寄存器ID 旁路寄存器 T 指令寄存器 MUX 输出 P 数据寄 Buffer 存器控 制 指令寄存器控制 TMS 选择 TCK TAP 控制器 使能 2020/9/5 集成电路可测性设计 15

系统结构 器件寄存器ID 旁路寄存器 MUX 指令寄存器 TDI MUX 输出 Buffer TDO TAP 控制器 TMS TCK TRST 数据寄 存器控 制 指令寄存器控制 选择 使能 边界扫描单元 边界扫描寄存器 测试数据寄存器 T A P 2020/9/5 集成电路可测性设计 15

端口信号解释 (1)测试时钟TCK 专用时钟信号,各个步骤的基准,许多测试逻辑是在T℃K的上升沿或下降沿完成。 测试数据可以用测试时钟T℃K串行移入移出,也可以并行移入。 多 (2)测试方式选择TMS 传送测试控制信息,由TAP控制器译码并控制相应的测试操作。,由于仅用一根输入线控制许 多元器件,所以必须用一个输入序列来确定测试方式,同时也必须确保序列传输和译码的 准确性。 测试逻辑在TCK的上升沿采样TMS传输的信号值,因此最好应在TCK的下降沿把TMS改变为下 一个要传输的值。 (3)串行测试数据输入TDI 以申行方式移入输入数据,数据有两种:一种供指令寄存器译码的指令数据,一种是传输 到测试数据寄存器的测试数据。 测试逻辑在TCK的上升沿采样TDI信号。 ÷(4)串行测试数据输出TD0 以串行方式移出数据,传输的数据也是两种,测试指令和测试数据。 测试逻辑在TCK的下降采样TD0信号。 (5)测试系统复位TRST 除了上述4条强制规定的信号外,IEEE1149.1标准还提供一个可供选择的输入信号“测试系 统复位”,功能是控制TAP控制器异步初始化。为了保证测试逻辑的确定性,当TRST上施加 的信号丛0变为1时MS在逻辑1上要保特个TCK时钟周期。 2020/9/5 集成电路可测性设计 16

2020/9/5 集成电路可测性设计 16 端口信号解释 (1)测试时钟TCK 专用时钟信号,各个步骤的基准,许多测试逻辑是在TCK的上升沿或下降沿完成。 测试数据可以用测试时钟TCK串行移入移出,也可以并行移入。 (2)测试方式选择TMS 传送测试控制信息,由TAP控制器译码并控制相应的测试操作。由于仅用一根输入线控制许 多元器件,所以必须用一个输入序列来确定测试方式,同时也必须确保序列传输和译码的 准确性。 测试逻辑在TCK的上升沿采样TMS传输的信号值,因此最好应在TCK的下降沿把TMS改变为下 一个要传输的值。 (3)串行测试数据输入TDI 以串行方式移入输入数据,数据有两种:一种供指令寄存器译码的指令数据,一种是传输 到测试数据寄存器的测试数据。 测试逻辑在TCK的上升沿采样TDI信号。 (4)串行测试数据输出TDO 以串行方式移出数据,传输的数据也是两种,测试指令和测试数据。 测试逻辑在TCK的下降采样TDO信号。 (5)测试系统复位TRST 除了上述4条强制规定的信号外,IEEE1149.1标准还提供一个可供选择的输入信号“测试系 统复位”,功能是控制TAP控制器异步初始化。为了保证测试逻辑的确定性,当TRST上施加 的信号从0变为1时,TMS在逻辑1上要保持几个TCK时钟周期