3.6系统测试逻辑 Boundary Register Cell Boundary Register System Circuitry 爱 Device ID Register 00000.0000 Bypass Register Instruction Register 000000 (Control Signals) TDO TCK TAP Controller TMS TRST* 2020/9/5 集成电路可测性设计 17

3.6 系统测试逻辑 2020/9/5 集成电路可测性设计 17

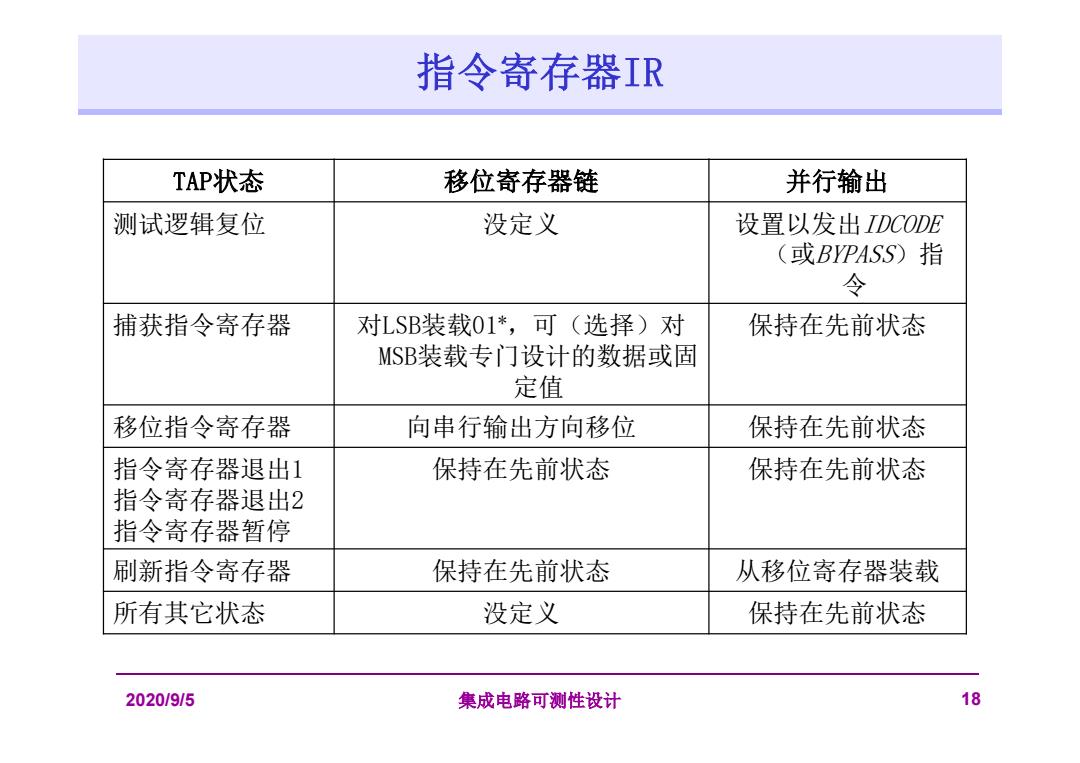

指令寄存器IR TAP状态 移位寄存器链 并行输出 测试逻辑复位 没定义 设置以发出IDCODE (或BYPASS)指 令 捕获指令寄存器 对LSB装载01*,可(选择)对 保持在先前状态 MSB装载专门设计的数据或固 定值 移位指令寄存器 向串行输出方向移位 保持在先前状态 指令寄存器退出1 保持在先前状态 保持在先前状态 指令寄存器退出2 指令寄存器暂停 刷新指令寄存器 保持在先前状态 从移位寄存器装载 所有其它状态 没定义 保持在先前状态 2020/9/5 集成电路可测性设计 18

2020/9/5 集成电路可测性设计 18 指令寄存器IR TAP状态 移位寄存器链 并行输出 测试逻辑复位 没定义 设置以发出IDCODE (或BYPASS)指 令 捕获指令寄存器 对LSB装载01*,可(选择)对 MSB装载专门设计的数据或固 定值 保持在先前状态 移位指令寄存器 向串行输出方向移位 保持在先前状态 指令寄存器退出1 指令寄存器退出2 指令寄存器暂停 保持在先前状态 保持在先前状态 刷新指令寄存器 保持在先前状态 从移位寄存器装载 所有其它状态 没定义 保持在先前状态

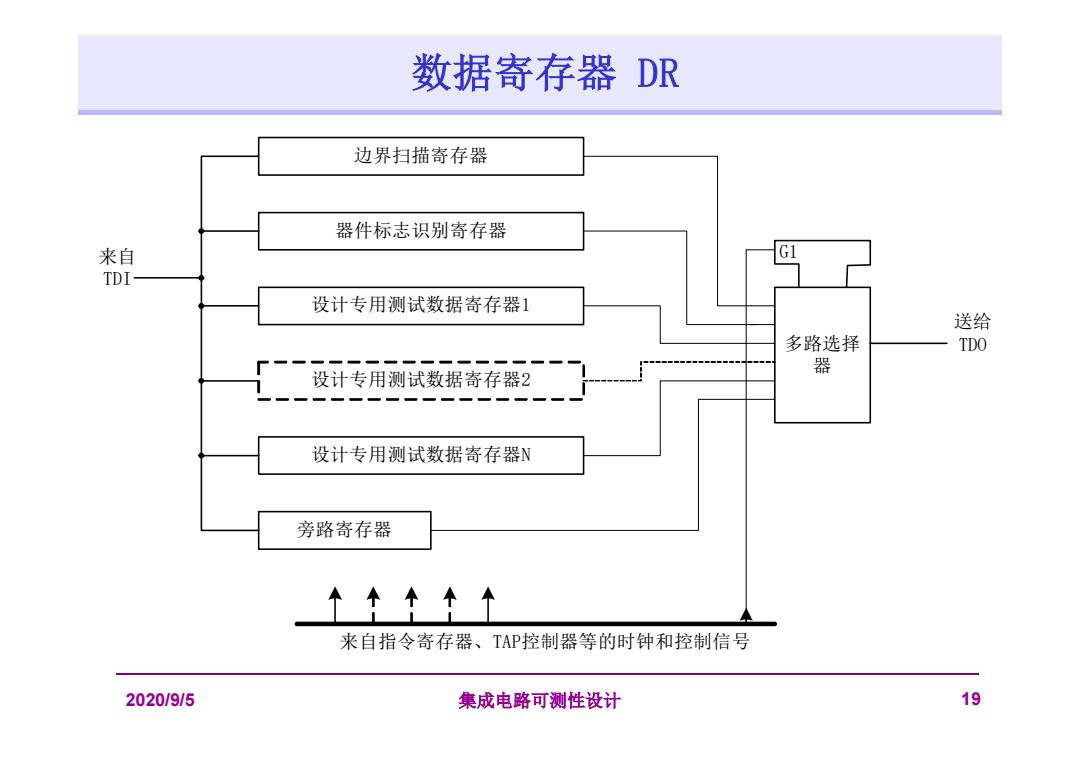

数据寄存器DR 边界扫描寄存器 器件标志识别寄存器 来自 TDI- 设计专用测试数据寄存器1 送给 多路选择 TDO 设计专用测试数据寄存器2 器 设计专用测试数据寄存器N 旁路寄存器 个个个个个 来自指令寄存器、TAP控制器等的时钟和控制信号 2020/9/5 集成电路可测性设计 19

2020/9/5 集成电路可测性设计 19 数据寄存器 DR 多路选择 器 G1 边界扫描寄存器 器件标志识别寄存器 旁路寄存器 设计专用测试数据寄存器1 设计专用测试数据寄存器N 设计专用测试数据寄存器2 送给 TDO 来自 TDI 来自指令寄存器、TAP控制器等的时钟和控制信号

旁路寄存器BR 来自DI 送给D0 位数据寄存器 时钟数据寄存器 2020/9/5 集成电路可测性设计 20

2020/9/5 集成电路可测性设计 20 旁路寄存器BR 1D C1 来自TDI 移位数据寄存器 时钟数据寄存器 送给TDO

边界扫描寄存器BSR 边界扫描寄存器单元BSRC 单元的路线逻辑 并行输入 单元的PIP0级 》并行输出 1D 1D C1 串行输入 串行输出 时钟与控制 路线控制 2020/9/5 集成电路可测性设计 21

2020/9/5 集成电路可测性设计 21 边界扫描寄存器BSR 1D C1 G1 1 1 1D C1 单元的路线逻辑 单元的PIPO级 串行输入 串行输出 时钟与控制 路线控制 并行输入 并行输出 边界扫描寄存器单元BSRC PI PO I O }