7.3随机存储器 (RAM) 7.3.1静态随机存储器 (SRAM) 一、SRAM的结构和工作原理 二、SRAM的静态存储单元→ 返回 2006年 新疆大学信息科学与工程学院 《数字电路课题组》

2006年 新疆大学信息科学与工程学院 《数字电路课题组》 7.3 随机存储器(RAM) 7.3.1 静态随机存储器(SRAM) 一、SRAM的结构和工作原理 二、SRAM的静态存储单元 返回

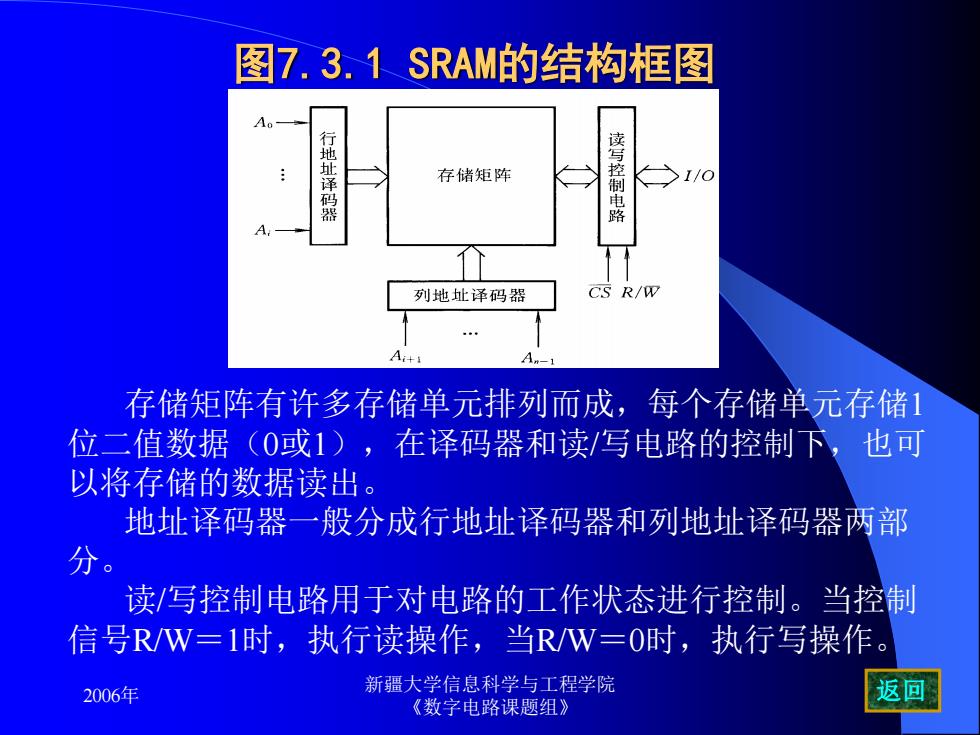

图7.3.1SRAM的结构框图 行地址译码器 存储矩阵 读写控制 A- 列地址译码器 CS R/W Ai+ A 存储矩阵有许多存储单元排列而成,每个存储单元存储1 位二值数据(0或1),在译码器和读/写电路的控制下,也可 以将存储的数据读出。 地址译码器一般分成行地址译码器和列地址译码器两部 分。 读/写控制电路用于对电路的工作状态进行控制。当控制 信号R/W=1时,执行读操作,当RW=0时,执行写操作。 2006年 新疆大学信息科学与工程学院 返回 《数字电路课题组》

2006年 新疆大学信息科学与工程学院 《数字电路课题组》 图7.3.1 SRAM的结构框图 存储矩阵有许多存储单元排列而成,每个存储单元存储1 位二值数据(0或1),在译码器和读/写电路的控制下,也可 以将存储的数据读出。 地址译码器一般分成行地址译码器和列地址译码器两部 分。 读/写控制电路用于对电路的工作状态进行控制。当控制 信号R/W=1时,执行读操作,当R/W=0时,执行写操作。 返回