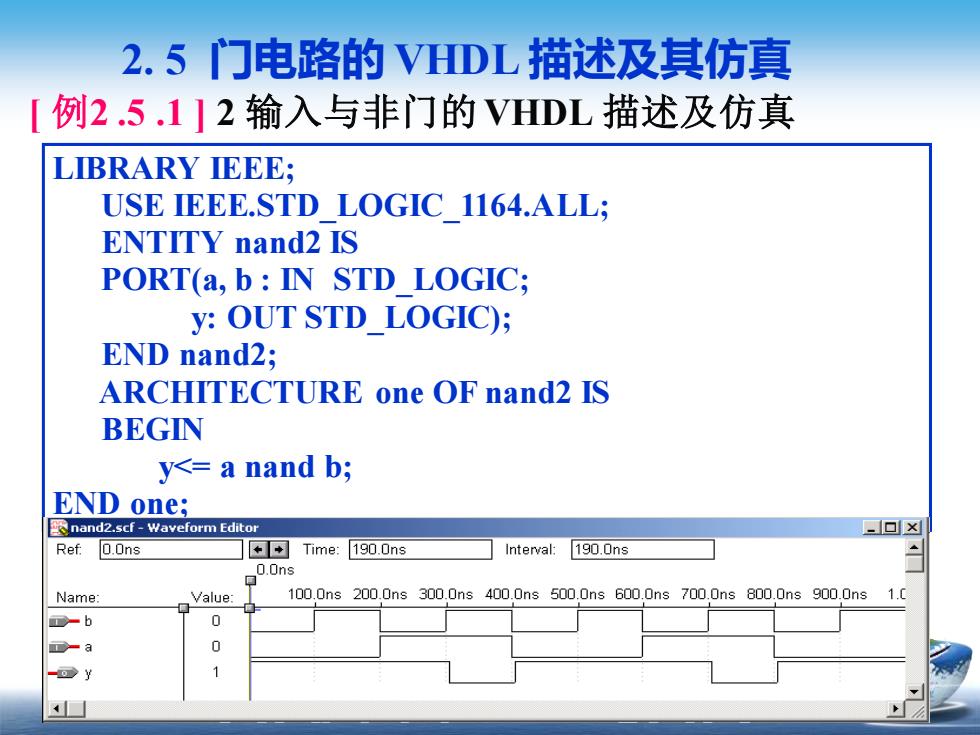

2.5门电路的VDL描述及其仿真 [例2.5.12输入与非门的VHDL描述及仿真 LIBRARY IEEE; USE IEEE.STD LOGIC 1164.ALL; ENTITY nand2 IS PORT(a,b:IN STD LOGIC; y:OUT STD LOGIC); END nand2; ARCHITECTURE one OF nand2 IS BEGIN y<=a nand b; END one; nand2.scf-Waveform Editor ▣x Ref:0.0ns Time: 190.0ns Interval:190.0ns 0.Ons Name: Value: 100.0ns200.0ns300.0ns400.0ns500.0ns600.0ns700.0ns800.0ns900.0ns1.0 b 0 工=a 0 y 口

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY nand2 IS PORT(a, b : IN STD_LOGIC; y: OUT STD_LOGIC); END nand2; ARCHITECTURE one OF nand2 IS BEGIN y<= a nand b; END one; [ 例2 .5 .1 ] 2 输入与非门的VHDL 描述及仿真 2. 5 门电路的 VHDL 描述及其仿真

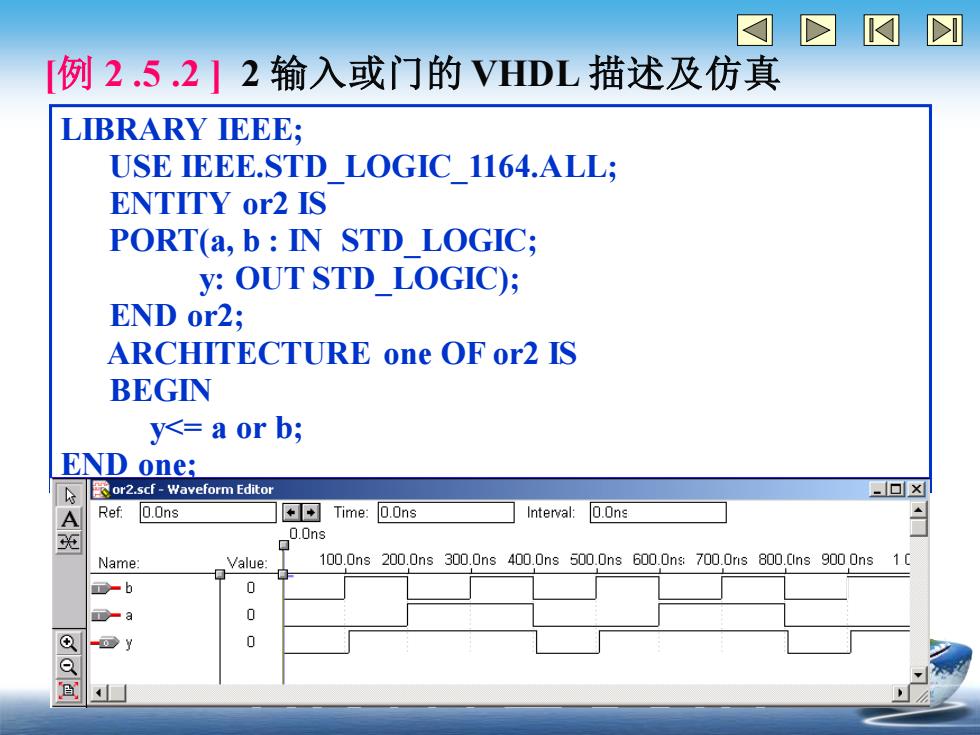

D I 例2.5.2】2输入或门的VHDL描述及仿真 LIBRARY IEEE; USE IEEE.STD LOGIC 1164.ALL; ENTITY or2 IS PORT(a,b:IN STD LOGIC; y:OUT STD LOGIC); END or2; ARCHITECTURE one OF or2 IS BEGIN y<=a or b; END one; or2.scf-Waveform Editor -▣x A Ref.0.0ns +中Time:O.Ons Interval: 0.0n3 0.0ns Name: Value: 100.0ns200.0ns300.0ns400.0ns500.0ns600.0ns:700.0r1s800.Cins9000ns1C 工-b 0 工-a 0 ® -@y 0 a

[例 2 .5 .2 ] 2 输入或门的 VHDL 描述及仿真 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY or2 IS PORT(a, b : IN STD_LOGIC; y: OUT STD_LOGIC); END or2; ARCHITECTURE one OF or2 IS BEGIN y<= a or b; END one;

例2.5.3非门的VHDL描述及仿真 LIBRARY IEEE: USE IEEE.STD LOGIC 1164.ALL; ENTITY hnot IS PORT(a:IN STD LOGIC; y:OUT STD LOGIC); END hnot; ARCHITECTURE one OF hnot IS BEGIN y<=not a; END one; hnot.scf-Waveform Editor -▣x Ref: 0.0ns 图Time: 635.0ns Interval: 635.0ns Name: Value: 100.0ns200.0ns300.0ns400.0ns500.0ns600.0ns700.0ns80C.0ns900.0ns1.0 工-a 0 y 1

[例 2 .5 .3 ] 非门的 VHDL 描述及仿真 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY hnot IS PORT(a : IN STD_LOGIC; y: OUT STD_LOGIC); END hnot; ARCHITECTURE one OF hnot IS BEGIN y<= not a; END one;

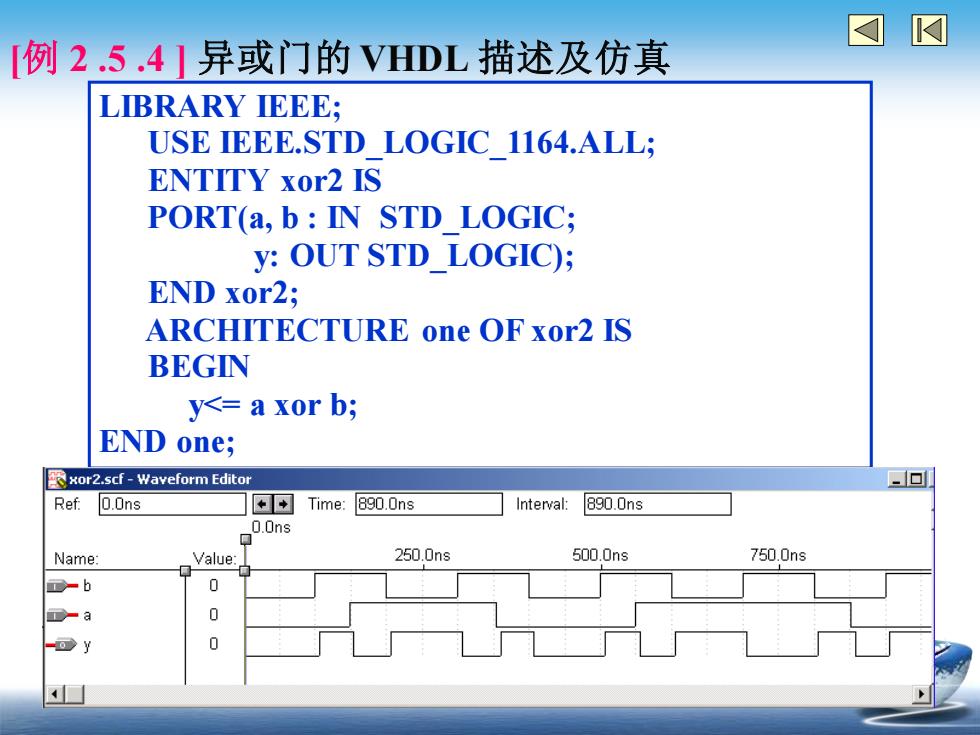

☒ [例2.5.4]异或门的VHDL描述及仿真 LIBRARY IEEE: USE IEEE.STD LOGIC 1164.ALL; ENTITY xor2 IS PORT(a,b:IN STD LOGIC; y:OUT STD LOGIC); END xor2; ARCHITECTURE one OF xor2 IS BEGIN y<=a xor b; END one; xor2.scf-Waveform Editor ▣ Ref 0.0ns 中 Time:890.0ns Interval: 890.0ns 0.Ons Name Value: 250.0ns 500.0ns 750.0ns D-b D-a 0 o●y

[例 2 .5 .4 ] 异或门的 VHDL 描述及仿真 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY xor2 IS PORT(a, b : IN STD_LOGIC; y: OUT STD_LOGIC); END xor2; ARCHITECTURE one OF xor2 IS BEGIN y<= a xor b; END one;