1.4EDA技术的基础知识 1.4.1VHDL语言基础 VHDL一超高速硬件描述语言 Very High Speed Hardware Description Language) 一、 VHDL的主要构件 实体(Entity)-描述设计单元的外部接口信号 基本 结构体(Architecture)-描述设计单元内部结构和行为 设计 单元 程序包(Package)-存放各设计模块共享的数据类 型、常数、子程序等 库(Library)-专门存放程序包 配置(Configration)-指定实体所要配置的结构体

1.4 EDA技术的基础知识 1. 4. 1 VHDL语言基础 一、VHDL的主要构件 基本 设计 单元 VHDL — 超高速硬件描述语言 (Very High Speed Hardware Description Language) 实体(Entity ) 结构体(Architecture ) 程序包(Package ) 库(Library ) 配置(Configration ) -描述设计单元的外部接口信号 -描述设计单元内部结构和行为 - 存放各设计模块共享的数据类 型、常数、子程序等 - 专门存放程序包 -指定实体所要配置的结构体

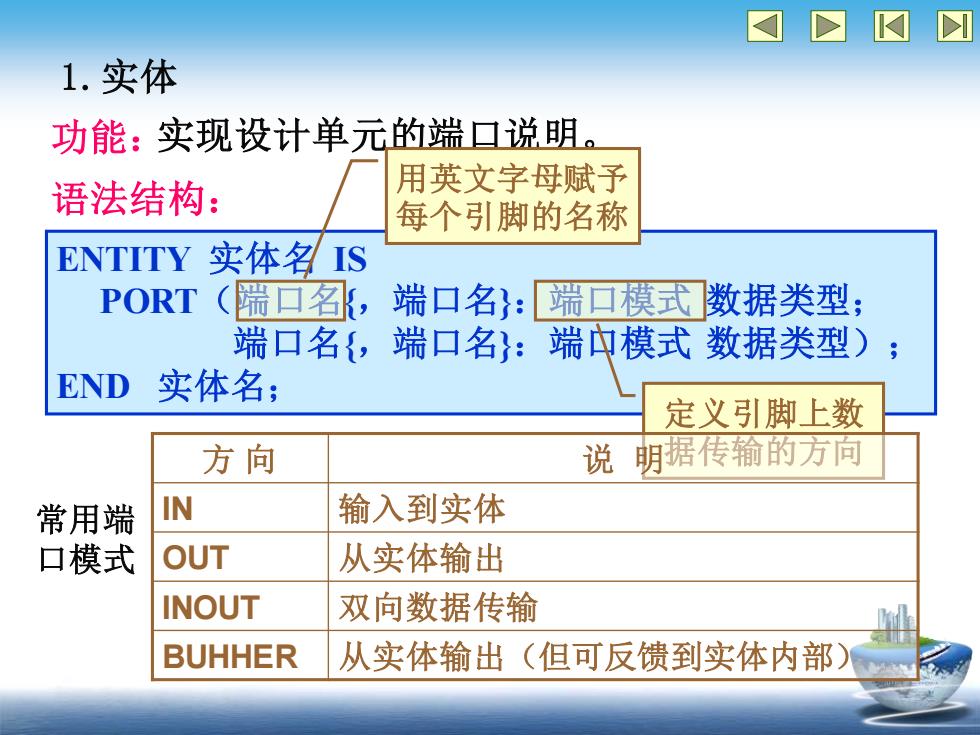

1.实体 功能:实现设计单元的端口说明。 语法结构: 用英文字母赋予 每个引脚的名称 ENTITY 实体名IS PORT(瑞口名, 端口名}:瑞口模式数据类型; 端口名{,端口名}:端中模式数据类型); END 实体名; 定义引脚上数 方向 说明据传输的方同 常用端 IN 输入到实体 口模式 OUT 从实体输出 INOUT 双向数据传输 BUHHER 从实体输出(但可反馈到实体内部)

1.实体 功能:实现设计单元的端口说明。 语法结构: ENTITY 实体名 IS PORT(端口名{,端口名}:端口模式 数据类型; 端口名{,端口名}:端口模式 数据类型); END 实体名; 用英文字母赋予 每个引脚的名称 定义引脚上数 据传输的方向 常用端 口模式 方 向 说 明 IN 输入到实体 OUT 从实体输出 INOUT 双向数据传输 BUHHER 从实体输出(但可反馈到实体内部)

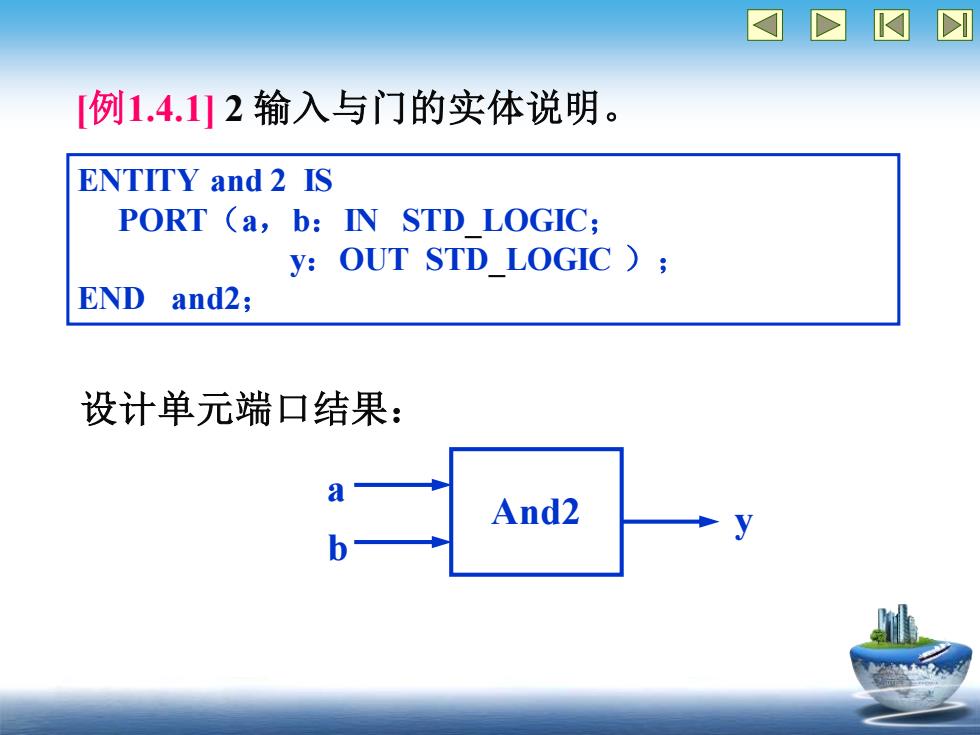

冈 [例1.4.12输入与门的实体说明。 ENTITY and 2 IS PORT (a,b:IN STD LOGIC; y:OUT STD LOGIC ) END and2; 设计单元端口结果: 2 And2

[例1.4.1] 2 输入与门的实体说明。 ENTITY and 2 IS PORT(a,b:IN STD_LOGIC; y:OUT STD_LOGIC ); END and2; 设计单元端口结果: And2 a b y

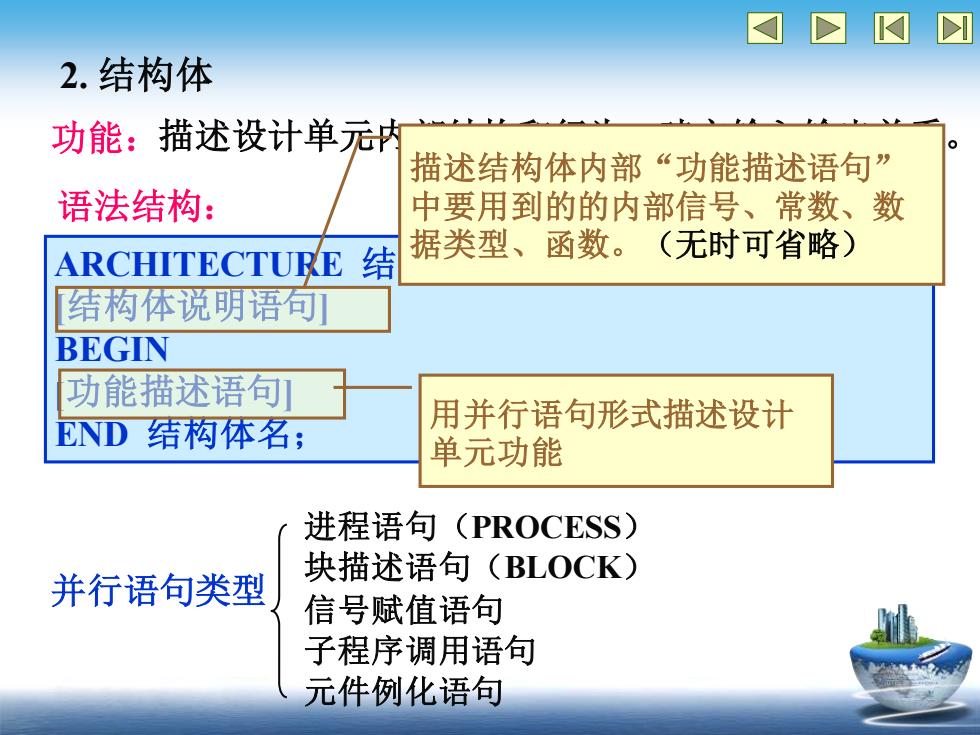

2.结构体 功能:描述设计单元疟内 描述结构体内部“功能描述语句” 语法结构: 中要用到的的内部信号、常数、数 ARCHITECTURE结 据类型、函数。(无时可省略) 结构体说明语句 BEGIN 功能描述语句] ND结构体名; 用并行语句形式描述设计 单元功能 进程语句(PROCESS) 块描述语句(BLOCK) 并行语句类型 信号赋值语句 子程序调用语句 元件例化语句

2. 结构体 功能:描述设计单元内部结构和行为,建立输入输出关系。 语法结构: ARCHITECTURE 结构体名 OF 实体名 IS [结构体说明语句] BEGIN [功能描述语句] END 结构体名; 描述结构体内部“功能描述语句” 中要用到的的内部信号、常数、数 据类型、函数。(无时可省略) 用并行语句形式描述设计 单元功能 并行语句类型 进程语句(PROCESS) 块描述语句(BLOCK) 信号赋值语句 子程序调用语句 元件例化语句

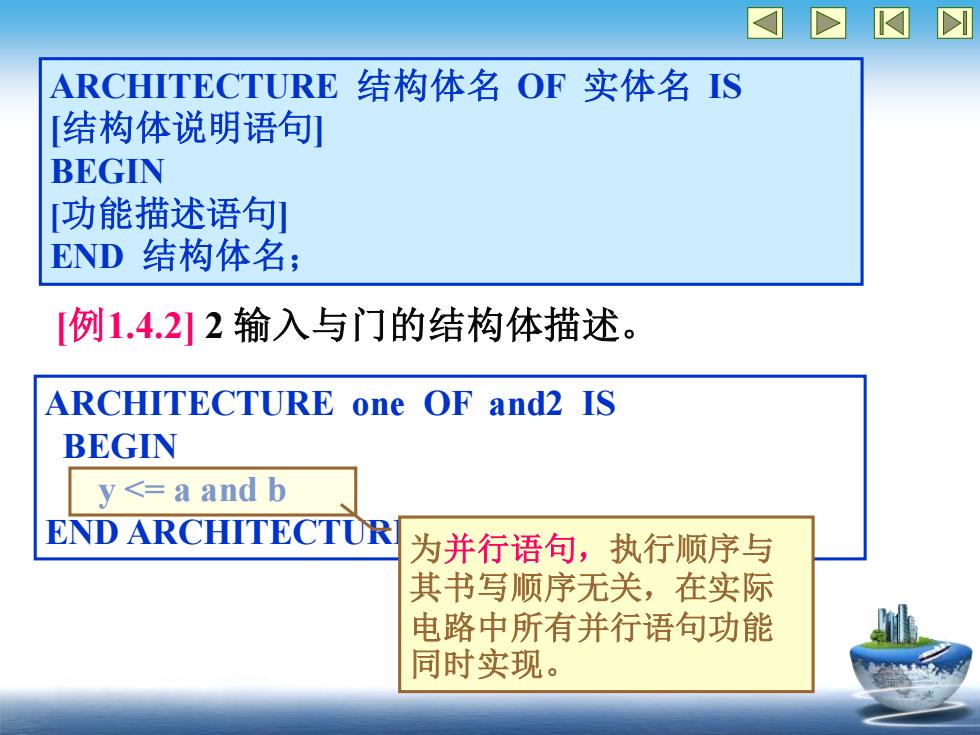

ARCHITECTURE结构体名OF实体名IS 结构体说明语句] BEGIN 功能描述语句] END结构体名; [例1.4.212输入与门的结构体描述。 ARCHITECTURE one OF and2 IS BEGIN y<=a and b END ARCHITECTURI 为并行语句,执行顺序与 其书写顺序无关,在实际 电路中所有并行语句功能 同时实现

ARCHITECTURE 结构体名 OF 实体名 IS [结构体说明语句] BEGIN [功能描述语句] END 结构体名; [例1.4.2] 2 输入与门的结构体描述。 ARCHITECTURE one OF and2 IS BEGIN y <= a and b END ARCHITECTURE one 为并行语句, ; 执行顺序与 其书写顺序无关,在实际 电路中所有并行语句功能 同时实现