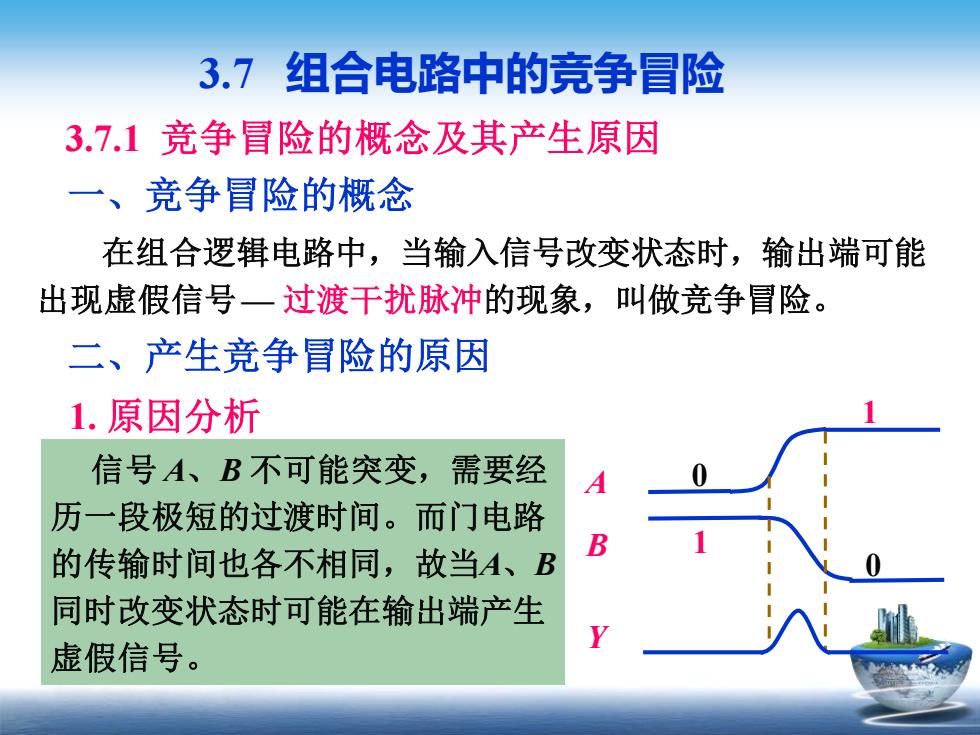

3.7组合电路中的竞争冒险 3.7.1竞争冒险的概念及其产生原因 一、竞争冒险的概念 在组合逻辑电路中,当输入信号改变状态时,输出端可能 出现虚假信号一过渡干扰脉冲的现象,叫做竞争冒险。 二、产生竞争冒险的原因 1.原因分析 信号A、B不可能突变,需要经 历一段极短的过渡时间。而门电路 B 的传输时间也各不相同,故当A、B 同时改变状态时可能在输出端产生 虚假信号

3.7 组合电路中的竞争冒险 3.7.1 竞争冒险的概念及其产生原因 一、竞争冒险的概念 在组合逻辑电路中,当输入信号改变状态时,输出端可能 出现虚假信号— 过渡干扰脉冲的现象,叫做竞争冒险。 二、产生竞争冒险的原因 1. 原因分析 A & B Y 0 1 1 0 A B Y 信号 A、B 不可能突变,需要经 历一段极短的过渡时间。而门电路 的传输时间也各不相同,故当A、B 同时改变状态时可能在输出端产生 虚假信号

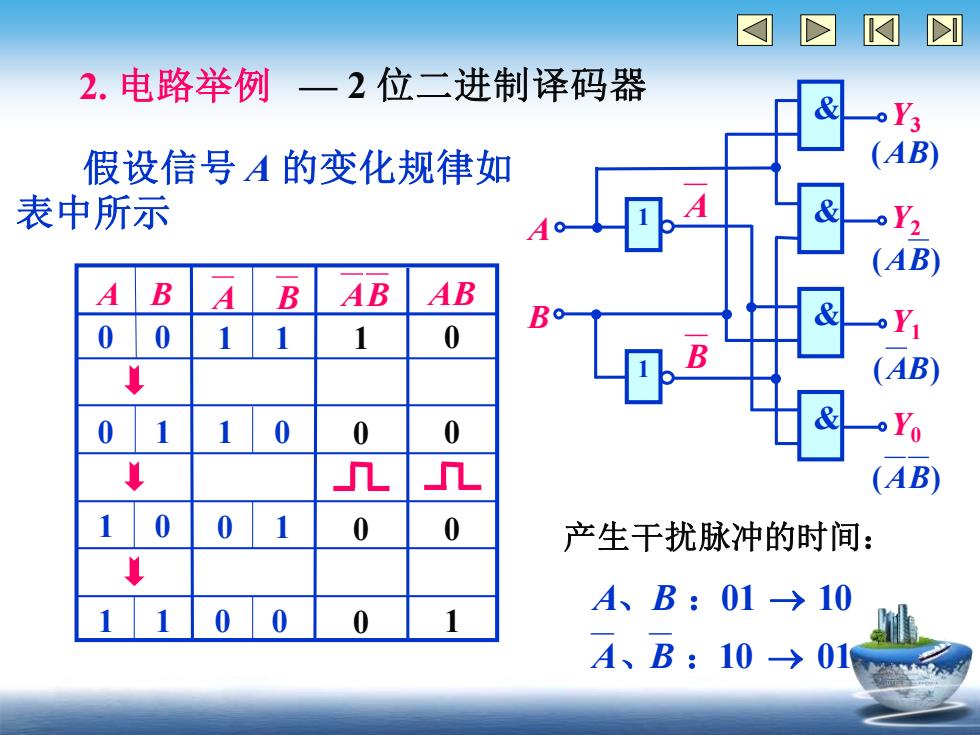

2.电路举例一2位二进制译码器 假设信号A的变化规律如 表中所示 B A B AB AB B 0 0 1 0 0 0 0 0 & 4 几 几 (AB) 0 0 0 产生干扰脉冲的时间: A、B:01→10 A、B:10→01

2. 电路举例 & Y3 & Y1 & Y2 & Y0 A 1 B 1 A — 2 位二进制译码器 B (AB) (AB) (AB) (AB) 假设信号 A 的变化规律如 表中所示 A B 0 0 0 1 1 0 1 1 A B AB AB 1 1 1 0 0 1 0 0 1 0 0 0 0 0 0 1 产生干扰脉冲的时间: A、B : 01 → 10 A、 B : 10 → 01

I 3.7.2消除竞争冒险的方法 三、接入滤波电容 Y B P P, P 存在的问题: 导致输出波形的边沿变坏

3.7.2 消除竞争冒险的方法 一、引入封锁脉冲 & Y3 & Y1 & Y2 & Y0 A 1 B 1 P1 A B A B A B P1 二、引入选通脉冲 P2 P2 存在的问题: 对封锁脉冲和选通脉冲的宽度和产生时间有 严格的要求。 三、接入滤波电容 Cf Cf 导致输出波形的边沿变坏

3.7.2消除竞争冒险的方法 四、修改逻辑设计增加冗余项 例如:Y=AB+AC◆Y=AB+AC+BC AC BC & BC 00 01 1110 0 0 AB 由于修改设计方案得当,收到了较好的效果

四、修改逻辑设计增加冗余项 3.7.2 消除竞争冒险的方法 & & & & A B C A G1 G2 G3 G4 Y & G5 A BC 0 1 00 01 11 10 1 1 1 0 0 1 0 0 例如: Y = AB+ AC Y = AB+ AC + BC AC AB BC 由于修改设计方案得当,收到了较好的效果