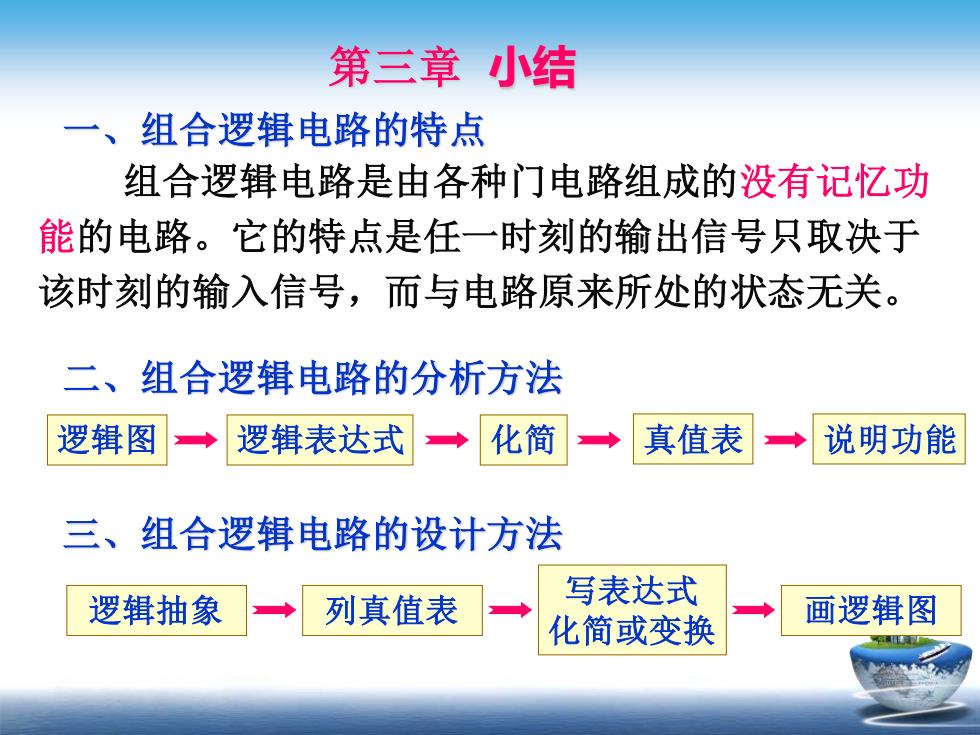

第三章小结 一、组合逻辑电路的特点 组合逻辑电路是由各种门电路组成的没有记忆功 能的电路。它的特点是任一时刻的输出信号只取决于 该时刻的输入信号,而与电路原来所处的状态无关。 二、组合逻辑电路的分析方法 逻辑图 逻辑表达式 化简 真值表 说明功能 三、组合逻辑电路的设计方法 逻辑抽象 列真值表 写表达式 化简或变换 画逻辑图

第三章 小结 一、组合逻辑电路的特点 组合逻辑电路是由各种门电路组成的没有记忆功 能的电路。它的特点是任一时刻的输出信号只取决于 该时刻的输入信号,而与电路原来所处的状态无关。 逻辑图 逻辑表达式 化简 真值表 说明功能 二、组合逻辑电路的分析方法 三、组合逻辑电路的设计方法 逻辑抽象 列真值表 写表达式 化简或变换 画逻辑图

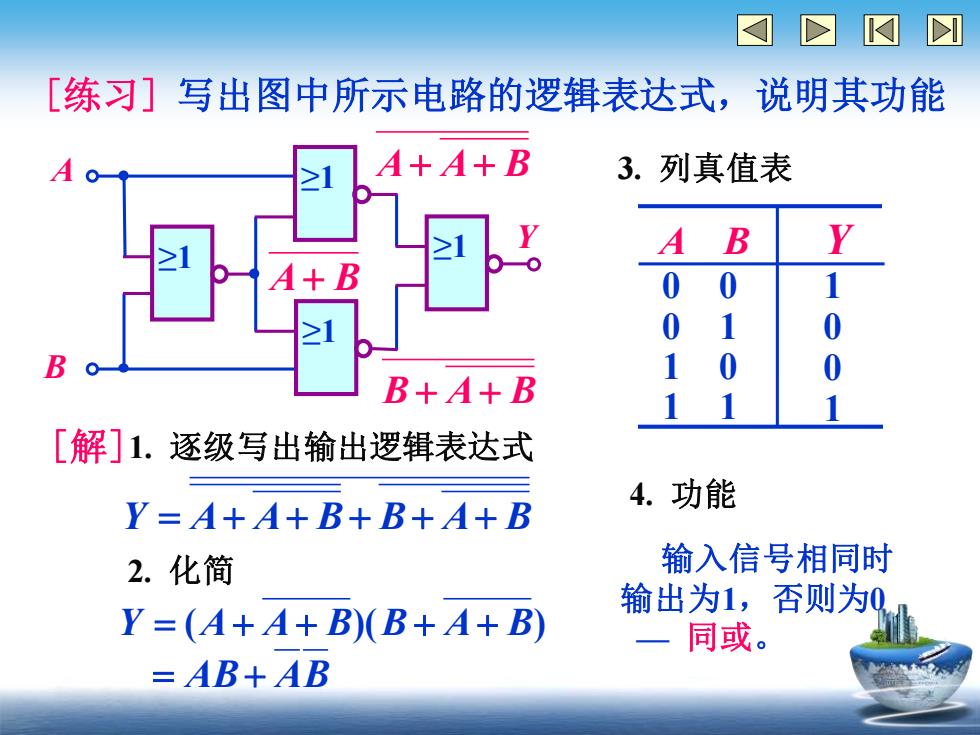

D☑I [练习]写出图中所示电路的逻辑表达式,说明其功能 A+4+B 3.列真值表 A B 0 0 0 0 10 B+4+B 11 [解]1.逐级写出输出逻辑表达式 4.功能 Y=4+4+B+B+4+B 2.化简 输入信号相同时 输出为1,否则为0 Y=(4+4+B(B+4+B) 一同或。 =AB+AB

[练习] 写出图中所示电路的逻辑表达式,说明其功能 A B ≥1 Y ≥1 ≥1 ≥1 [解]1. 逐级写出输出逻辑表达式 A+ B A+ A+ B B + A+ B Y = A+ A+ B+ B+ A+ B 2. 化简 Y = (A+ A+ B)(B + A+ B) = AB+ AB 3. 列真值表 A B Y 0 0 0 1 1 0 1 1 1 0 0 1 4. 功能 输入信号相同时 输出为1,否则为0 — 同或

四、常用中规模集成组合逻辑电路 1.加法器:实现两组多位二进制数相加的电路。 根据进位方式不同,可分为串行进位加法 器和超前进位加法器。 集成芯片: 74LS183(TTL)、C661(CMOS)一双全加器 两片双全加器(如74LS183)→四位串行进位加法器 74283、74LS283(TTL) CC4008 (CMOS) 一四位二进制超前进位加法器 2.数值比较器:比较两组多位二进制数大小的电路。 集成芯片:7485、74L85(TTL) CC14585、C663(CMOS)一四位数值比有

四、常用中规模集成组合逻辑电路 1. 加法器:实现两组多位二进制数相加的电路。 根据进位方式不同,可分为串行进位加法 器和超前进位加法器。 2. 数值比较器:比较两组多位二进制数大小的电路。 集成芯片: 74LS183(TTL)、C661(CMOS)—双全加器 两片双全加器(如74LS183)→ 四位串行进位加法器 74283、74LS283(TTL) CC4008(CMOS) — 四位二进制超前进位加法器 集成芯片: 7485、74L 85(TTL) CC14585、C663(CMOS) — 四位数值比较器

3.编码器:将输入的电平信号编成二进制代码的电路。 主要包括二进制编码器、二-十进制编码 器和优先编码器等。 集成芯片: 74148、74LS148、74LS348(TTL)一8线-3线优先编码器 74147、74LS147(TTL)一10线-4线优先编码器 4.译码器:将输入的二进制代码译成相应的电平信号。 主要包括二进制译码器、二-十进制译码 器和显示译码器等。 集成芯片: 74LS138(TTL)一3线-8线译码器(二进制译码器) 7442、74LS42(TTL)一4线-10线译码器 74247、74LS247(TTL)一共阳极显示译码器 7448、74248、7449、74249等(TTL)一共阴极显示译码器

3. 编码器:将输入的电平信号编成二进制代码的电路。 主要包括二进制编码器、二 – 十进制编码 器和优先编码器等。 4. 译码器:将输入的二进制代码译成相应的电平信号。 主要包括二进制译码器、二 – 十进制译码 器和显示译码器等。 集成芯片: 74148、74LS148、74LS348(TTL)— 8 线 – 3 线优先编码器 74147、74LS147(TTL)— 10 线 – 4 线优先编码器 集成芯片: 74LS138(TTL)— 3线 – 8线译码器(二进制译码器) 7442、74LS42(TTL)— 4线 – 10线译码器 74247、74LS247(TTL)— 共阳极显示译码器 7448、74248、7449、74249等(TTL)—共阴极显示译码器

I 5.数据选择器:在地址码的控制下,在同一时间内从 多路输入信号中选择相应的一路信号 输出的电路。常用于数据传输中的并 串转换。 集成芯片: 74151、74LS151 74251、74LS251(TTL)一8选1数据选择器 6.数据分配器:在地址码的控制下,将一路输入信号 传送到多个输出端的任何一个输出端 的电路。常用于数据传输中的串-并转 换。 集成芯片:无专用芯片,可用二进制集成译码器实现

5. 数据选择器:在地址码的控制下,在同一时间内从 多路输入信号中选择相应的一路信号 输出的电路。常用于数据传输中的并- 串转换。 集成芯片: 74151、74LS151 74251、74LS251(TTL)— 8 选 1 数据选择器 6. 数据分配器:在地址码的控制下,将一路输入信号 传送到多个输出端的任何一个输出端 的电路。常用于数据传输中的串-并转 换。 集成芯片: 无专用芯片,可用二进制集成译码器实现