●● SOC软硬件协同设计流程 ●●●● ●●● ●0 ●●●●0 ●●●● ●●0● ● ● Design Architecture IP Library Specification Estimators Description Language L Hw/Sw Partitioning HW SW Verification VHDL,Verilog Synthesis Compiler Cosimulation Rapid design space exploration On-Chip Quality tool-kit generation Care Off-Chip Memory Design reuse nterface 7

7 SOC软硬件协同设计流程

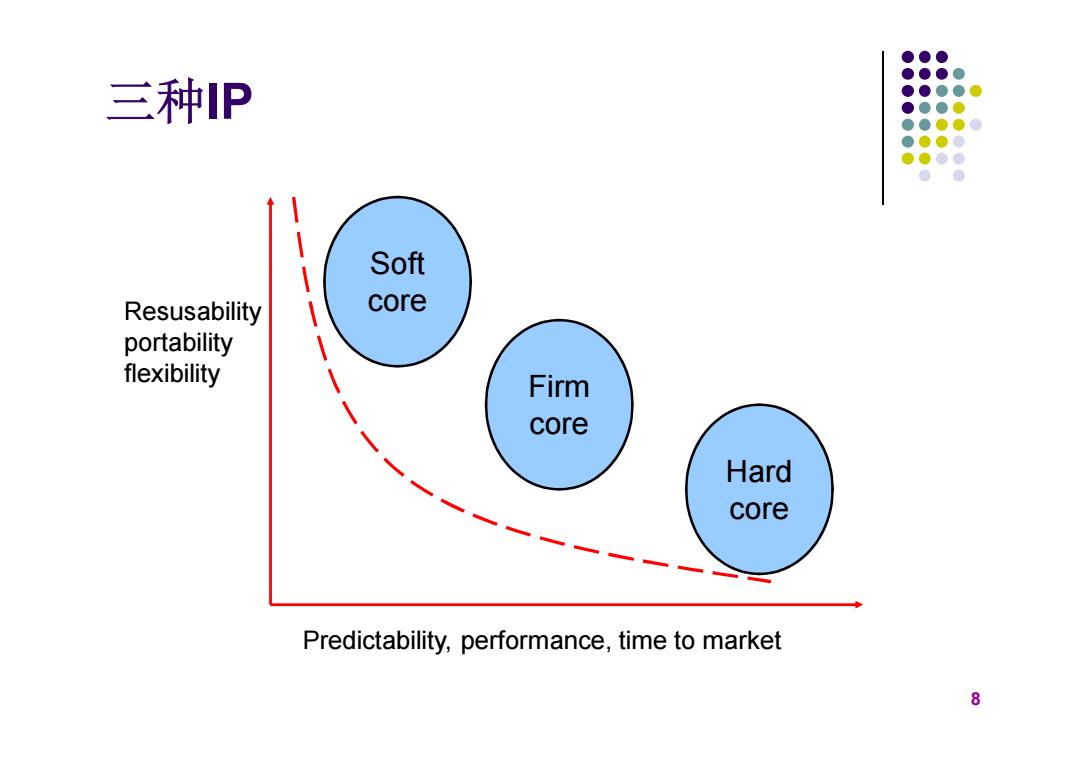

●● ●●● 三种IP ● ●● ●●0 ●●0● ● Soft Resusability core portability flexibility Firm core Hard core Predictability,performance,time to market 8

8 Resusability portability flexibility Predictability, performance, time to market Soft core Firm core Hard core 三种IP

●● ●●●● ●●●● 可复用核的分类 ●●● ●●●●0 ●●●● 类型 灵活性 设计流 表达 库 处理工 可携带性 程 艺 软核 非常灵 系统设 行为 无 无关 无限制 活 计 RTL 不可 RTL 测 固核 比较灵 版图 RTL, 参考 生成 库映射 活 布线 模块, 时间模 网表 型 硬核 不灵活 Routing Polygon 特定的 固定 过程映射 可预测 验证 数据 库和 设计 规律 9

9 可复用核的分类 类型 灵活性 设计流 程 表达 库 处理工 艺 可携带性 软核 非常灵 活 不可预 测 系统设 计 RTL 行为 RTL 无 无关 无限制 固核 比较灵 活 版图 布线 RTL, 模块, 网表 参考 时间模 型 生成 库映射 硬核 不灵活 可预测 Routing 验证 Polygon 数据 特定的 库和 设计 规律 固定 过程映射