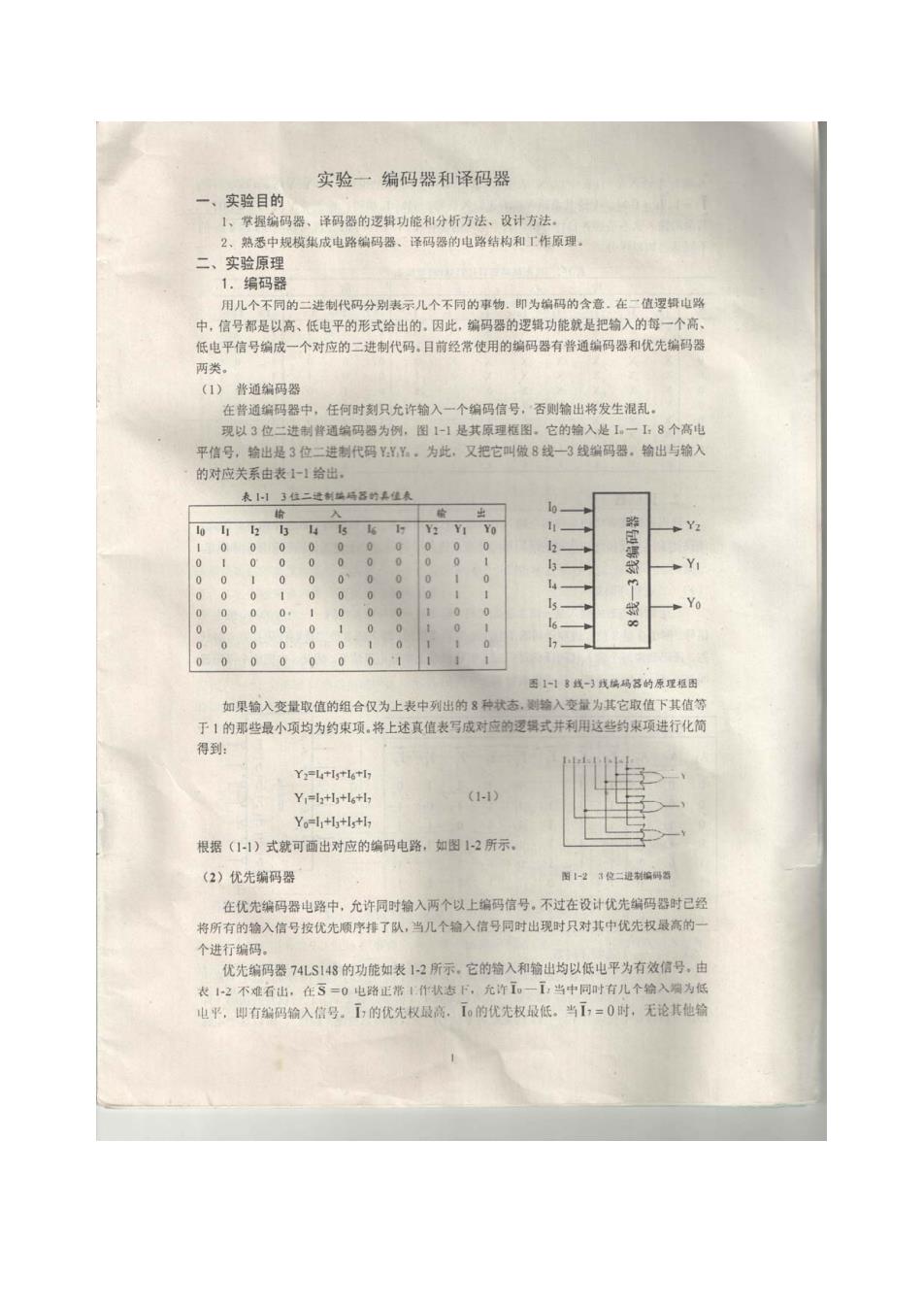

实验一编码器和译码器 一、实验目的 1、掌握编码器、译码器的逻辑功能和分析方法、设计方法 2、熟悉中规模集成电路编码器、译码器的电路结构和工作原理。 二、实验原理 1.编码器 用儿个不同的二进制代码分别表示儿个不同的事物.即为编码的含意.在二值逻辑电路 中,信号都是以高、低电平的形式给出的。因此,编码器的逻辑功能就是把输入的每一个高、 低电平信号编成一个对应的二进制代码。目前经常使用的编码器有普通编码器和优先编码器 两类。 (1)普通编码器 在普通编码器中,任何时刻只允许输入一个编码信号,否则输出将发生混乱。 现以3位二进制管通编码器为例,图1-1是其原理框图,它的输入是1一1五8个高电 平信号,输出是3位二进制代码Y,为此,又把它叫做8线一3线编码器。输出与输入 的对应关系由表1-1给出 表1问13位二进制编局器的具但表 Y2 YI +Y2 0 0 0 000 0 0 6 0 0000 0 YI 0 0 001 0 0 00 0 0 0 0 0 0 0 0 0 0. 0 Yo 1 0 0 0 0 0 0 0 0 0 0 0 0 0 00 0 0 图1-18线-3线编码器的原理框图 如果输入变量取值的组合仅为上表中列出的8种状态,则输入变量为其它取值下其值等 于1的那些最小项均为约束项,将上述真值表写成对应的逐辑式并利用这些约束项进行化简 得到: Y2=L+1+l6+1 Y=+1+16+1 (1-1) Yo=l+lj+ls+l 根据(1-1)式就可画出对应的编码电路,如图1-2所示。 (2)优先编码器 图1-23位二进制编码器 在优先编码器电路中,允许同时输入两个以上编码信号,不过在设计优先编码器时已经 将所有的输入信号按优先顺序排了队,当几个输入信号同时出现时只对其中优先权最高的 个进行编码。 优先编码器74LS143的功能如表1-2所示,它的输入和输出均以低电平为有效信号,由 农12不难石出,在S=0电路正带1作状志下,允许。一当中同时有儿个输入端为低 电平,即有编码输入信号。的优先权最高。0的优先权最低。当=0时,无论其他输

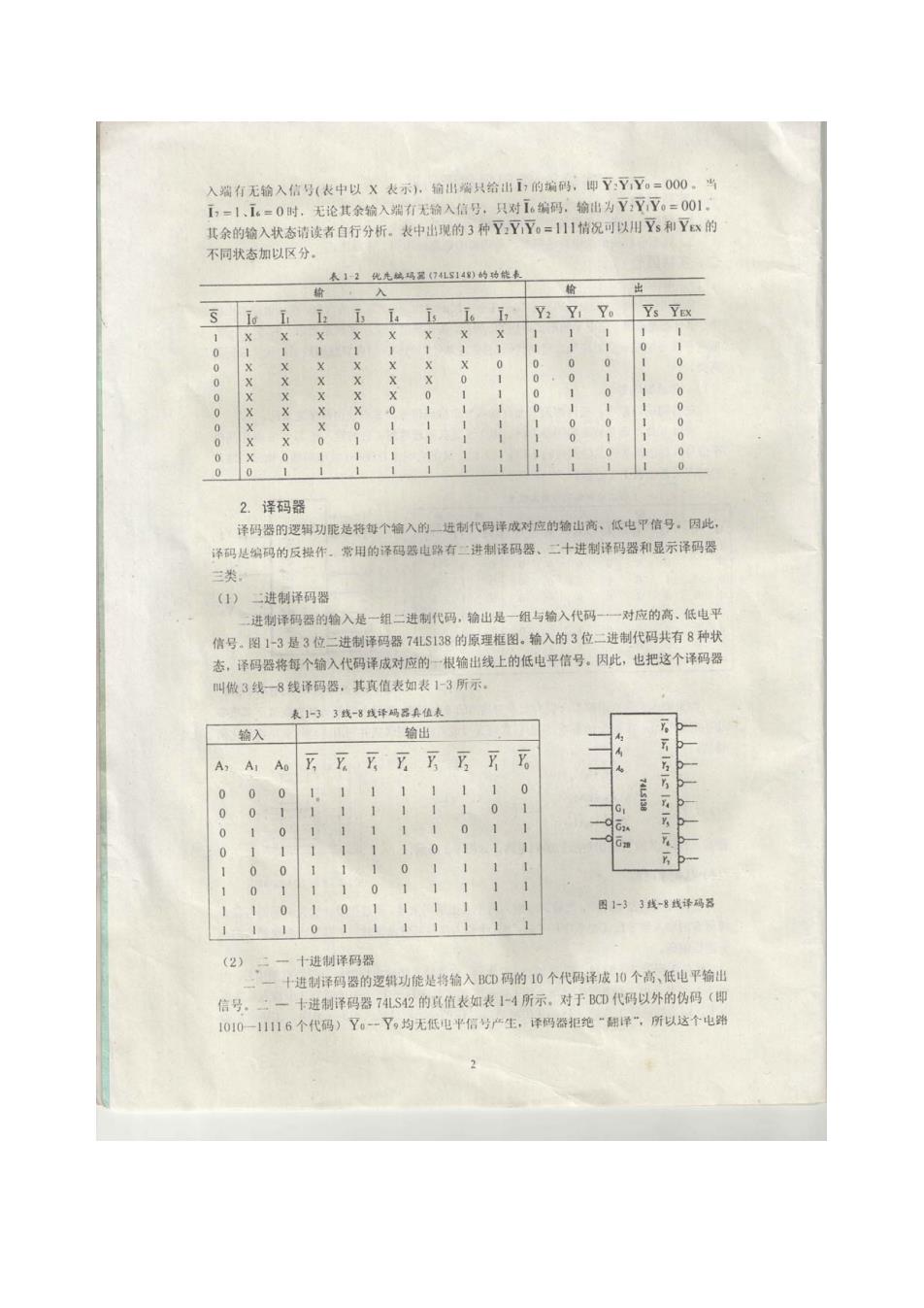

入端有无输入信号(表中以X表示),输端只给出1,的编码,即了:YY。=000。当 5=1、1=0时,无论其余输入端有无输入信号,只对i6编码,输出为V:了了0=001。 其余的输入状态请读者自行分析。表中出现的3种TT下。=111情况可以用s和Yx的 不同状态加以区分, 表】2化先铭码器(7LS148)的功能表 入 出 Y3YY。 Ys YEx X 1 0 0 X 0 0 0 0 0 0 0 0 0 0 X X X X X 0 0 1 0 1 0 0 X X 0 0 0 0 0 0 X X 0 0 0 0 0 0 0 2.译码器 译码器的逻辑功能是将每个输入的进制代码译成对应的输山高、低电平信号。因此, 译码是编码的反操作.常用的译码器电路有二进制译码器、二十进制译码器和显示译码器 三类 (1)二进制译码器 进制译码器的输入是一组二进制代码,输出是一组与输入代码一对应的高、低电平 信号。图1-3是3位二进制译码器74S138的原理框图。输入的3位二进制代码共有8种状 态,译码器将每个输入代码译成对应的一根输出线上的低电平信号。因此,也把这个译码器 叫做3线一8线译码器,其真值表如表13所示, 表1-33线-8线译妈器真仙表 输入 输出 A A1 Ao Y.YYY耳。 g 0 0 0 1111 1 0 0 0 1 1 0 0 1 0 1 1 1 0 d 0 1 1 1 0 1 1 0 0 0 1 01 0 11 0 0 图1-33线-8线译码器 1 0 (2)三 十进制译码器 十进制译码器的逻辑功能是将输入BD码的10个代码译成0个高、低电平输出 信号。二一十进制译码器74S2的真值表如表14所示,对于BCD代码以外的伪码(即 1010一11116个代码)了。一Y,均无低电平信号产生,译码器拒绝“翻译“,所以这个电路

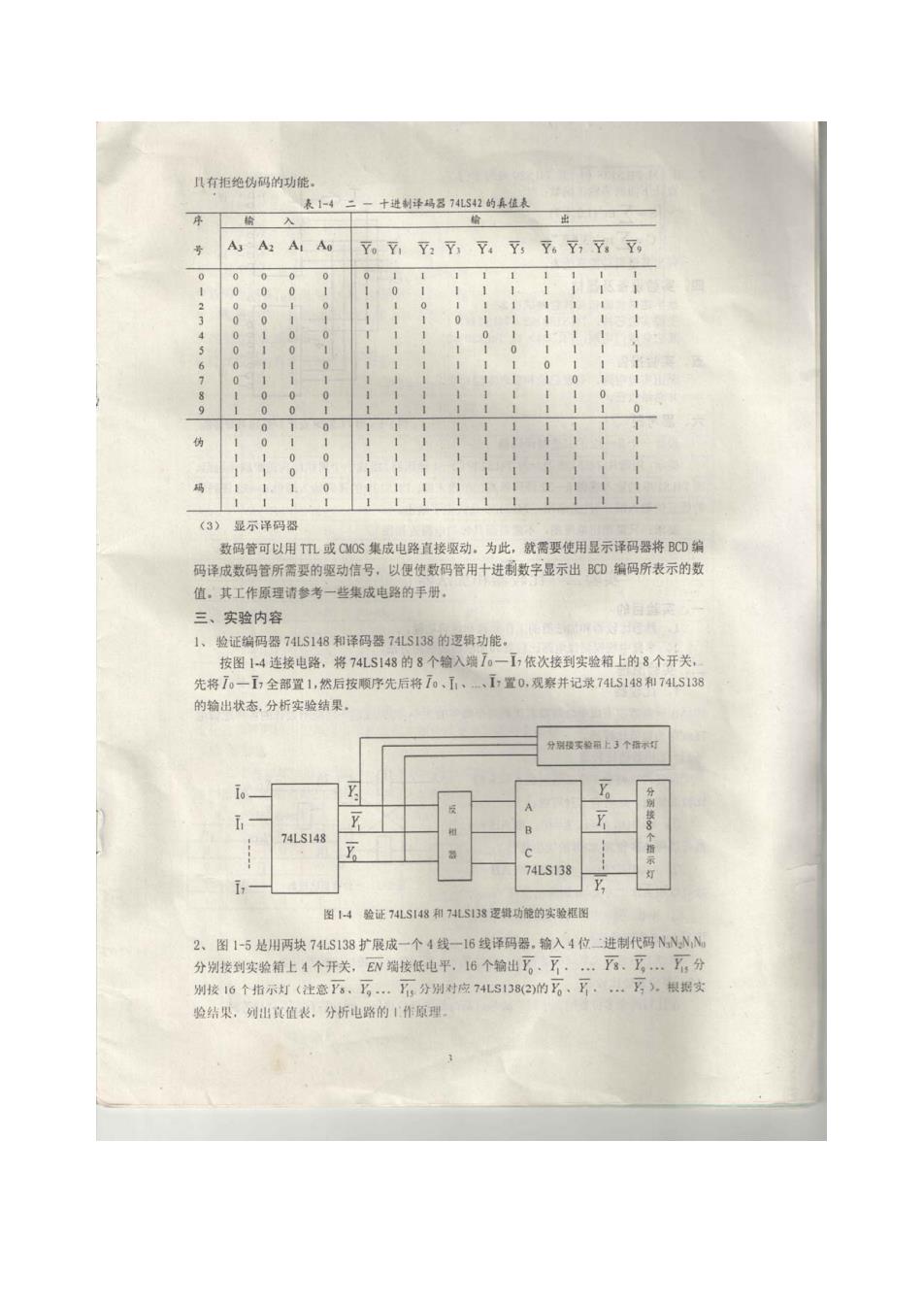

具有拒绝伪码的功能。 表1-4二一十进制译妈器74LS42的真值表 序输入 出 A3 A2 Al Ao Y。Y72Y74T;7.7,7g7 0 0 0 0 0 0 0 2 0 0 3 0 0 0 0 0 0 0 6 0 1 0 0 0 0 0 9 0 0 0 0 0 0 0 0 (3)显示译码器 数码管可以用TTL或COS集成电路直接驱动。为此,就需要使用显示译码器将BCD编 码译成数码管所需要的驱动信号,以便使数码管用十进制数字显示出D编码所表示的数 值。其工作原理请参考一些集成电路的手册。 三、实验内容 1、验证编码器74LS148和译码器74S138的逻辑功能。 按图14连接电路,将74LS148的8个输入端70一,依次接到实验箱上的8个开关, 先将0一1,全部置1,然后按顺序先后将10、1、、置0观察并记录74S148和74S138 的输出状态,分析实验结果 分别接实验而上3个指不可 Io_ 国 74LS148 分别接8个指示 74LS138 图14验证74LS48和74LS138逻辑功能的实验框图 2、图1-5是用两块74S138扩展成一个4线一16线译码器.输入4位二进制代码NNN 分捌接到实验箱上4个开关,N端接低电平,16个输出了。、了.。.…分 州接16↑指示灯(注意..…,分别对应74礼S138(2)的写、了。..写).根据实 验结果,列出真值表,分析电路的1作原理

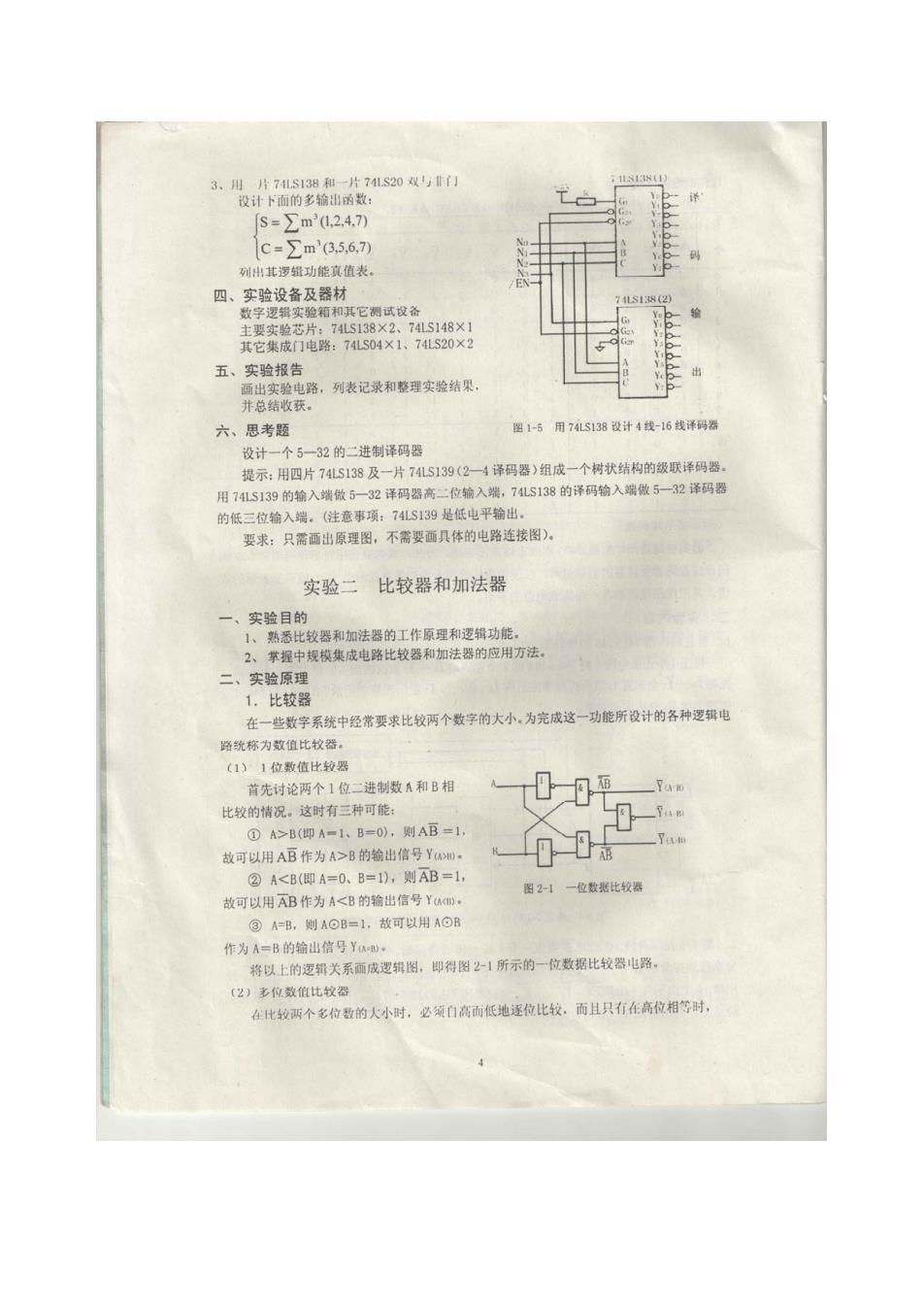

3、用片71S138和一片741S20双与门 设计下面的多输出函数: s=∑m'1.24.刀 C=∑m'(35,6,7) 列出其逻辑功能真值表, 四、实验设备及器材 数字逻辑实验箱和其它测试设备 主要实验芯片:74LS138×2、741S148×1 其它集成门电路:74LS04×1、74LS20×2 五、实验报告 画出实验电路,列表记录和整理实验结果。 并总结收获。 六、思考题 图1-5用74LS138设计4线-16线译码器 设计一个5一32的二进制译码器 提示:用四片741S138及一片741S139(2一4译码器)组成一个树状结构的级联译码器。 用74S139的输入端做5一32译码器高二位输入端,74S138的译码输入端做5一32译码器 的低三位输入端。(注意事项:74LS139是低电平输出。 要求:只需画出原理图,不需要画具体的电路连接图)。 实验二比较器和加法器 一、实验目的 1、熟悉比较器和加法器的工作原理和逻辑功能。 2、掌握中规模集成电路比较器和加法器的应用方法, 二、实验原理 1.比较器 在一些数字系统中经常要求比较两个数字的大小,为完成这一功能所设计的各种逻辑电 路统称为数值比较器 (1)1位数值比较器 首先讨论两个1位二进制数A和B相 比较的情况。这时有三种可能: ①A>B(即A-1、B=0),则AB=1 故可以用AB作为A>B的输出信号Y: ②A<B(即A=0、B=1),则AB=1, 图2-1一位数据比较器 故可以用AB作为A<B的输出信号Ya, ③A=B,则A⊙B=1,故可以用A⊙B 作为A=B的输出信号YA:D, 将以上的逻辑关系画成逻辑图,即得图21所示的一位数据比较器电路 (2)多位数值比较器 在比较两个多位数的大小时,必须自高而低地逐位比纹,而且只有在高位相等时

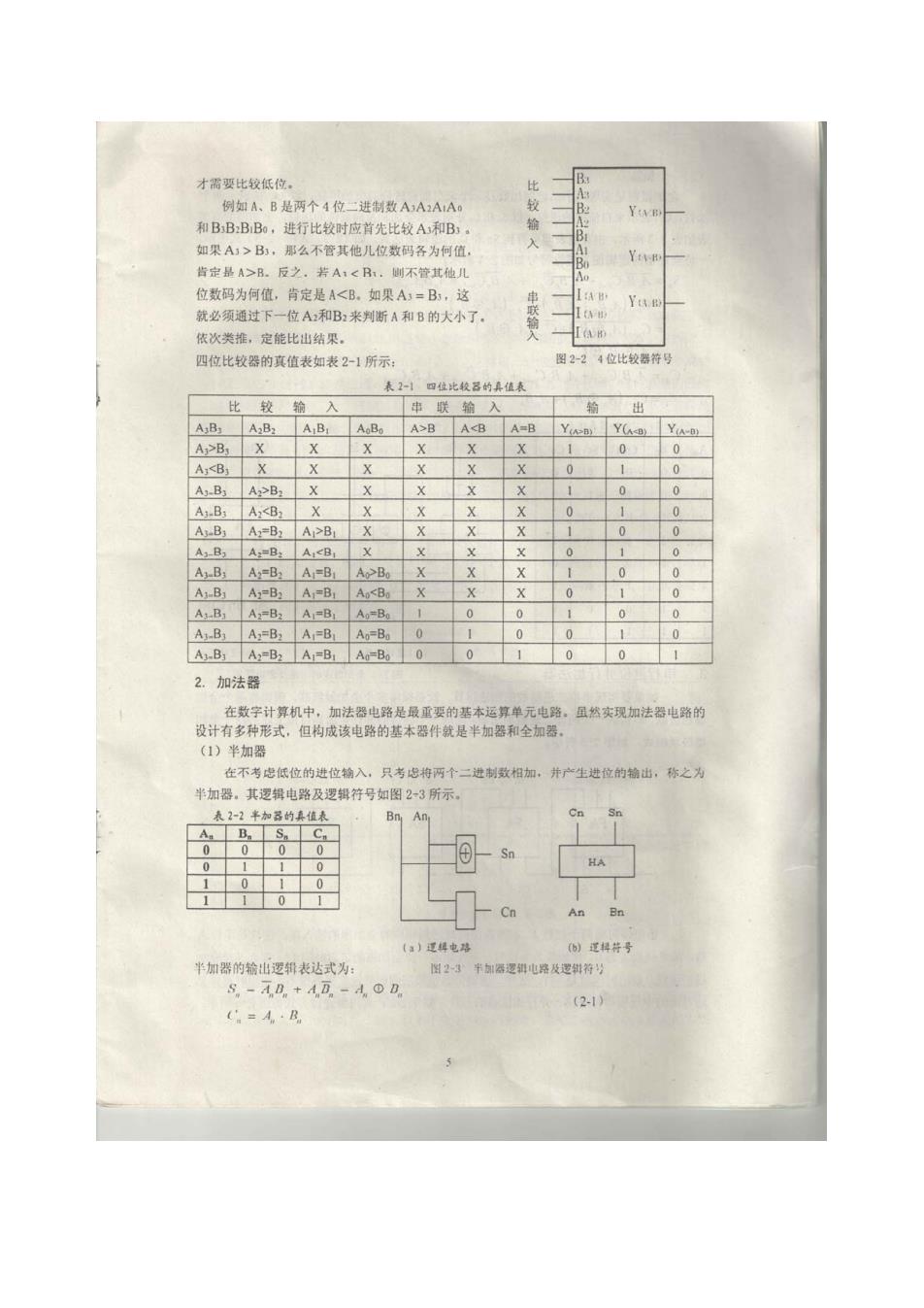

才需要比较低位 B 例如A、B是两个4位三进制数AA2AIA0 Y.vB 和3B:BiBo,进行比较时应首先比较A和B1。 输 B 如果A>B,那么不管其他几位数码各为何值, 入 告定是A>B.反之。若A1<B:,则不管其他儿 位数码为何值,肯定是A<B.如果A3=B,这 就必须通过下一位A:和B:来判断A和B的大小了, 依次类推,定能比出结果。 联输入 四位比较器的真值表如表2-1所示 图2-24位比较器符号 表2四位比较器的真值表 比较输入 申联输入 输 出 A:B A2B2 A:B:AoBo A>B A<B A=B Y(-B) Y(AsB) Y(A-B) A)>By X X X X X X 1 0 0 A3<B1 X X X X 0 1 0 A3-B3 A2>B2 X X X X X 1 0 0 A2-B:A2<B X X X X 0 1 0 A-B3 A2=B2 A>B X X X X 1 0 0 A2-B:A:=B: A1<B1 0 1 0 A1-B: A2=B2 A=B Ao>Bo X X X 0 0 A1-B1 A2=B2 A=B A0<Bo X X X 0 1 0 A-B A2=B2 A=B Ao=Bo 1 0 0 1 0 0 A3-B3 A2=B2A=B1 Ao=Bo0 0 0 A)-B3 A2=B2 A=B:Ao=Bo 0 0 0 0 2.加法器 在数字计算机中,加法器电路是最重要的基本运算单元电路。虽然实现加法器电路的 设计有多种形式,但构成该电路的基本器件就是半加器和全加器。 (1)半加器 在不考虑低位的进位输入,只考虑将两个二进制数相加,并广生进位的输出,称之为 半加器。其逻辑电路及逻辑符号如图2-3所示 表2-2半加器的真值表 Bn An A.B。S。C 0 0 0 Sn 0 0 HA 0 0 Cn An日 (a)道镇电塔 6)辽抖特号 半加器的输出逻辑表达式为: 图2-3半如器逻辑电路及逻辑符号 S。-ADn+4Dn-A0D (2-1) (=A·B