中国绅学我术大学 University of Science and Technology of China 第四章组合逻辑电路 本章目录 >4.1概述 >4.2组合逻辑电路的分析方法 >4.3组合逻辑电路的基本设计方法 >4.4若干常用的组合逻辑电路模块 >4.5层次化和模块化的设计方法 >4.6可编程逻辑器件 >4.7 硬件描述语言 >4.8用可编程通用模块设计组合逻辑电路 >4.9组合逻辑电路中的竞争一冒险 2017-8-4 第四章组合逻辑电路 §4.1概述 数字逻辑电路分类:组合逻辑电路和时序逻辑电路。 一、组合逻辑电路的特点 组合逻辑电路逻辑功能特点:任意时刻的输出仅取决于该 时刻的输入,与电路原来的状态无关。 组合逻辑电路电路结构特点:不能包含有存储单元。 二、逻辑功能的描述 a1- y=f(a1,a2,…,an) a2- 组合逻辑 -y2 2=f3(a1,a2,…,an) : 电路 ym ym=fn(a1,a2,…,an) 组合逻辑电路的框图 Y=F(A) 2017-8-4 第四章组合逻辑电路 2

2017-8-4 第四章 组合逻辑电路 1 第四章 组合逻辑电路 第四章 组合逻辑电路 本章目录 ¾4.1 概述 ¾4.2 组合逻辑电路的分析方法 ¾4.3 组合逻辑电路的基本设计方法 ¾4.4 若干常用的组合逻辑电路模块 ¾4.5 层次化和模块化的设计方法 ¾4.6 可编程逻辑器件 ¾4.7 硬件描述语言 ¾4.8 用可编程通用模块设计组合逻辑电路 ¾4.9 组合逻辑电路中的竞争-冒险 2017-8-4 第四章 组合逻辑电路 2 §4.1 概述 一、组合逻辑电路的特点 数字逻辑电路分类:组合逻辑电路和时序逻辑电路。 组合逻辑电路逻辑功能特点:任意时刻的输出仅取决于该 时刻的输入,与电路原来的状态无关。 组合逻辑电路电路结构特点:不能包含有存储单元。 二、逻辑功能的描述 组合逻辑电路的框图 Y = F(A) ( , , , ) ( , , , ) ( , , , ) 1 2 2 2 1 2 1 1 1 2 m m n n n y f a a a y f a a a y f a a a L M L L = = =

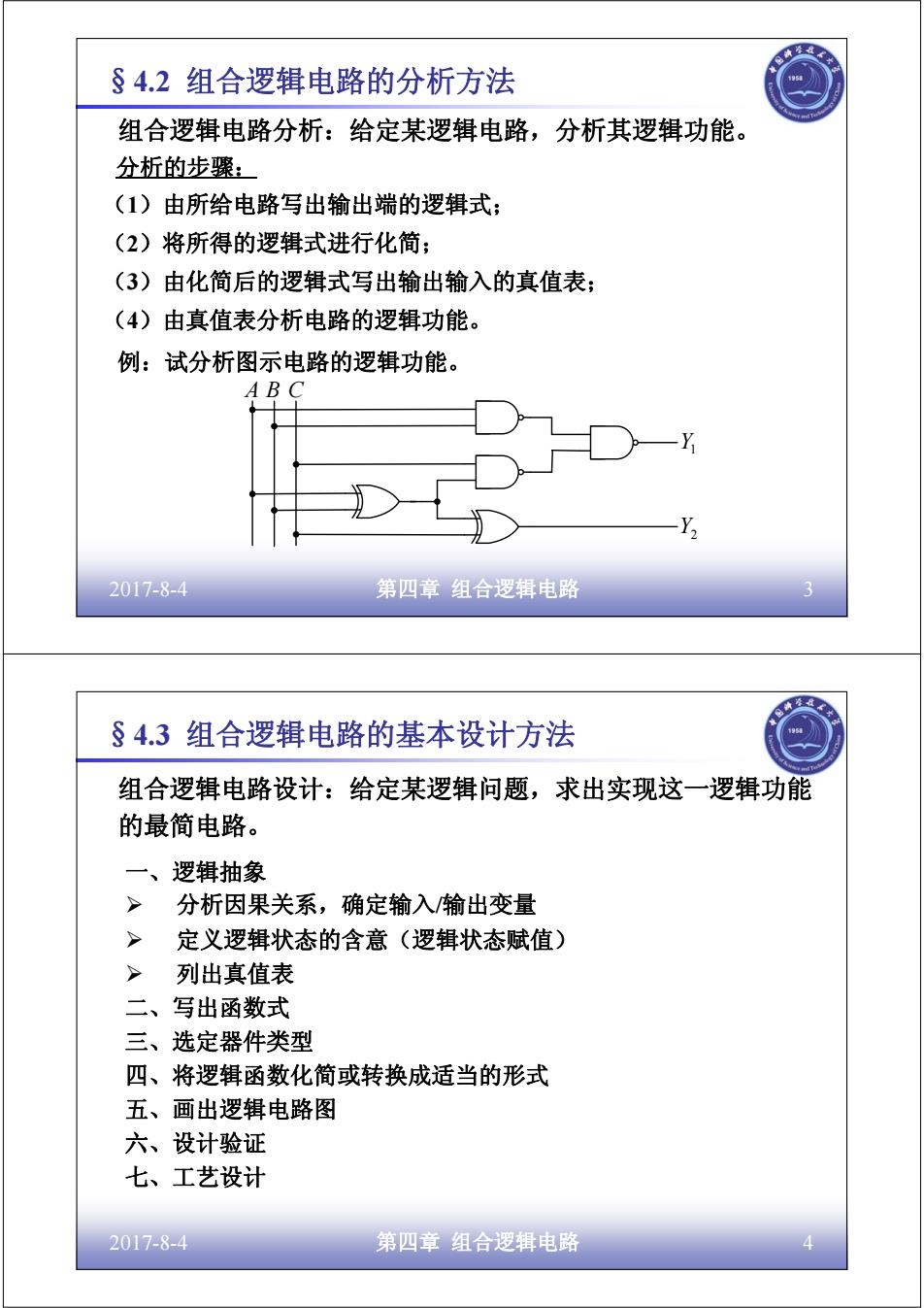

§4.2组合逻辑电路的分析方法 组合逻辑电路分析:给定某逻辑电路,分析其逻辑功能。 分析的步骤: (1)由所给电路写出输出端的逻辑式; (2)将所得的逻辑式进行化简; (3)由化简后的逻辑式写出输出输入的真值表; (4)由真值表分析电路的逻辑功能。 例:试分析图示电路的逻辑功能。 ABC 2017-8-4 第四章组合逻辑电路 §4.3组合逻辑电路的基本设计方法 组合逻辑电路设计:给定某逻辑问题,求出实现这一逻辑功能 的最简电路。 一、逻辑抽象 分析因果关系,确定输入输出变量 定义逻辑状态的含意(逻辑状态赋值) 列出真值表 二、写出函数式 三、选定器件类型 四、将逻辑函数化简或转换成适当的形式 五、画出逻辑电路图 六、设计验证 七、工艺设计 2017-8-4 第四章组合逻辑电路

2017-8-4 第四章 组合逻辑电路 3 §4.2 组合逻辑电路的分析方法 组合逻辑电路分析:给定某逻辑电路,分析其逻辑功能。 分析的步骤: (1)由所给电路写出输出端的逻辑式; (2)将所得的逻辑式进行化简; (4)由真值表分析电路的逻辑功能。 (3)由化简后的逻辑式写出输出输入的真值表; 例:试分析图示电路的逻辑功能。 A B C Y1 Y2 2017-8-4 第四章 组合逻辑电路 4 一、逻辑抽象 ¾ 分析因果关系,确定输入/输出变量 ¾ 定义逻辑状态的含意(逻辑状态赋值) ¾ 列出真值表 二、写出函数式 三、选定器件类型 四、将逻辑函数化简或转换成适当的形式 五、画出逻辑电路图 六、设计验证 七、工艺设计 §4.3 组合逻辑电路的基本设计方法 组合逻辑电路设计:给定某逻辑问题,求出实现这一逻辑功能 的最简电路

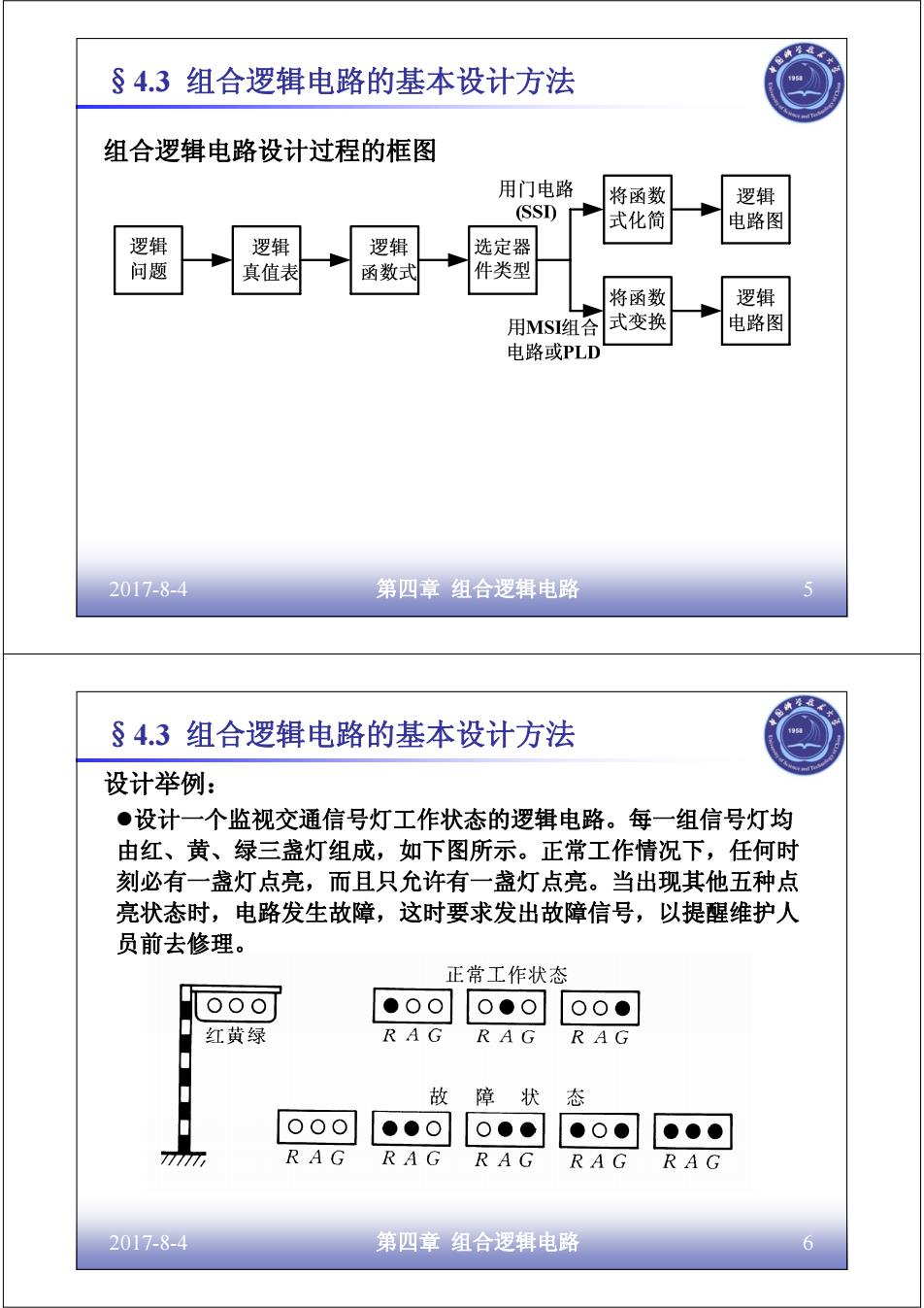

§4.3组合逻辑电路的基本设计方法 组合逻辑电路设计过程的框图 用门电路 将函数 逻辑 (SSD 式化简 电路图 逻辑 逻辑 逻辑 选定器 问题 真值表 函数式 件类型 将函数 逻辑 用MSI组合 式变换 电路图 电路或PLD 2017-8-4 第四章组合逻辑电路 §4.3组合逻辑电路的基本设计方法 设计举例: ·设计一个监视交通信号灯工作状态的逻辑电路。每一组信号灯均 由红、黄、绿三盏灯组成,如下图所示。正常工作情况下,任何时 刻必有一盏灯点亮,而且只允许有一盏灯点亮。当出现其他五种点 亮状态时,电路发生故障,这时要求发出故障信号, 以提醒维护人 员前去修理。 正常工作状态 O00 ●0 0●0 O0● 红黄绿 RAG RAG RAG 故 障 状 态 O00 ●●0 0●● RAG RAG RAG RAG RAG 2017-8-4 第四章组合逻辑电路 6

2017-8-4 第四章 组合逻辑电路 5 §4.3 组合逻辑电路的基本设计方法 组合逻辑电路设计过程的框图 2017-8-4 第四章 组合逻辑电路 6 设计举例: z设计一个监视交通信号灯工作状态的逻辑电路。每一组信号灯均 由红、黄、绿三盏灯组成,如下图所示。正常工作情况下,任何时 刻必有一盏灯点亮,而且只允许有一盏灯点亮。当出现其他五种点 亮状态时,电路发生故障,这时要求发出故障信号,以提醒维护人 员前去修理。 §4.3 组合逻辑电路的基本设计方法

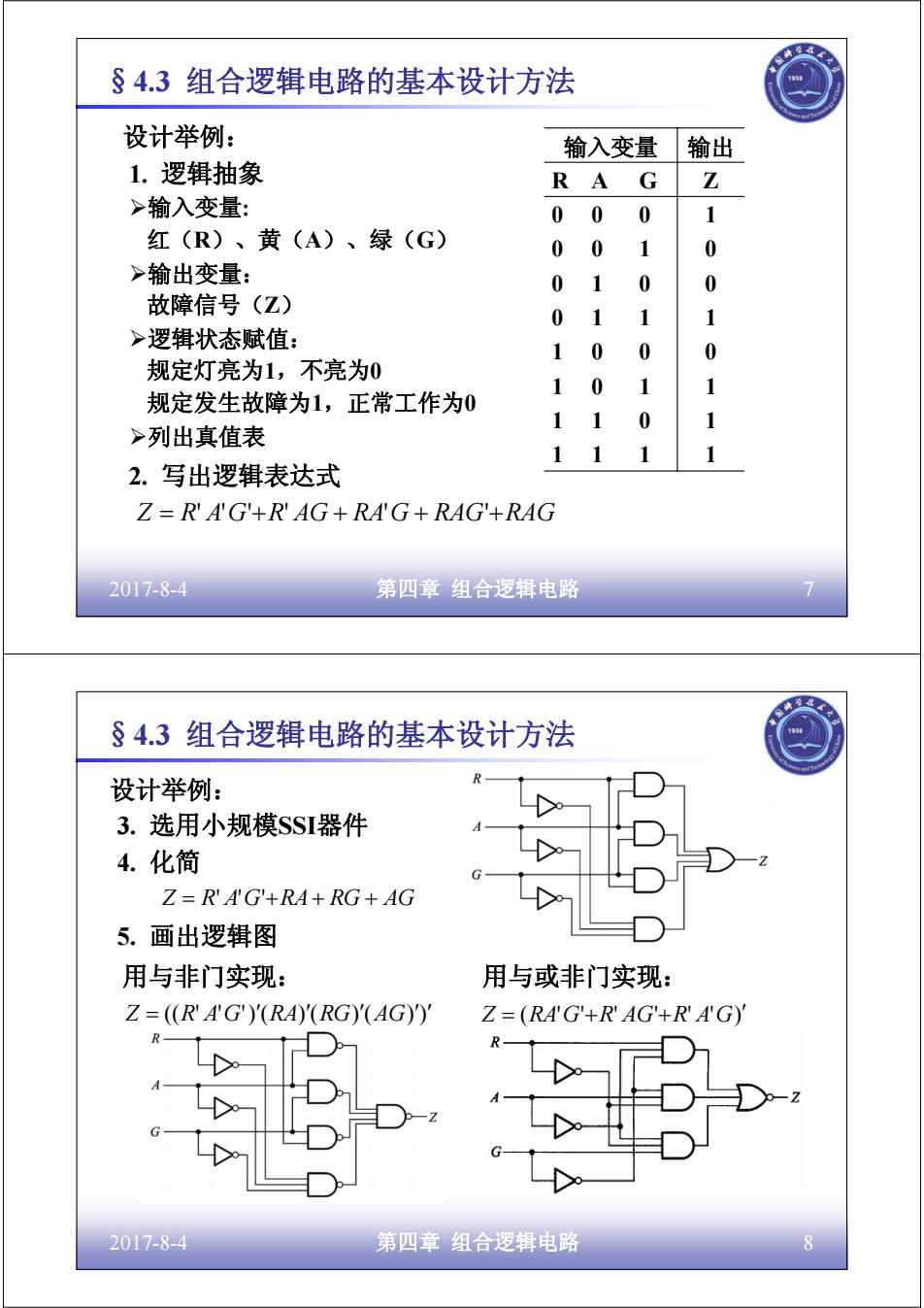

§4.3组合逻辑电路的基本设计方法 设计举例: 输入变量 输出 1.逻辑抽象 R A G >输入变量: 0 0 0 1 红(R)、黄(A)、绿(G) 0 0 1 0 >输出变量: 01 0 0 故障信号(Z) 0 1 1 1 >逻辑状态赋值: 1 0 0 0 规定灯亮为1,不亮为0 1 0 1 规定发生故障为1,正常工作为0 1 11 0 1 >列出真值表 11 1 1 2.写出逻辑表达式 Z=RAG+RAG+RAG+RAG+RAG 2017-8-4 第四章组合逻辑电路 §4.3组合逻辑电路的基本设计方法 设计举例: 3.选用小规模SSI器件 4.化简 Z=RAG+RA+RG+AG 5.画出逻辑图 用与非门实现: 用与或非门实现: Z-(RAG(RA)(RG(AG)) Z=(RAG+RAG+RAG) 2017-8-4 第四章组合逻辑电路 8

2017-8-4 第四章 组合逻辑电路 7 1 1 1 1 1 1 0 1 1 0 1 1 1 0 0 0 0 1 1 1 0 1 0 0 0 0 1 0 0 0 0 1 R A G Z 输入变量 输出 Z = R' A'G'+R' AG + RA'G + RAG'+RAG 设计举例: 1. 逻辑抽象 ¾输入变量: 红(R)、黄(A)、绿(G) ¾输出变量: 故障信号(Z) ¾逻辑状态赋值: 规定灯亮为1,不亮为0 规定发生故障为1,正常工作为0 ¾列出真值表 2. 写出逻辑表达式 §4.3 组合逻辑电路的基本设计方法 2017-8-4 第四章 组合逻辑电路 8 3. 选用小规模SSI器件 4. 化简 5. 画出逻辑图 Z = R' A'G'+RA+ RG + AG 设计举例: Z = ((R' A'G')′(RA)′(RG)′(AG)′)′ Z = (RA'G'+R' AG'+R' A'G)′ 用与非门实现: 用与或非门实现: §4.3 组合逻辑电路的基本设计方法

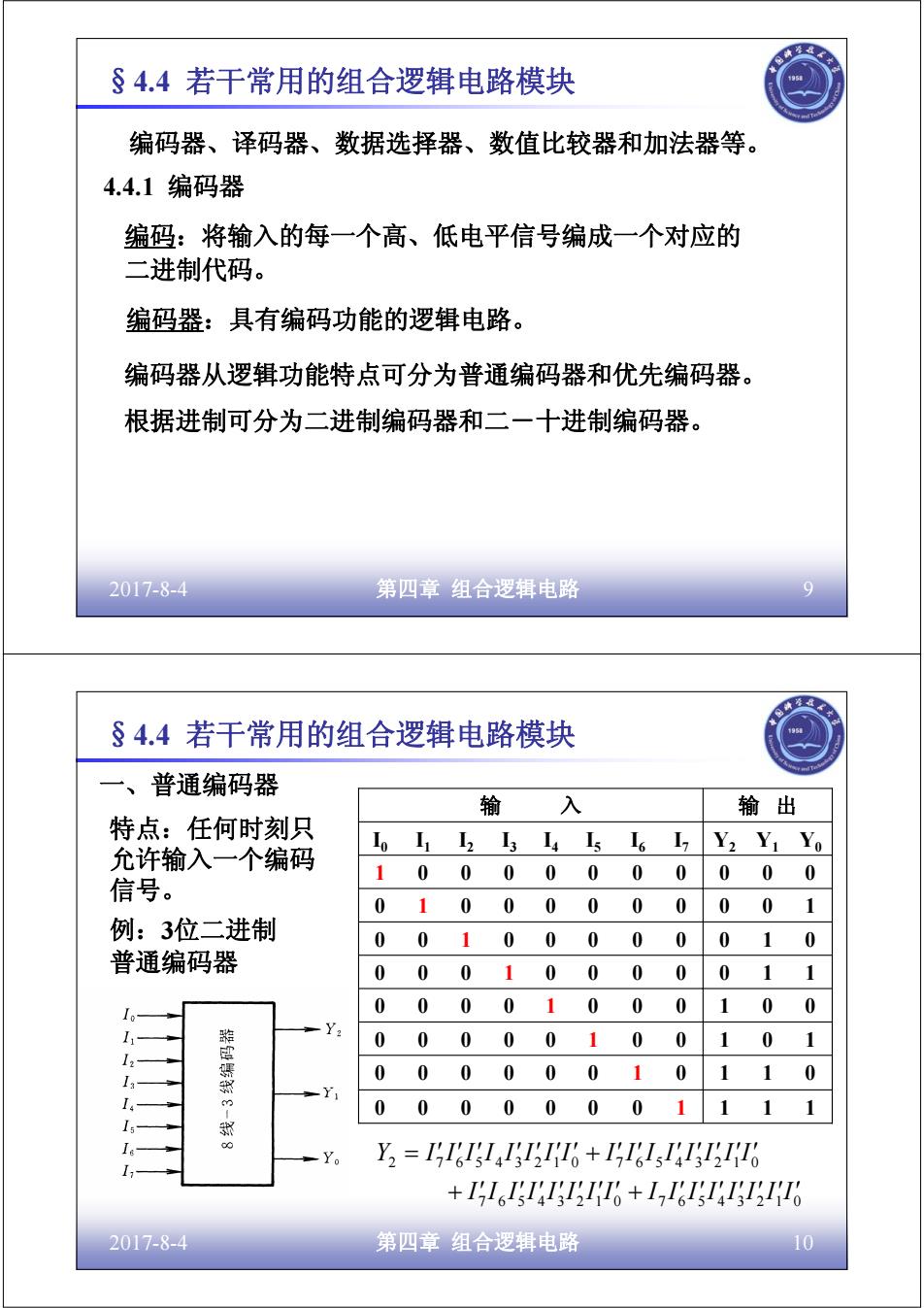

§4.4若干常用的组合逻辑电路模块 编码器、译码器、数据选择器、数值比较器和加法器等。 4.4.1编码器 编码:将输入的每一个高、低电平信号编成一个对应的 二进制代码。 编码器:具有编码功能的逻辑电路。 编码器从逻辑功能特点可分为普通编码器和优先编码器。 根据进制可分为二进制编码器和二一十进制编码器。 2017-8-4 第四章组合逻辑电路 §4.4若干常用的组合逻辑电路模块 一、普通编码器 输 入 输出 特点:任何时刻只 I12 Is I Is II Y2 YI Yo 允许输入一个编码 1 0 00000 0 00 0 信号。 0 1 0 0 0 0 0 0 0 0 1 例:3位二进制 0 01 0 00 0 01 0 普通编码器 0 0 0 1 0 0 0 0 S 1 1 0 0 0 0 1 0 0 0 10 0 0 0 0 0 0 0 0 0 1 0 00000 10 11 0 -Y 0 0 0 0 0 0 0 1 11 1 Is 00 4° Y2=17161514131211o+1161s141312110 +1I5I131HIo+I-IIs1a1312I1o 2017-8-4 第四章组合逻辑电路 10

2017-8-4 第四章 组合逻辑电路 9 §4.4 若干常用的组合逻辑电路模块 编码器、译码器、数据选择器、数值比较器和加法器等。 4.4.1 编码器 编码:将输入的每一个高、低电平信号编成一个对应的 二进制代码。 编码器:具有编码功能的逻辑电路。 编码器从逻辑功能特点可分为普通编码器和优先编码器。 根据进制可分为二进制编码器和二-十进制编码器。 2017-8-4 第四章 组合逻辑电路 10 一、普通编码器 0 0 0 0 0 0 0 1 1 1 1 0 0 0 0 0 0 1 0 1 1 0 0 0 0 0 0 1 0 0 1 0 1 0 0 0 0 1 0 0 0 1 0 0 0 0 0 1 0 0 0 0 0 1 1 0 0 1 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 0 0 1 1 0 0 0 0 0 0 0 0 0 0 Y2 Y1 Y0 I7 I6 I5 I4 I3 I2 I1 I0 输 入 输 出 7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0 2 7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0 I I I I I I I I I I I I I I I I Y I I I I I I I I I I I I I I I I + ′ ′ ′ ′ ′ ′ ′ + ′ ′ ′ ′ ′ ′ ′ = ′ ′ ′ ′ ′ ′ ′ + ′ ′ ′ ′ ′ ′ ′ 特点:任何时刻只 允许输入一个编码 信号。 例:3位二进制 普通编码器 §4.4 若干常用的组合逻辑电路模块