3.被测对象与测试方法 数据域测试按被测对象可分为: ()组合电路测试,通常有敏化通路法、D算法、布尔差分法等。 (2)时序电路测试,通常采用迭接阵列、测试序列(同步、引导 和区分序列)等方法。 (3)数字系统测试,如大规模集成电路,常用随机测试(用伪随 机序列信号作激励)技术、穷举测试技术等

3.被测对象与测试方法 数据域测试按被测对象可分为: (1) 组合电路测试,通常有敏化通路法、D算法、布尔差分法等。 (2) 时序电路测试,通常采用迭接阵列、测试序列(同步、引导 和区分序列)等方法。 (3) 数字系统测试,如大规模集成电路,常用随机测试(用伪随 机序列信号作激励)技术、穷举测试技术等

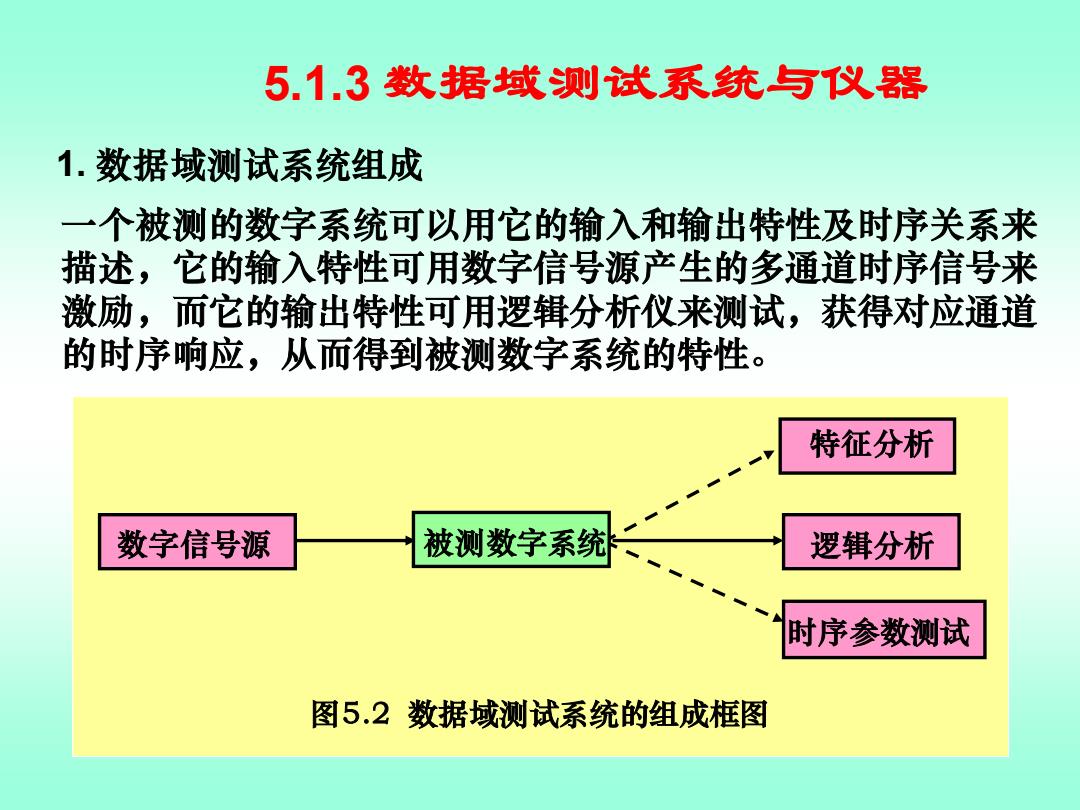

5.1.3数据域测试系统与仪器 1.数据域测试系统组成 一个被测的数字系统可以用它的输入和输出特性及时序关系来 描述,它的输入特性可用数字信号源产生的多通道时序信号来 激励,而它的输出特性可用逻辑分析仪来测试,获得对应通道 的时序响应,从而得到被测数字系统的特性。 特征分析 数字信号源 被测数字系统 逻辑分析 时序参数测试 图5.2数据域测试系统的组成框图

5.1.3 数据域测试系统与仪器 1. 数据域测试系统组成 一个被测的数字系统可以用它的输入和输出特性及时序关系来 描述,它的输入特性可用数字信号源产生的多通道时序信号来 激励,而它的输出特性可用逻辑分析仪来测试,获得对应通道 的时序响应,从而得到被测数字系统的特性。 图5.2 数据域测试系统的组成框图 数字信号源 被测数字系统 特征分析 逻辑分析 时序参数测试

2.数据域测试仪器 1)逻辑笔 逻辑笔算不上仪器,但却是数字域检测中方便实用的工具。它 像一支电工用的试电笔,能方便地探测数字电路中各点的逻辑 状态,例如,笔上红色指示灯亮为高电平,绿灯亮为低电平, 红灯绿灯轮流闪烁表示该点是时钟信号。 2)数字信号源 数字信号源又称为数字信号发生器,是数据域测试中的一种重 要仪器,它可产生图形宽度可编程的并行和串行数据图形,也 可产生输出电平和数据速率可编程的任意波形,以及一个可由 选通信号和时种信号来控制的预先规定的数据流。 数字信号源是为数字系统的功能测试和参数测试提供输入激励 信号。功能测试是测出被测器件在规定电平和正确定时激励下 的输出,就可以知道被测系统的功能是否正常;参数测试可用 来测试诸如电平值、脉冲的边缘特性等参数是否符合设计规范

2.数据域测试仪器 1)逻辑笔 逻辑笔算不上仪器,但却是数字域检测中方便实用的工具。它 像一支电工用的试电笔,能方便地探测数字电路中各点的逻辑 状态,例如,笔上红色指示灯亮为高电平,绿灯亮为低电平, 红灯绿灯轮流闪烁表示该点是时钟信号。 2)数字信号源 数字信号源又称为数字信号发生器,是数据域测试中的一种重 要仪器,它可产生图形宽度可编程的并行和串行数据图形,也 可产生输出电平和数据速率可编程的任意波形,以及一个可由 选通信号和时种信号来控制的预先规定的数据流。 数字信号源是为数字系统的功能测试和参数测试提供输入激励 信号。功能测试是测出 被测器件在规定电平和正确定时激励下 的输出,就可以知道被测系统的功能是否正常;参 数测试可用 来测试诸如电平值、脉冲的边缘特性等参数是否符合设计规范

(1)数字信号源的组成 分配器 内部时钟和 起/停产生 分离电路 外部时钟 起/停 分频器 多路 格式 输出 通道0 存储器 器 化器 放大器 序列 寄存 地址计数器 多路 格式 输出 通道K 存储器 器 化器 放大器

(1)数字信号源的组成

(2)数据的产生 上图中的序列存储器在初始化期间写入了每个通道的数据,数 据存储器的地址由地址计数器提供。在测试过程中,在每一个 作用时钟沿上,计数器将地址加1。数据存储器输出的数据与 地址是一一对应的,这是产生线性数据流的一种简单方法,这 种方法提供的最大数据率每秒大于1O0 MbitS。 一个8:的多路器可将运行频率为F/8的8个并行输入位转换成 频率为F的串行数据流。对于低速的数字信号源,多路器可以 不要,从数据的每位数输出可直接产生一个串行数据流,该数 据流加到格式化器的输入端,通过格式化器将数据流与时钟同 步。在简单情况下,格式化器就是一个D触发器。数据的逻辑 电平加在D输入端,在时钟信号沿的作用下输出。 格式化器的输出直接驱动输出放大器,放大器的输出电平是可 编程的。在某些数字信号源中,通过在每个数据模块上提供外 部时钟和启动停止输入,以便产生不同的异步数据流

(2)数据的产生 上图中的序列存储器在初始化期间写入了每个通道的数据,数 据存储器的地址由地址计数器提供。在测试过程中,在每一个 作用时钟沿上,计数器将地址加1。数据存储器输出的数据与 地址是一一对应的,这是产生线性数据流的一种简单方法,这 种方法提供的最大数据率每秒大于100MbitS。 一个8:l的多路器可将运行频率为F/8的8个并行输入位转换成 频率为F的串行数据流。对于低速的数字信号源,多路器可以 不要,从数据的每位数输出可直接产生一个串行数据流,该数 据流加到格式化器的输入端,通过格式化器将数据流与时钟同 步。在简单情况下,格式化器就是一个D触发器。数据的逻辑 电平加在D输入端,在时钟信号沿的作用下输出。 格式化器的输出直接驱动输出放大器,放大器的输出电平是可 编程的。在某些数字信号源中,通过在每个数据模块上提供外 部时钟和启动/停止输入,以便产生不同的异步数据流