扫描设计的原理 Scan Chain Scan Chain ( A Scan In Scan In ② Combination ② Combination Logic Logic Logic Scan Enable Clock D③ Scan Out Scan Out 1.Scan shift in 2.Parallel capture 3.Scan shift out (scan mode) (normal mode) (scan mode) 集成电路可测性设计 第六章:扫描设计17

扫描设计的原理 集成电路可测性设计 第六章:扫描设计 17 Scan In Scan In Scan Out Scan Chain Combination Logic Scan Out Scan Chain ① ① ③ ③ Scan Enable ② ② ② ② ② ② ② ② ② Clock Clock 1. Scan shift in (scan mode) 2. Parallel capture (normal mode) 3. Scan shift out (scan mode) Combination Logic Combination Logic

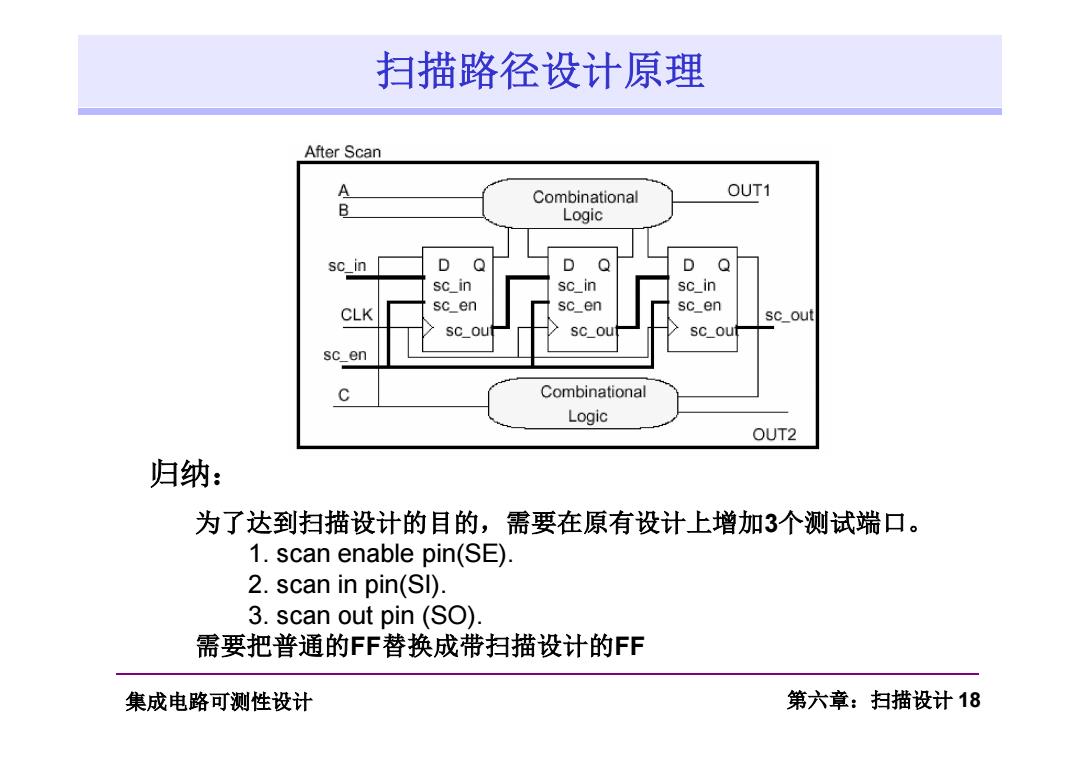

扫描路径设计原理 After Scan A Combinational OUT1 B Logic sc_in D Q D Q D Q sc_in sc_in sc_in CLK sc_en sc_en sc_en sc out sc_out sc_ou sc ou sc_en Combinational Logic OUT2 归纳: 为了达到扫描设计的目的,需要在原有设计上增加3个测试端口。 1.scan enable pin(SE) 2.scan in pin(SI). 3.scan out pin (SO) 需要把普通的FF替换成带扫描设计的FF 集成电路可测性设计 第六章:扫描设计18

扫描路径设计原理 集成电路可测性设计 第六章:扫描设计 18 归纳: 为了达到扫描设计的目的,需要在原有设计上增加3个测试端口。 1. scan enable pin(SE). 2. scan in pin(SI). 3. scan out pin (SO). 需要把普通的FF替换成带扫描设计的FF

扫描路径种类 全扫描设计(Full-Scan Design) -全部的FF都连成扫描链 -测试速度快,测试图形短 -面积代价高 部分扫描设计(Partial-Scan Design) -只有部分的FF连成扫描链 -测试速度慢,测试图形长 -面积代价低 集成电路可测性设计 第六章:扫描设计19

扫描路径种类 全扫描设计(Full-Scan Design) 全部的FF都连成扫描链 测试速度快,测试图形短 面积代价高 部分扫描设计(Partial-Scan Design) 只有部分的FF连成扫描链 测试速度慢,测试图形长 面积代价低 集成电路可测性设计 第六章:扫描设计 19

扫描路径种类 隔离的串行扫描设计一不常使用 非串行的扫描设计一不常使用 集成电路可测性设计 第六章:扫描设计20

扫描路径种类 隔离的串行扫描设计—不常使用 非串行的扫描设计—不常使用 集成电路可测性设计 第六章:扫描设计 20

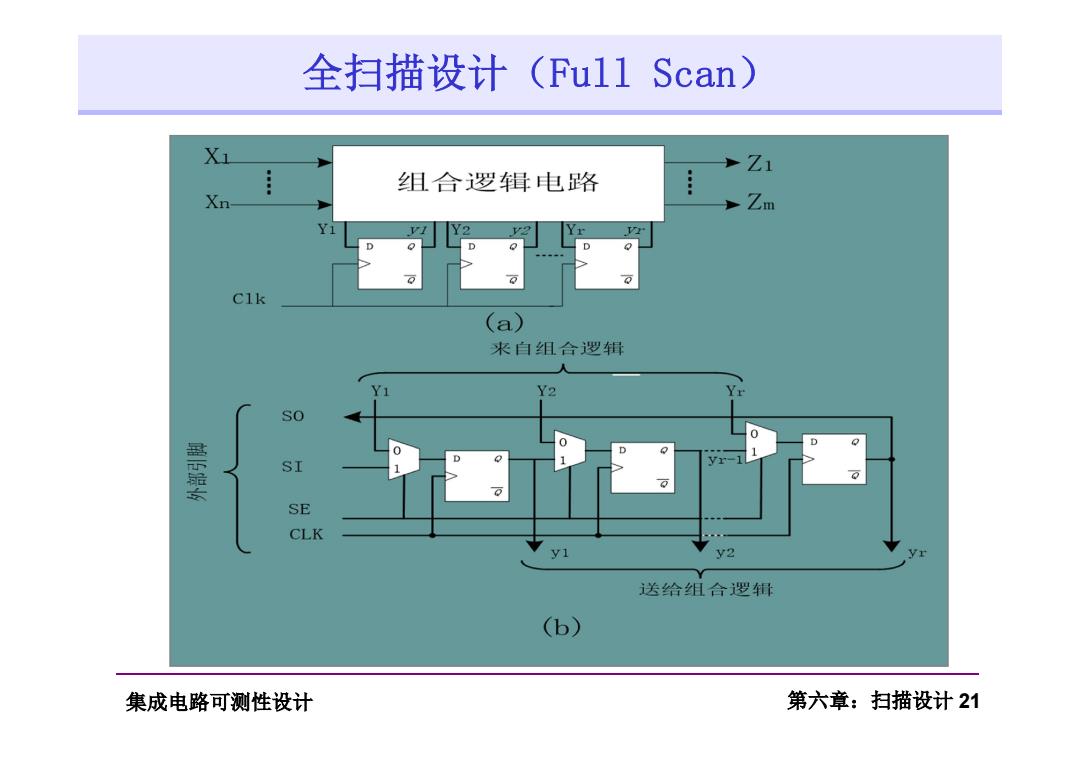

全扫描设计(Ful1Scan) Xi >ZI 组合罗辑电路 Xn Zm 4 D Clk (a) 来自组合逻辑 人 Y1 Y2 SI SE CLK y1 送给组合逻辑 (b) 集成电路可测性设计 第六章:扫描设计21

集成电路可测性设计 第六章:扫描设计 21 全扫描设计(Full Scan)