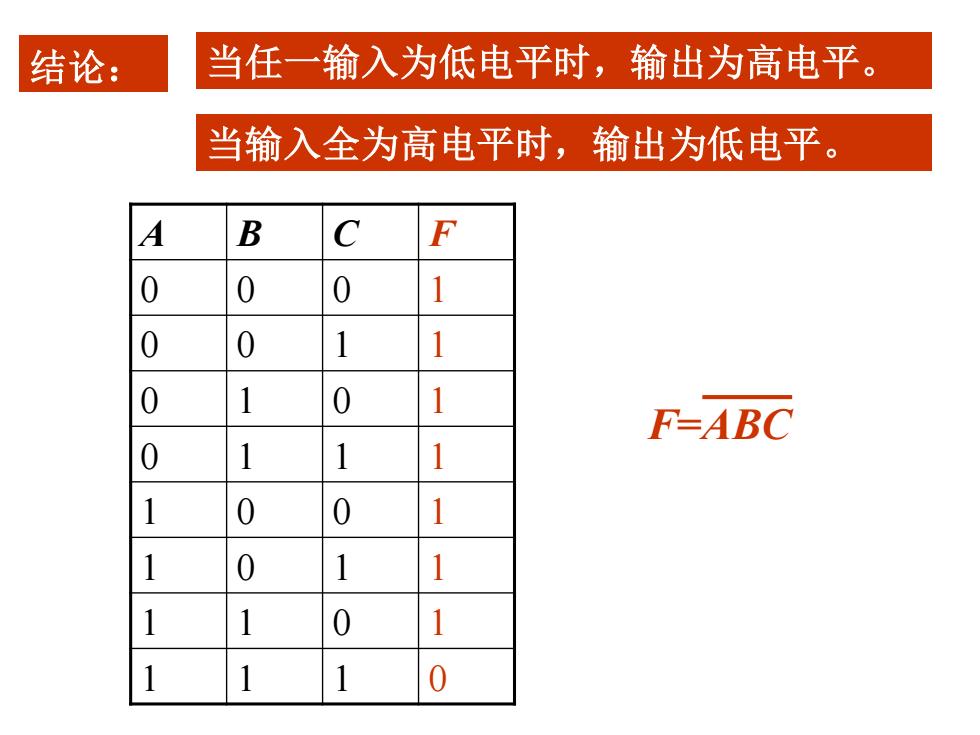

结论: 当任一输入为低电平时,输出为高电平。 当输入全为高电平时,输出为低电平。 A B 0 F-ABC 0 0 0 1 0 1 1 0

当输入全为高电平时,输出为低电平。 当任一输入为低电平时,输出为高电平。 A B C F 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 0 结论: F=ABC

2三态输出与非门电路 B E +5V EN R R B 控制端 Rs

三态 (1)高电平 (2)低电平 (3)高阻状态 2 三态输出与非门电路 A B F & E EN R3 +5V F T3 T4 T5 T2 R1 R2 R4 R5 T1 A B E D 控 制 端

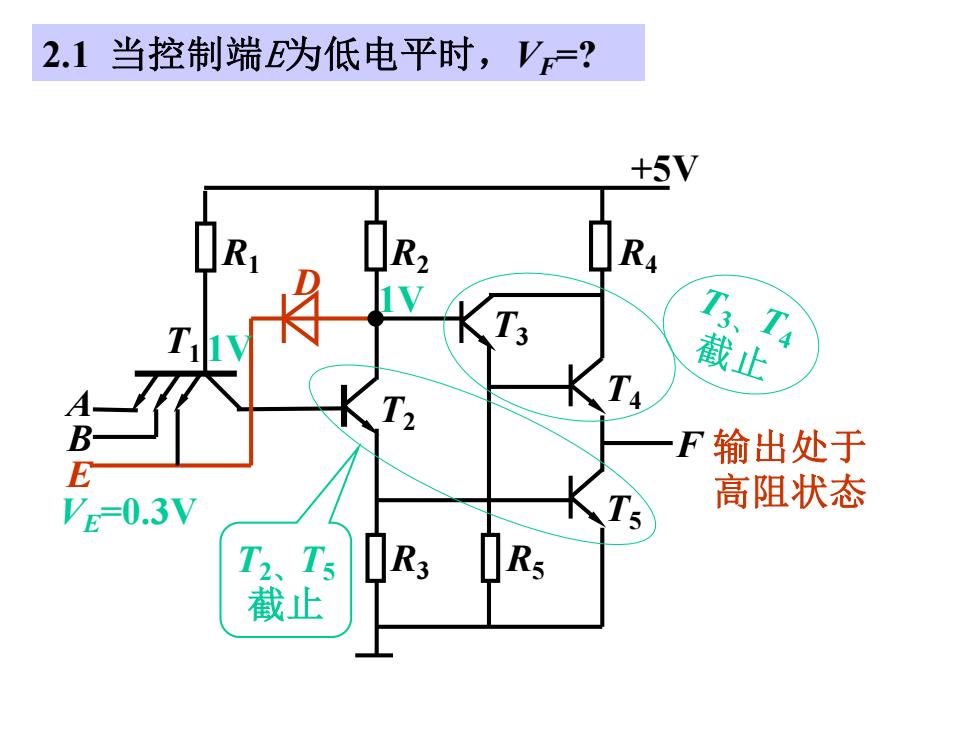

2.1当控制端为低电平时,V=? +5V R R T T3 T3、T4 截止 B -F 输出处于 E V=0.3V 高阻状态 T2、T5 截止

R3 +5V F T3 T4 T5 T2 R1 R2 R4 R5 T1 A B E D 2.1 当控制端E为低电平时,VF=? 输出处于 高阻状态 VE=0.3V 1V 1V T2、 T5 截止

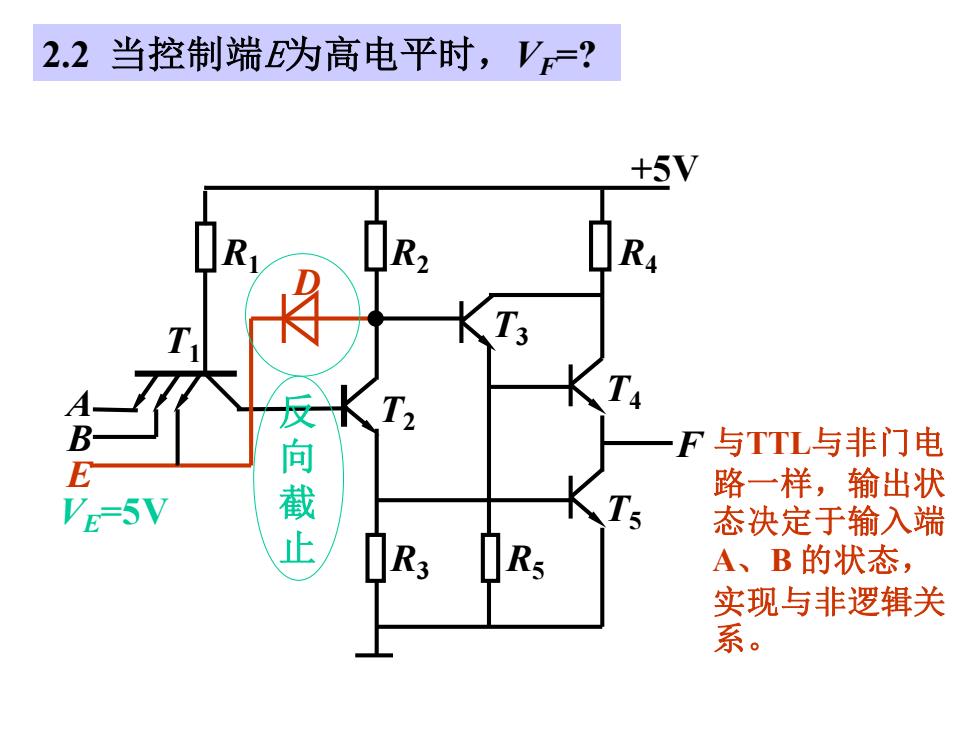

2.2当控制端为高电平时,V=? +5V R <T4 B E 反向截 F与TTL与非门电 路一样,输出状 VE=5V 态决定于输入端 A、B的状态, 实现与非逻辑关 系

2.2 当控制端E为高电平时,VF=? R3 +5V F T3 T4 T5 T2 R1 R2 R4 R5 T1 A B E D VE=5V 与TTL与非门电 路一样,输出状 态决定于输入端 A、B 的状态, 实现与非逻辑关 系。 反 向 截 止

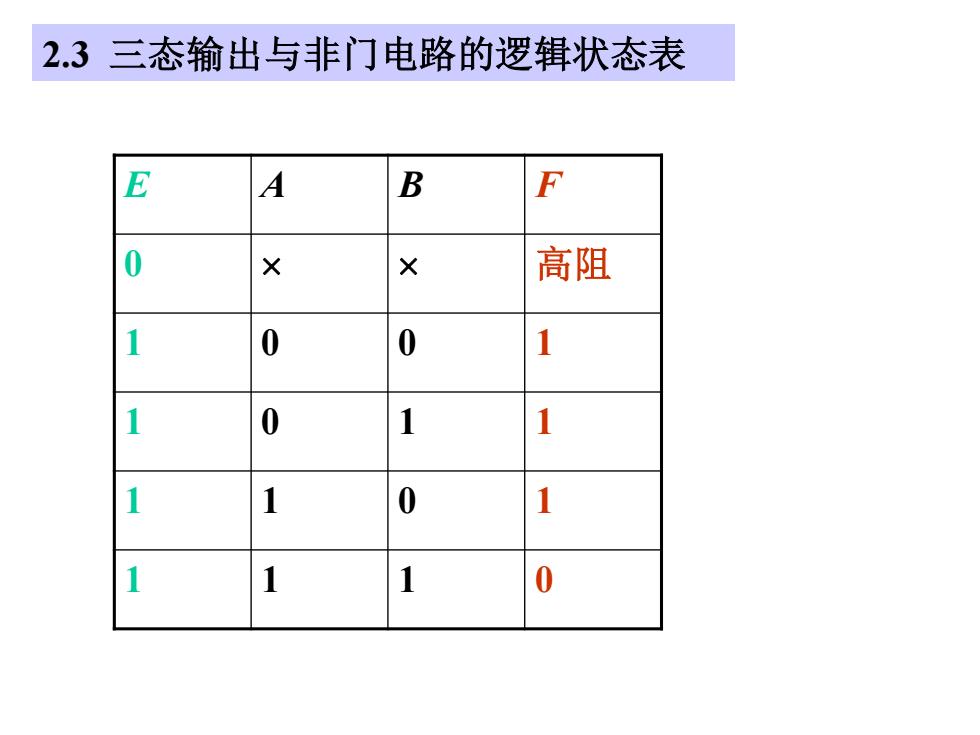

2.3三态输出与非门电路的逻辑状态表 E A B F × × 高阻 0 0 1 0 1 1 1 0 1 1 0

2.3 三态输出与非门电路的逻辑状态表 E A B F 0 高阻 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 0