心读锁存器和读引脚指令■当把P0~P3口作为输入引脚使用时,以I/O口作为源操作数的数据传送指令、算术/逻辑运算指令及位测试转移指令等均属读引脚指令。所有的“读一改一写”指令均读/O口锁存器

❖ 读锁存器和读引脚指令 ▪ 当把P0~P3口作为输入引脚使用时,以I/O口作为 源操作数的数据传送指令、算术/逻辑运算指令及 位测试转移指令等均属读引脚指令。 ▪ 所有的“读—改—写”指令均读I/O口锁存器

5.1.1P1口心结构组成:它由一个输出锁存器、两个三态输入缓冲器和输出驱动电路组成---准双向口。*功能:作为通用I/O使用

5.1.1 P1口 ❖ 结构组成:它由一个输出锁存器、两个三态输入缓冲 器和输出驱动电路组成-准双向口。 ❖ 功能:作为通用I/O使用

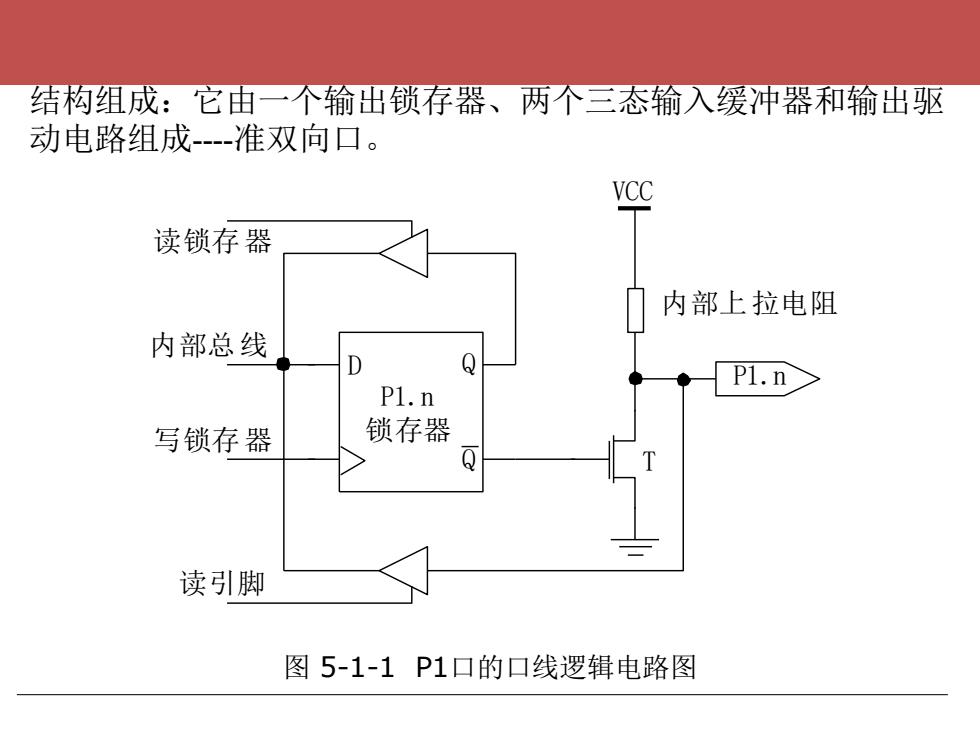

结构组成:它由一个输出锁存器、两个三态输入缓冲器和输出驱动电路组成----准双向口。VCC读锁存器内部上拉电阻内部总线QDP1.nP1.n锁存器写锁存器Q读引脚图5-1-1P1口的口线逻辑电路图

P1.n 锁存器 P1.n Q D Q 读锁存器 写锁存器 内部总线 读引脚 内部上拉电阻 T VCC 图 5-1-1 P1口的口线逻辑电路图 结构组成:它由一个输出锁存器、两个三态输入缓冲器和输出驱 动电路组成-准双向口

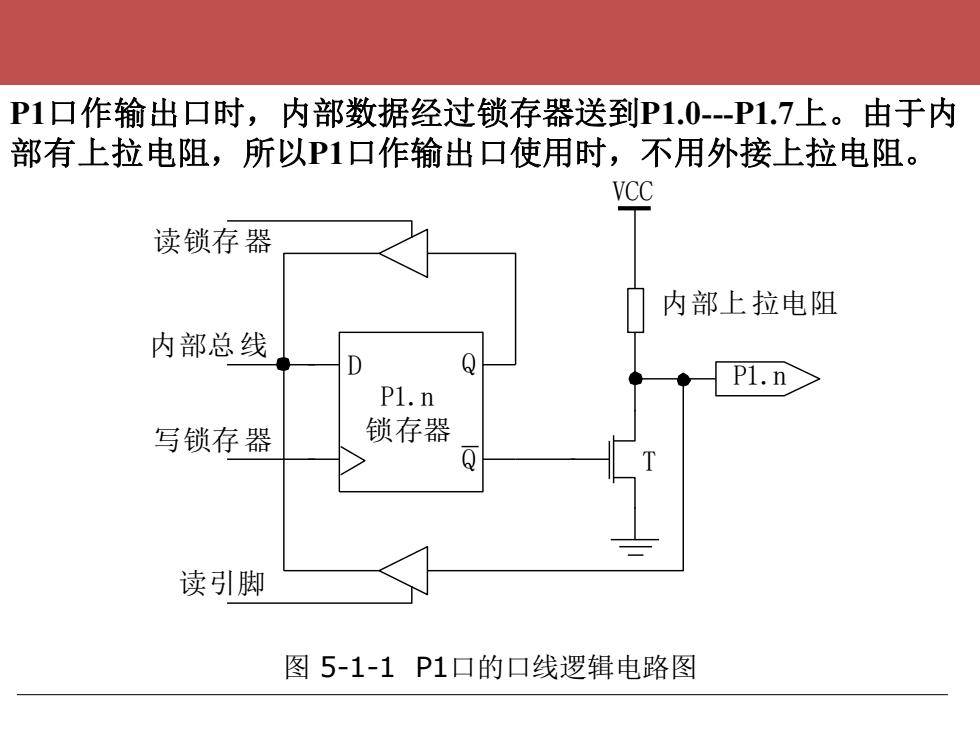

P1口作输出口时,内部数据经过锁存器送到P1.0---P1.7上。由于内部有上拉电阻,所以P1口作输出口使用时,不用外接上拉电阻。VCC读锁存器内部上拉电阻内部总线QDP1.nP1. n锁存器写锁存器Q读引脚图5-1-1P1口的口线逻辑电路图

P1.n 锁存器 P1.n Q D Q 读锁存器 写锁存器 内部总线 读引脚 内部上拉电阻 T VCC 图 5-1-1 P1口的口线逻辑电路图 P1口作输出口时,内部数据经过锁存器送到P1.0-P1.7上。由于内 部有上拉电阻,所以P1口作输出口使用时,不用外接上拉电阻

P1口作输入口时,P1.0一P1.7上的信号经过缓冲器送到内部数据总线上。在读引脚之前,要先将锁存器置1,否则总是读到0。CPU对IO口的读操作有2种:读引脚和读锁存器VCC读锁存器内部上拉电阻内部总线DQP1.nP1.n锁存器写锁存器Q读引脚图5-1-1P1口的口线逻辑电路图

P1.n 锁存器 P1.n Q D Q 读锁存器 写锁存器 内部总线 读引脚 内部上拉电阻 T VCC 图 5-1-1 P1口的口线逻辑电路图 P1口作输入口时,P1.0—P1.7上的信号经过缓冲器送到内部数据 总线上。在读引脚之前,要先将锁存器置1,否则总是读到0。 CPU对I/O口的读操作有2种:读引脚和读锁存器