第6章单片机接口技术PO口、P2口可以作为并行扩展总线口使用,可扩展64KB的程序存储器和64KB的数据存储器(RAM或I/O口)本章将系统扩展原理、扩展器件、设备接口技术结合在一起,综合介绍单片机的接口技术和程序设计方法。重点是O口扩展和设备的接口与编程。6.151系列单片机并行扩展原理6.1.1大系统的扩展总线和扩展原理一、大系统(large)对于硬件需求量大,外部存储器空间被充分利用的应用系统,其系统结构规模大,我们之为大系统。在大系统中,PO口和P2口都作为总线口使用,不能作为第一功能的I/O接口连接外部设备。DPTR、RO、R1都可以作为访问外部数据存储器的地址指针,外部变量用xdata定义。二、大系统总线时序大系统中PO口、P2口作为扩展总线口。P2口输出高8位地址A8~A15,P0口输出低8位地址A0~A7,同时作为双向数据总线D0~D7。控制总线PSEN,RD(P3.7)、WR(P3.6),以及ALE。图6-1-1给出了大系统中CPU访问外部存储器的时序波形

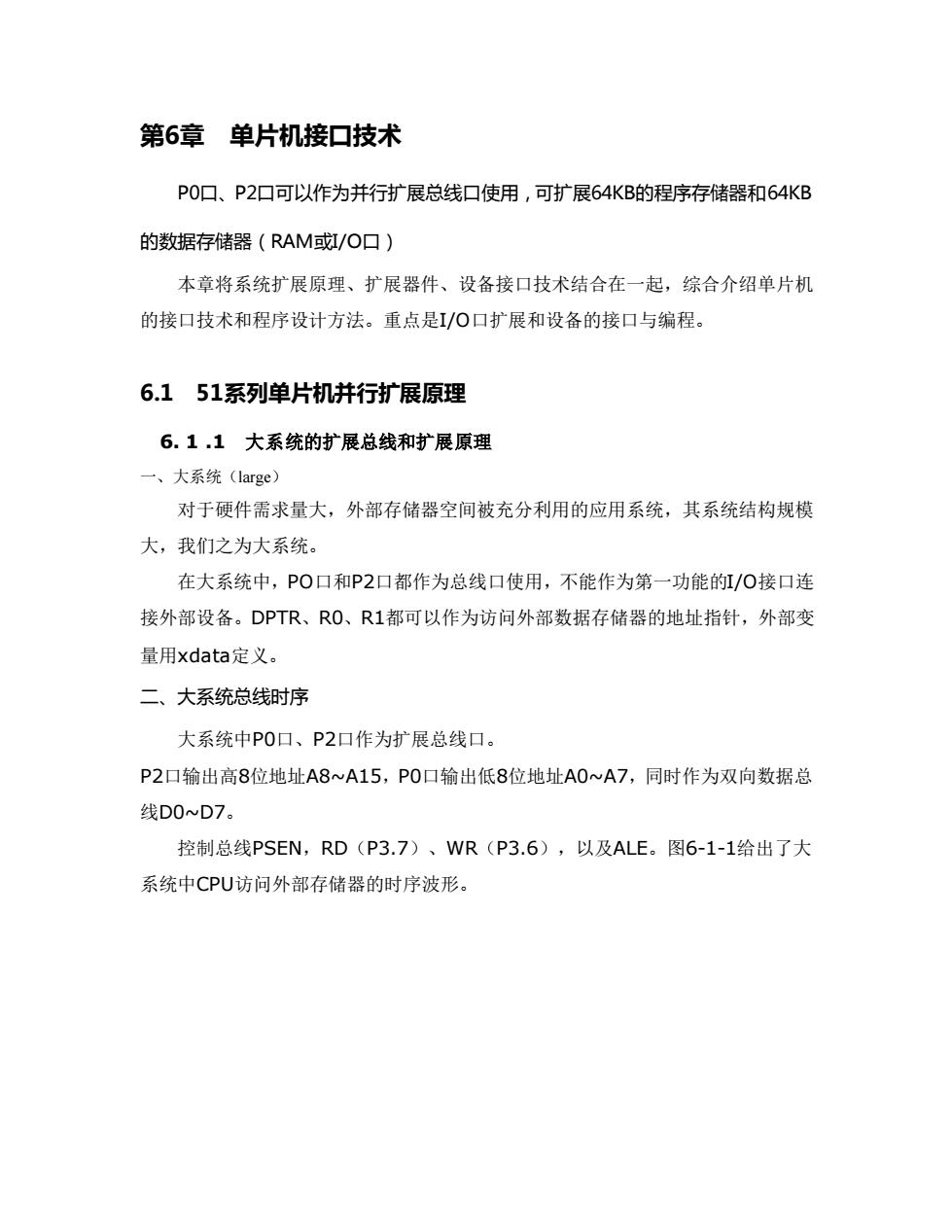

第6章 单片机接口技术 P0口、P2口可以作为并行扩展总线口使用,可扩展64KB的程序存储器和64KB 的数据存储器(RAM或I/O口) 本章将系统扩展原理、扩展器件、设备接口技术结合在一起,综合介绍单片机 的接口技术和程序设计方法。重点是I/O口扩展和设备的接口与编程。 6.1 51系列单片机并行扩展原理 6. 1 .1 大系统的扩展总线和扩展原理 一、大系统(large) 对于硬件需求量大,外部存储器空间被充分利用的应用系统,其系统结构规模 大,我们之为大系统。 在大系统中,PO口和P2口都作为总线口使用,不能作为第一功能的I/O接口连 接外部设备。DPTR、R0、R1都可以作为访问外部数据存储器的地址指针,外部变 量用xdata定义。 二、大系统总线时序 大系统中P0口、P2口作为扩展总线口。 P2口输出高8位地址A8~A15,P0口输出低8位地址A0~A7,同时作为双向数据总 线D0~D7。 控制总线PSEN,RD(P3.7)、WR(P3.6),以及ALE。图6-1-1给出了大 系统中CPU访问外部存储器的时序波形

机器摄S5SPile2TPPPllP2oscTALEPSENRD.WRP2地址A15~A8地址A15-A8指全PO图6-1-1大系统中CPU访问外部存储器的时序波形三、大系统扩展总线PO口是地址/数据复用的总线口,ALE的负跳变将地址信息AO~A7打入外部的地址锁存器。图6-1-4是用74HC573作为地址锁存器的系统扩展总线图。图6-1-5为74HC573的结构框图。常用锁存器:74LS373、74HC353/573、8282P20>A8~A15地址总线89C52A0~A7DOO7INSOUIALEG74HC573EQD7ADO~D7数据总线PO口PSEN控制总线(p3.6)WR(p3.7)RD图6-1-5图6-1-4

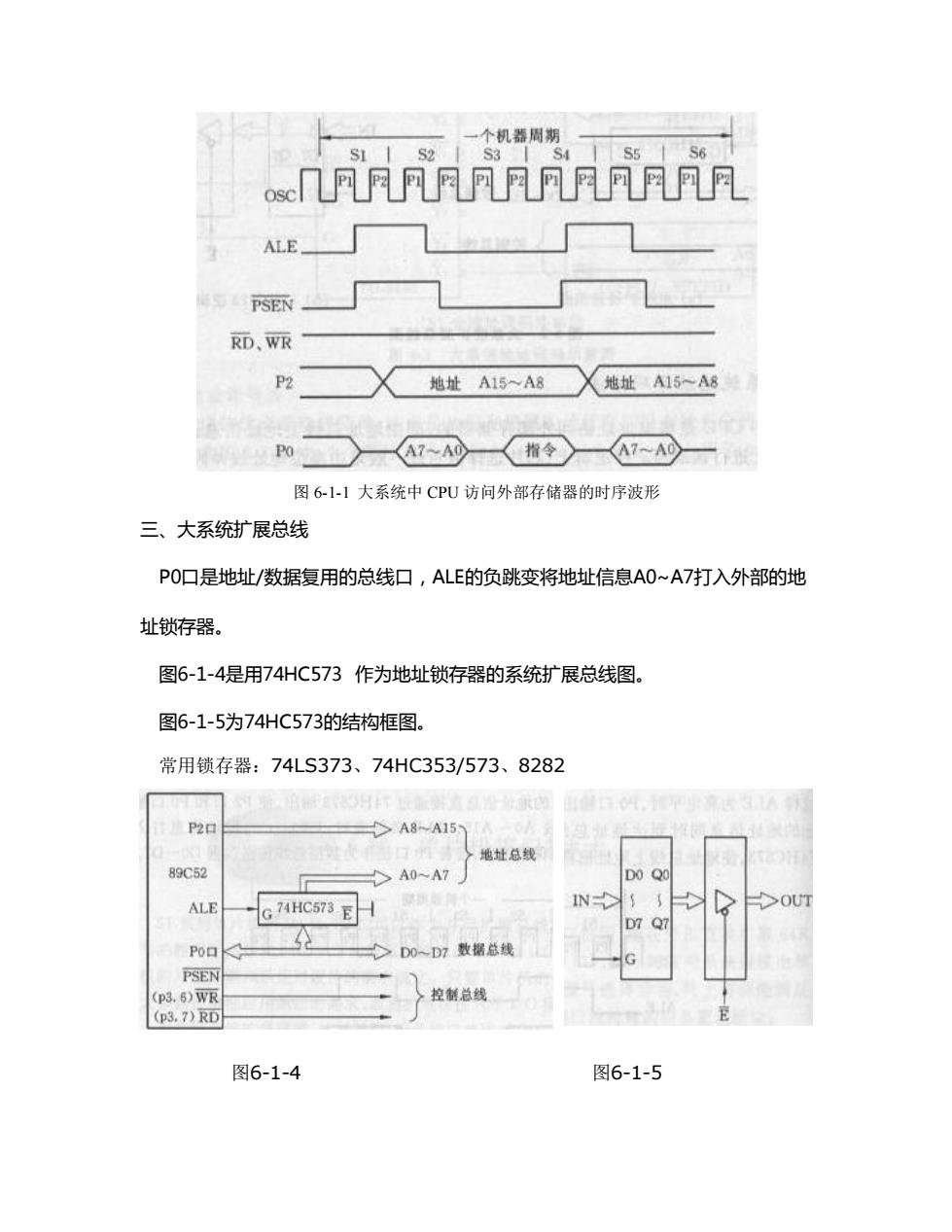

图 6-1-1 大系统中 CPU 访问外部存储器的时序波形 三、大系统扩展总线 P0口是地址/数据复用的总线口,ALE的负跳变将地址信息A0~A7打入外部的地 址锁存器。 图6-1-4是用74HC573 作为地址锁存器的系统扩展总线图。 图6-1-5为74HC573的结构框图。 常用锁存器:74LS373、74HC353/573、8282 图6-1-4 图6-1-5

四、大系统地址译码方法单片机中CPU是根据地址访问外部存储器的,即由地址总线上地址信息选中某一芯片的某个单元进行读或写。在逻辑上,芯片选择信号线一般是由高位地址线译码产生的,而芯片中的单元选择是由低位地址确定。地址译码方法有线选法和全地址译码法两种。1、线选法所谓线选法就是用某一位地址线作为片选线,一般芯片的选片信号为低电平有效(如:CS、CE),只要这一位地址线为低电平,就选中该芯片进行读写。若外部扩展的芯片中最多的单元地址线为AO~Ai,则可以作为选片的地址线为A15~Ai+1。例如:i=12,则只有A15、A14、A13可以作为选片线。图6-1-6中A15作为CS0、A14作为CS1、A13作为CS2,分别接到0、1#、2#芯片的选片端。不管芯片中有多少个单元,所占的地址空间一样大,可以用如下方法确定芯片中单元地址:芯片中未用到的地址线为1,用到的地址线由所访问的芯片和单元确定

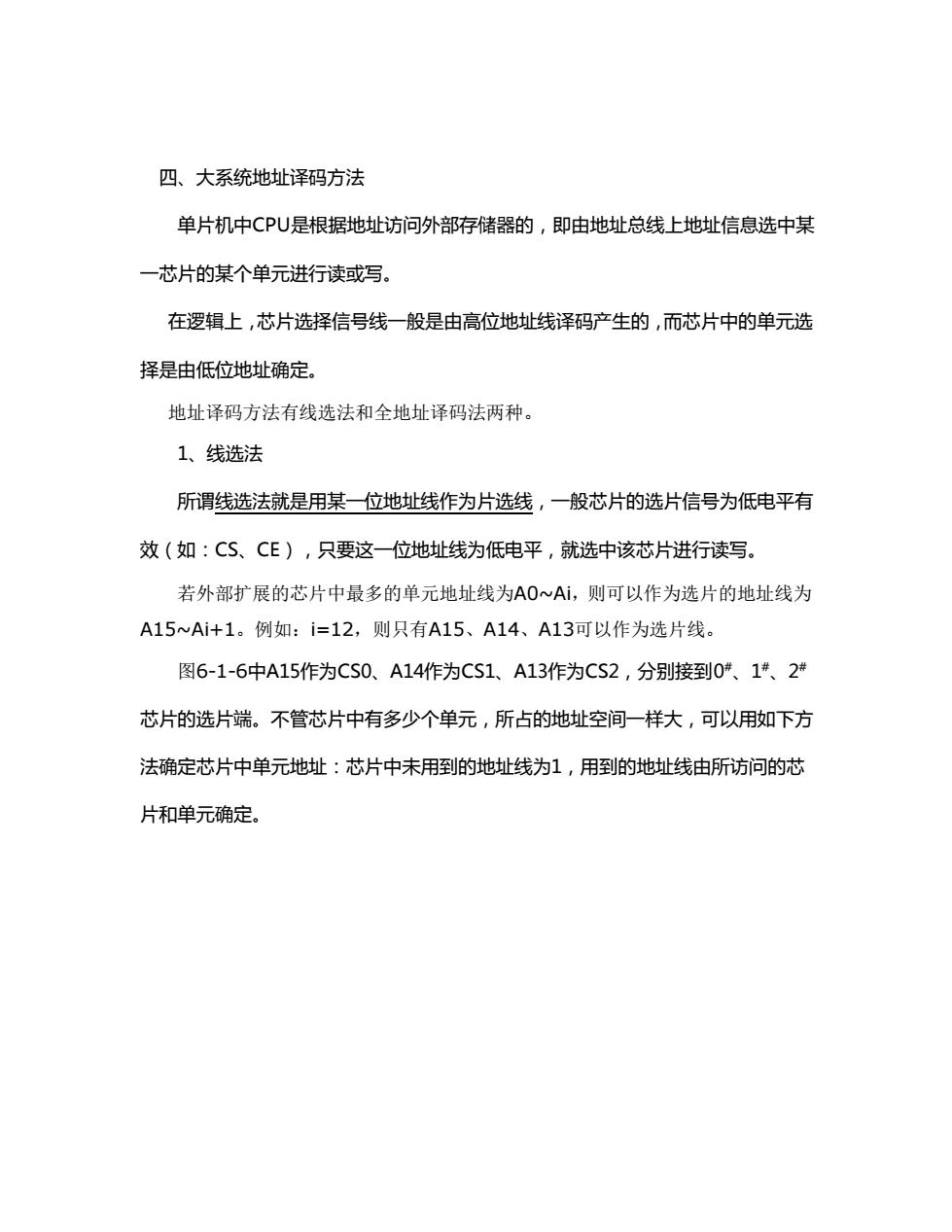

四、大系统地址译码方法 单片机中CPU是根据地址访问外部存储器的,即由地址总线上地址信息选中某 一芯片的某个单元进行读或写。 在逻辑上,芯片选择信号线一般是由高位地址线译码产生的,而芯片中的单元选 择是由低位地址确定。 地址译码方法有线选法和全地址译码法两种。 1、线选法 所谓线选法就是用某一位地址线作为片选线,一般芯片的选片信号为低电平有 效(如:CS、CE),只要这一位地址线为低电平,就选中该芯片进行读写。 若外部扩展的芯片中最多的单元地址线为A0~Ai,则可以作为选片的地址线为 A15~Ai+1。例如:i=12,则只有A15、A14、A13可以作为选片线。 图6-1-6中A15作为CS0、A14作为CS1、A13作为CS2,分别接到0 #、1 #、2 # 芯片的选片端。不管芯片中有多少个单元,所占的地址空间一样大,可以用如下方 法确定芯片中单元地址:芯片中未用到的地址线为1,用到的地址线由所访问的芯 片和单元确定

ACA00#芯片CSA15AlA1CSO)A2(6000H~7FFFH)A2A9AI1芯片aCSA14(CSD)CA000H~BEFFHDA12A12ACAo2芯片CSA13AA(CS2)(COOOH~DFFFH)1图 6-1-62.地址译码法线选法的优点是接线简单,缺点是外部存储器的地址空间没有被充分利用,可以接的芯片少。如在图6-1-6中,3个芯片总共有(8192+4+8)个单元,却占用了64K空间。可以用对高位地址译码方法克服这个缺点。常用地址译码器为:2--4译码器74HC139对A15、A14译码产生4个选片信号线,接4个芯片,每个芯片占16K字节空间;3--8译码器74HC138对A15、A14、A13译码产生8个选片信号,可接8个芯片,每个芯片占8K字节空间(见图6-1-8)。实际使用中常常将线选法和译码法结合起来使用

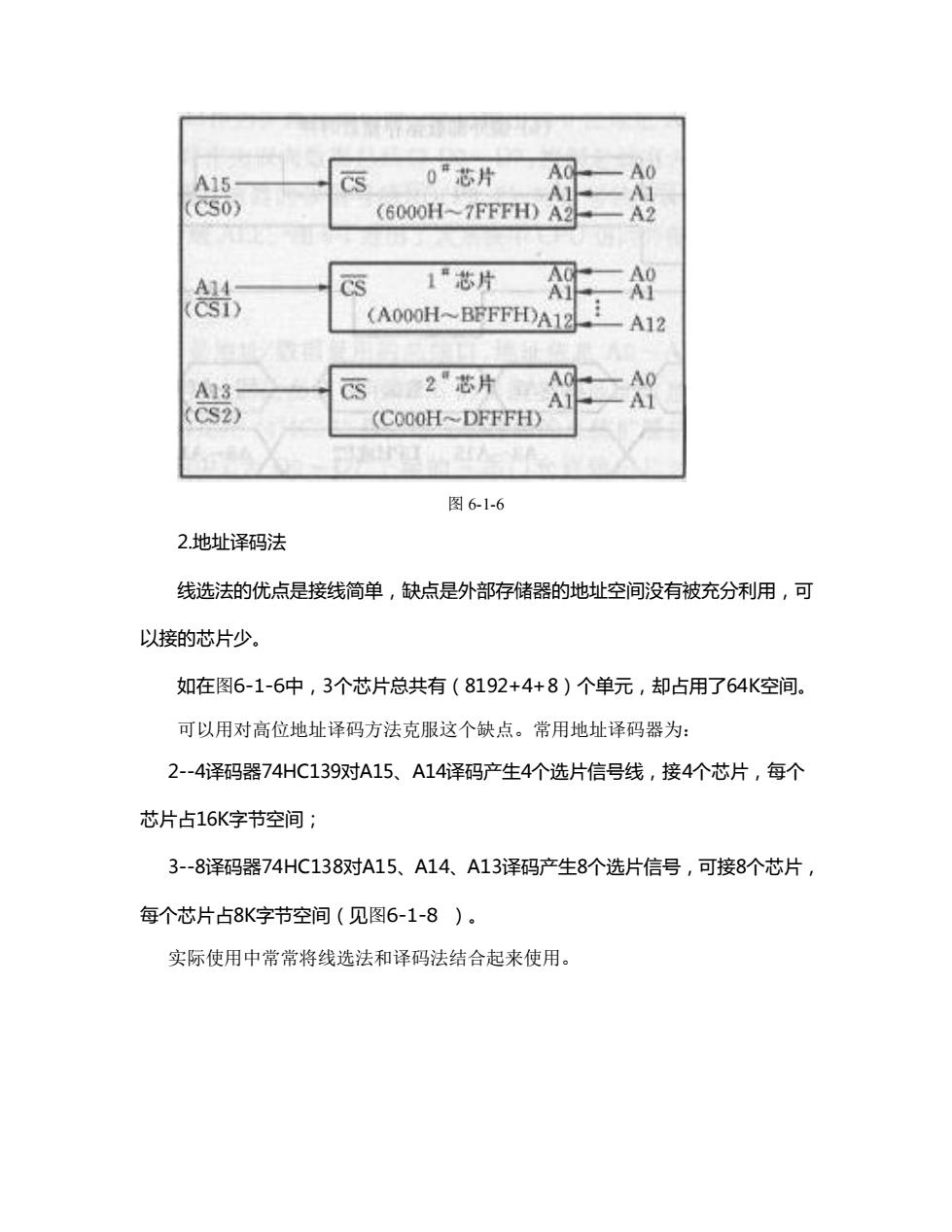

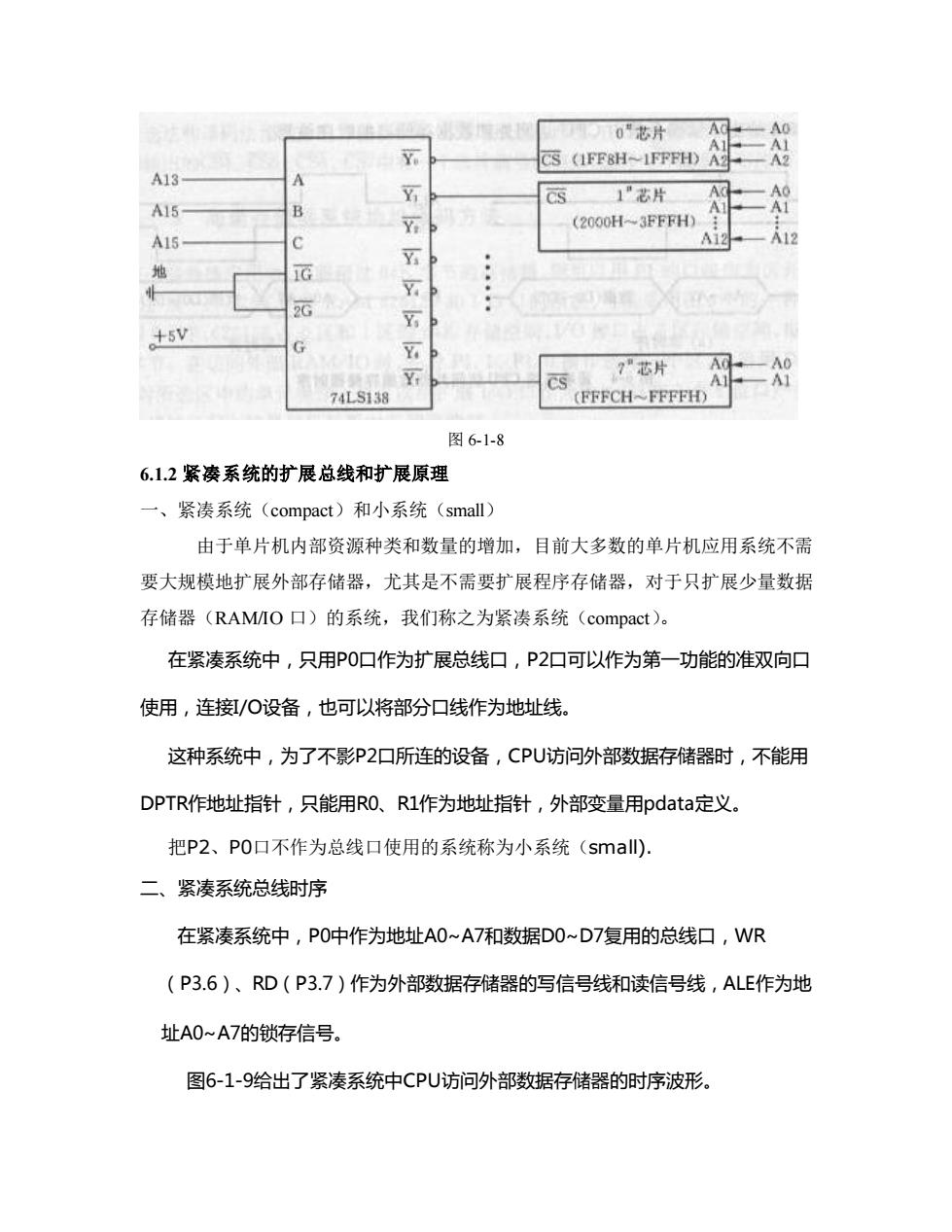

图 6-1-6 2.地址译码法 线选法的优点是接线简单,缺点是外部存储器的地址空间没有被充分利用,可 以接的芯片少。 如在图6-1-6中,3个芯片总共有(8192+4+8)个单元,却占用了64K空间。 可以用对高位地址译码方法克服这个缺点。常用地址译码器为: 2-4译码器74HC139对A15、A14译码产生4个选片信号线,接4个芯片,每个 芯片占16K字节空间; 3-8译码器74HC138对A15、A14、A13译码产生8个选片信号,可接8个芯片, 每个芯片占8K字节空间(见图6-1-8 )。 实际使用中常常将线选法和译码法结合起来使用

AoAc0芯片MA2Y.CS(1FF8H-IFPFH)AA13AYAOACCS1芯片A1A15B(2000H~3FFFH)主Y.A12A12cA15Y.地1GY.2GY.+5VGY.AC--AO2芯片YIA1AI(FFFCH~FFFFH)74LS138图6-1-86.1.2紧凑系统的扩展总线和扩展原理、紧凑系统(compact)和小系统(small)由于单片机内部资源种类和数量的增加,目前大多数的单片机应用系统不需要大规模地扩展外部存储器,尤其是不需要扩展程序存储器,对于只扩展少量数据存储器(RAM/IO口)的系统,我们称之为紧凑系统(compact)。在紧凑系统中,只用PO口作为扩展总线口,P2口可以作为第一功能的准双向口使用,连接/O设备,也可以将部分口线作为地址线。这种系统中,为了不影P2口所连的设备,CPU访问外部数据存储器时,不能用DPTR作地址指针,只能用RO、R1作为地址指针,外部变量用pdata定义,把P2、PO口不作为总线口使用的系统称为小系统(small).二、紧凑系统总线时序在紧凑系统中,PO中作为地址A0~A7和数据D0~D7复用的总线口,WR(P3.6)、RD(P3.7)作为外部数据存储器的写信号线和读信号线,ALE作为地址A0~A7的锁存信号。图6-1-9给出了紧凑系统中CPU访问外部数据存储器的时序波形

图 6-1-8 6.1.2 紧凑系统的扩展总线和扩展原理 一、紧凑系统(compact)和小系统(small) 由于单片机内部资源种类和数量的增加,目前大多数的单片机应用系统不需 要大规模地扩展外部存储器,尤其是不需要扩展程序存储器,对于只扩展少量数据 存储器(RAM/IO 口)的系统,我们称之为紧凑系统(compact)。 在紧凑系统中,只用P0口作为扩展总线口,P2口可以作为第一功能的准双向口 使用,连接I/O设备,也可以将部分口线作为地址线。 这种系统中,为了不影P2口所连的设备,CPU访问外部数据存储器时,不能用 DPTR作地址指针,只能用R0、R1作为地址指针,外部变量用pdata定义。 把P2、P0口不作为总线口使用的系统称为小系统(small). 二、紧凑系统总线时序 在紧凑系统中,P0中作为地址A0~A7和数据D0~D7复用的总线口,WR (P3.6)、RD(P3.7)作为外部数据存储器的写信号线和读信号线,ALE作为地 址A0~A7的锁存信号。 图6-1-9给出了紧凑系统中CPU访问外部数据存储器的时序波形