4.1组合逻辑电路的分析方法与设计方法 例3.4.3:设计一个将余3码变换成8421码的组合逻辑电路。 解:(1)根据题目要求,列出真值表: 真值表 输入(余3码) 输出(8421码) A3 A A0 L3 L2 L Lo 0 0 11 0 0 0 0 1 0 0 0 0 1 0 10 1 0 0 1 0 0 1 10 0 0 1 1 0 11 1 0 1 0 0 1 0 0 0 0 1 0 1 1 001 0 1 1 0 1 0 1 S 1 1 1 1 1 0 0 0 1 0 0 0 0 机电学院电气工程系 上一页 下-页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 真 值 表 输入(余3码) 输出(8421码) 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 A3 A2 A1 A0 L3 L2 L1 L0 例3.4.3:设计一个将余3码变换成8421码的组合逻辑电路。 解:(1)根据题目要求,列出真值表: 4.1 组合逻辑电路的分析方法与设计方法

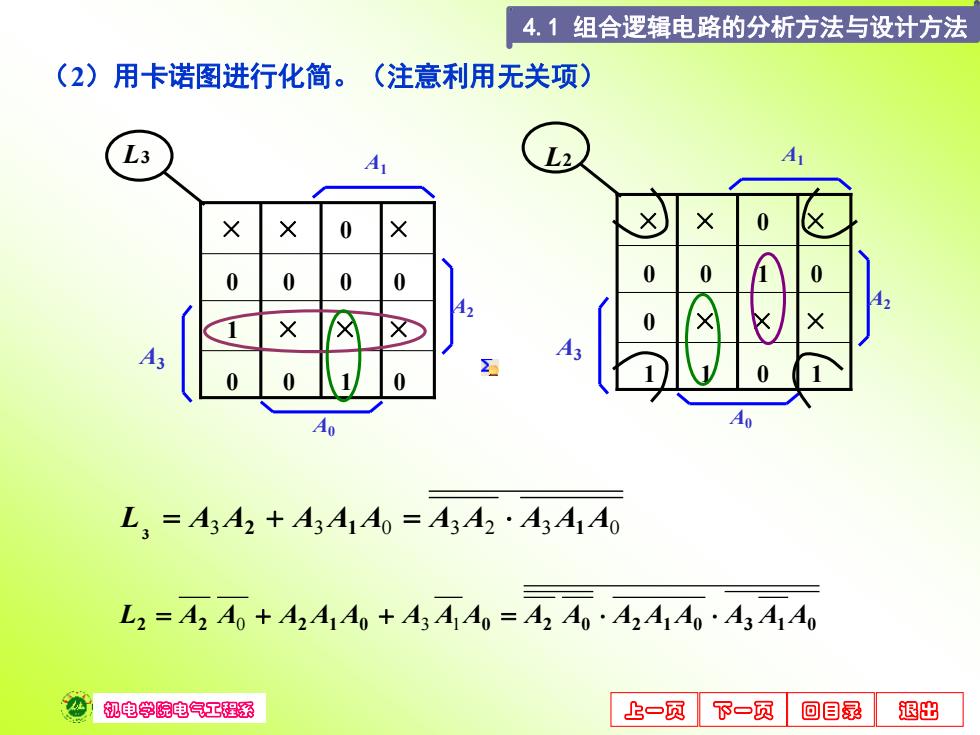

4.1组合逻辑电路的分析方法与设计方法 (2)用卡诺图进行化简。(注意利用无关项) L3 0 0 L,=A342 +A34A0=A342434A0 L2=A2 Ao +A2A Ao+A3A Ao=42 AoA2A AoA3AAo 少机电学院电气工程系 上一页下一页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 L3 A1 A3 A2 A0 × 0 1 0 0 × 0 0 0 0 × × 1 0 × × L2 A1 A3 A2 A0 × 0 0 1 0 × 0 0 1 1 × × 0 1 × × L2 A2 A A2 A1 A0 A A A0 A2 A0 A2 A1 A0 A3 A1 A0 = + + = 0 3 1 L 3 A3 A2 A3 A1 A0 A3 A2 A3 A1 A0 = + = (2)用卡诺图进行化简。(注意利用无关项) 4.1 组合逻辑电路的分析方法与设计方法

4.1组合逻辑电路的分析方法与设计方法 L Lo 0 0 0 A0 L1=A1A0+A0A1=A1田A0 L0=A0 机电学院电气工程系 上一页下-页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 L1 A1 A3 A2 A0 × 1 0 0 1 × 0 0 0 1 × × 0 1 × × L0 A1 A3 A2 A0 × 0 1 0 1 × 0 1 1 0 × × 0 1 × × L0 = A0 L1 = A1 A0 + A0 A1 = A1 A0 4.1 组合逻辑电路的分析方法与设计方法

4.1组合逻辑电路的分析方法与设计方法 逻辑表达式: L。=A, 40 0L0 L1=A⊕A 0L1 L2=A,A,·A2AA·A3AA 42 L,=AA·AAA L2 (3)由逻辑表达 43 A & 式画出逻辑图。 少机电学院电气工程系 上一页下一页回目绿 退出

机电学院电气工程系 上一页 下一页 回目录 退出 L0 = A0 L1 = A1 A0 L2 A2 A0 A2 A1 A0 A3 A1 A0 = L 3 A3 A2 A3 A1 A0 = 逻辑表达式: (3)由逻辑表达 式画出逻辑图。 4.1 组合逻辑电路的分析方法与设计方法 L L L A & =1 3 L 0 A 1 A & 2 3 0 & 1 A & 1 1 2 & & & 1 1 1 0 0 0 0 0 0

4.2编码器 一、编码器的基本概念及工作原理 编码—将某一特定的逻辑信号变换为二进制代码。 编码器有若干个输入,对每一个有效的输入信号,编 码器产生一组惟一的二进制代码输出。一般而言,N个不同 的信号,至少需要位二进制数编码。N和n之间满足下列关 系: 2>N 能够实现编码功能的逻辑部件称为编码器。 机电学院电气工程系 上一页 下一页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 4.2 编码器 一、编码器的基本概念及工作原理 编码——将某一特定的逻辑信号变换为二进制代码。 编码器有若干个输入,对每一个有效的输入信号,编 码器产生一组惟一的二进制代码输出。一般而言,N个不同 的信号,至少需要n位二进制数编码。N和n之间满足下列关 系: 2 n≥N 能够实现编码功能的逻辑部件称为编码器