第五章时序逻辑电路 5.1、时序逻辑电路与组合逻辑电路的根本区别是什么?同步时序逻辑电路与异步时序电路 的根本区别是什么? 5.2、利用主从JK触发器构成四位二进制加法计数器电路和四位二进制减法计数器电路, 两者连接规律有何不同? 5.3、利用74S160芯片分别构成60进制计数器和24进制计数器。 5.4、采用直接清零法构成任意N进制计数器时,使用74LS162/163芯片和使用74LS160/161 芯片有什么不同?请画出N=12时两者的接线图。 5.5、环形计数设置初态可以通过哪几种方法?画图举例说明。 5.6、画出图P5-1(、(b)所示电路的状态表,状态图和时序波形图,并简述其功能。 ID Q CI FFO P5-1题5-6图

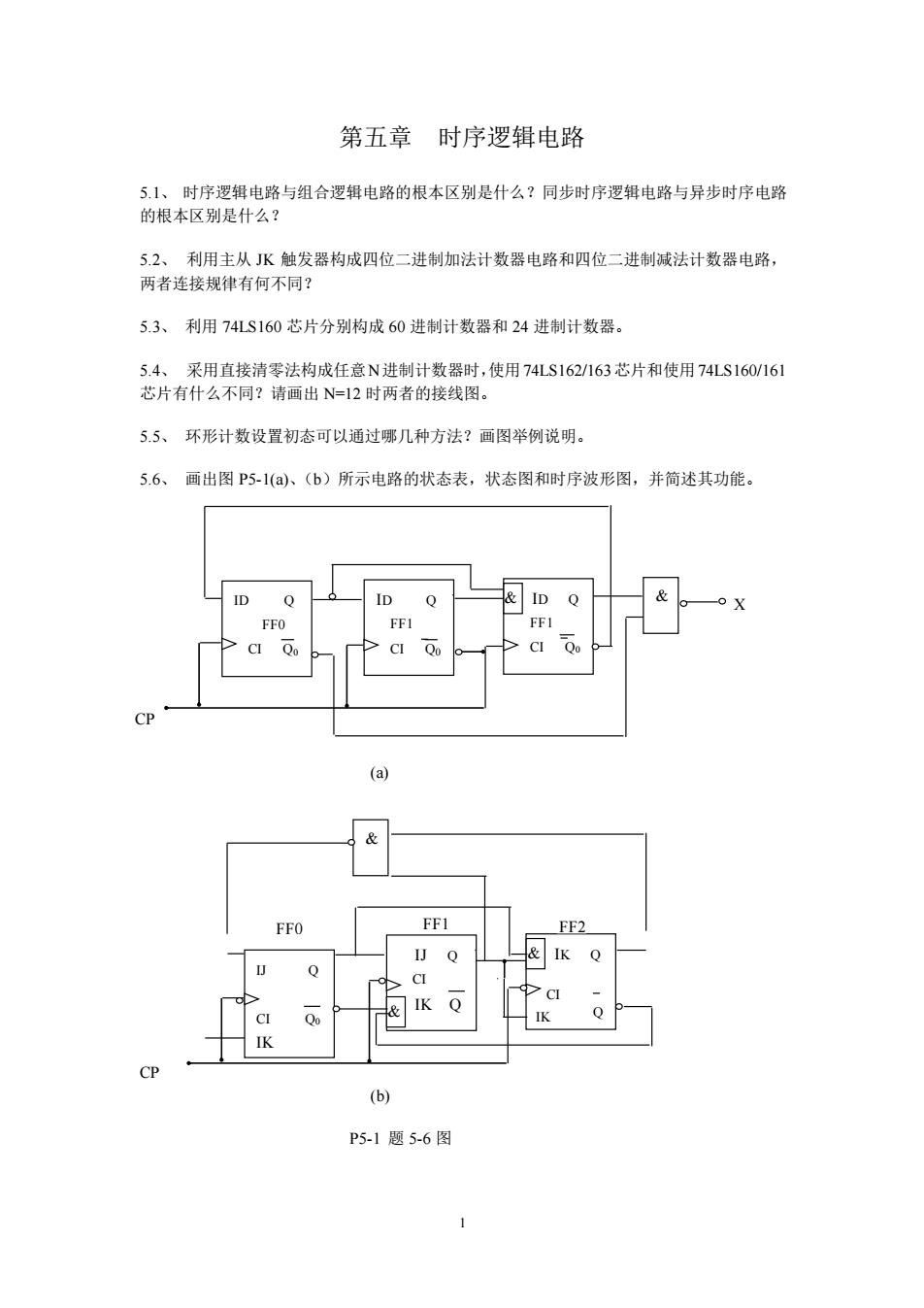

1 第五章 时序逻辑电路 5.1、 时序逻辑电路与组合逻辑电路的根本区别是什么?同步时序逻辑电路与异步时序电路 的根本区别是什么? 5.2、 利用主从 JK 触发器构成四位二进制加法计数器电路和四位二进制减法计数器电路, 两者连接规律有何不同? 5.3、 利用 74LS160 芯片分别构成 60 进制计数器和 24 进制计数器。 5.4、 采用直接清零法构成任意N进制计数器时,使用74LS162/163芯片和使用74LS160/161 芯片有什么不同?请画出 N=12 时两者的接线图。 5.5、 环形计数设置初态可以通过哪几种方法?画图举例说明。 5.6、 画出图 P5-1(a)、(b)所示电路的状态表,状态图和时序波形图,并简述其功能。 ID Q FF0 CI Q0 ID Q FF1 CI Q0 ID Q FF1 CI Q0 & X (a) & CP (b) CP & P5-1 题 5-6 图 IJ Q CI IK Q FF1 IJ Q CI Q0 IK IK Q i & & CI IK Q FF0 FF2

5.6、已知计数器的输出端QQQ,的输出波形图P5-2所示,试画出其对应的状态转换图, 并判断该计数为几进制计数器 图P5-2 57、 试分析图P53所示74S161集成芯片构成的计数器,设初态为0000,请列出其状 态转换表,分析该电路采用何种方式构成几进制的计数器 CPT Qo Q:Q:Q3 CIP 74L.S161 >CP CR Do D:D2 D3 p5-3 59、 采用直接清零法,将集成计数器,74S161(74LS161芯片的引脚排列如图528)构 成9进制计数器,曲出逻辑电路图。 5.10、采用预置复位法,将集成计数器74LS161构成7进制计数器,画出逻辑电路图 5.11 、采用进位输出置最小数法,将集成计数器74S161构成12进制计数器,画出逻辑 电路图。 5.12、采用级联法,将集成计数器74S161构成108进制计数器,画出逻辑电路图。 513. 采用直接清零法,将集成计数器74S290(74S290芯片的引脚排列图见534构 成十进制和五进制的计数器,分别画出逻辑电路图 5.14、 采用级联法将集成计数器74LS290构成64进制计数器,画出逻辑电路图 5.15、利用双向四位TTL集成移位寄存器74LS194(见图54474LS194)引脚排列图)分 别构成分频系数N1=5,N2=6的环形计数器,画出逻辑电路图

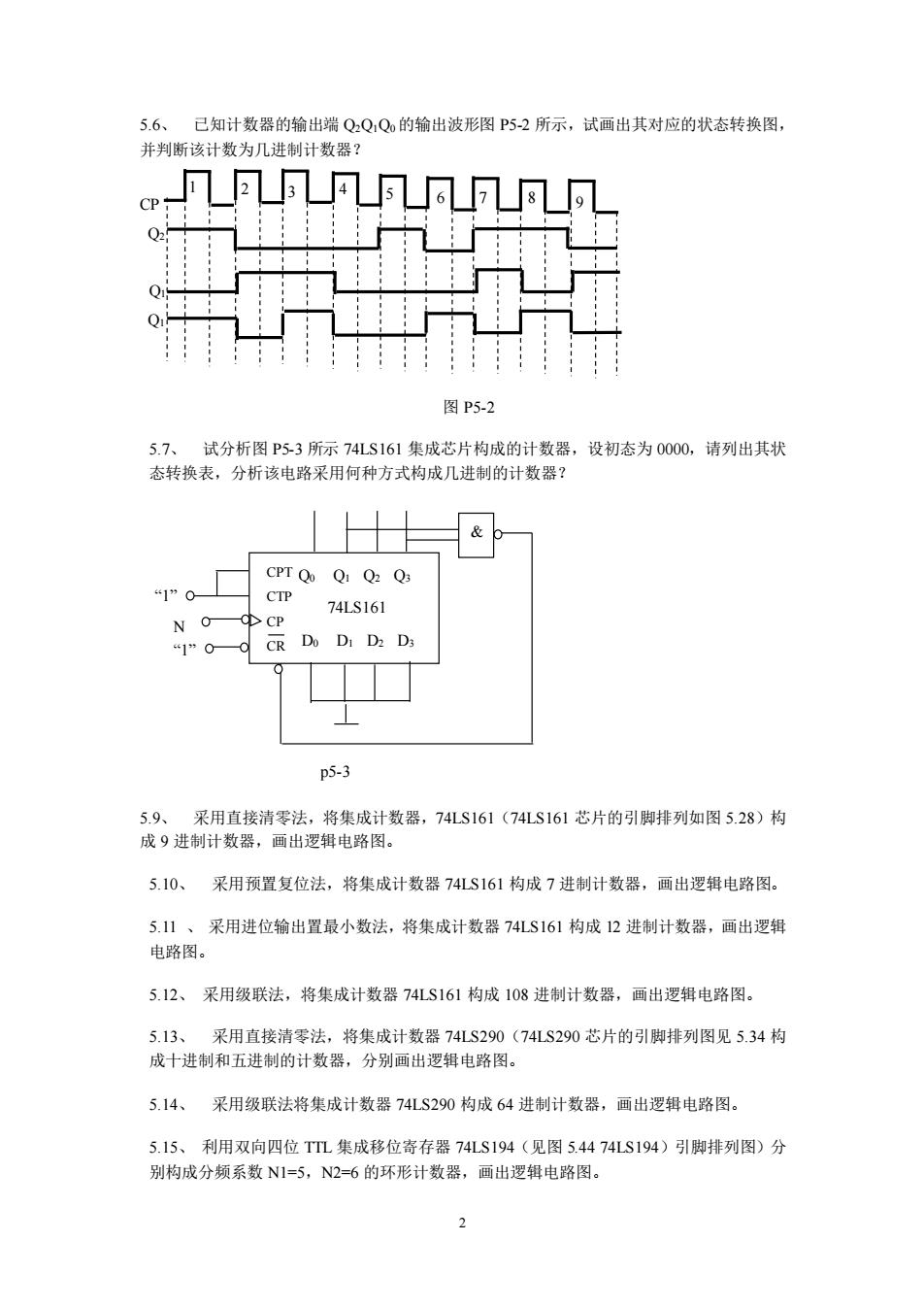

2 5.6、 已知计数器的输出端 Q2Q1Q0 的输出波形图 P5-2 所示,试画出其对应的状态转换图, 并判断该计数为几进制计数器? 图 P5-2 5.7、 试分析图 P5-3 所示 74LS161 集成芯片构成的计数器,设初态为 0000,请列出其状 态转换表,分析该电路采用何种方式构成几进制的计数器? 5.9、 采用直接清零法,将集成计数器,74LS161(74LS161 芯片的引脚排列如图 5.28)构 成 9 进制计数器,画出逻辑电路图。 5.10、 采用预置复位法,将集成计数器 74LS161 构成 7 进制计数器,画出逻辑电路图。 5.11 、 采用进位输出置最小数法,将集成计数器 74LS161 构成 12 进制计数器,画出逻辑 电路图。 5.12、 采用级联法,将集成计数器 74LS161 构成 108 进制计数器,画出逻辑电路图。 5.13、 采用直接清零法,将集成计数器 74LS290(74LS290 芯片的引脚排列图见 5.34 构 成十进制和五进制的计数器,分别画出逻辑电路图。 5.14、 采用级联法将集成计数器 74LS290 构成 64 进制计数器,画出逻辑电路图。 5.15、 利用双向四位 TTL 集成移位寄存器 74LS194(见图 5.44 74LS194)引脚排列图)分 别构成分频系数 N1=5,N2=6 的环形计数器,画出逻辑电路图。 Q0 Q1 Q2 Q3 D0 D1 D2 D3 CPT CTP CP CR & 74LS161 p5-3 1 2 3 4 5 6 7 8 CP 9 Q2 2 Q1 Q2 1 2 N “1” “1

5.16、见图P5-4所示的两级」-K触发器构成的加法计数器,请分析是几进制计数器,若 要改接成3进制加法计数器,该怎么改接?画出逻辑电路图。 19 NO- K K P5-4 5.17利用1024×1RAM2102A构成2048×4RAM,画出连接图。现要求在地址10、1023 1024、2046、2047共5个单元中分别存储数据(D3、D2、D1、D0)的值为(1010)、(1001) (0101)、(1111)和(0001),请用编程图标明RAW中写入的内容。 5.18某编程函数为: F=ABC+AC+ACD+BD F=AC+BD+ABD+AC D: E=ABC+BD+ACD+BCD: 则使用PLA实现上述编程函数需要最少的乘积线(位线)多少条,“或”线多少条?

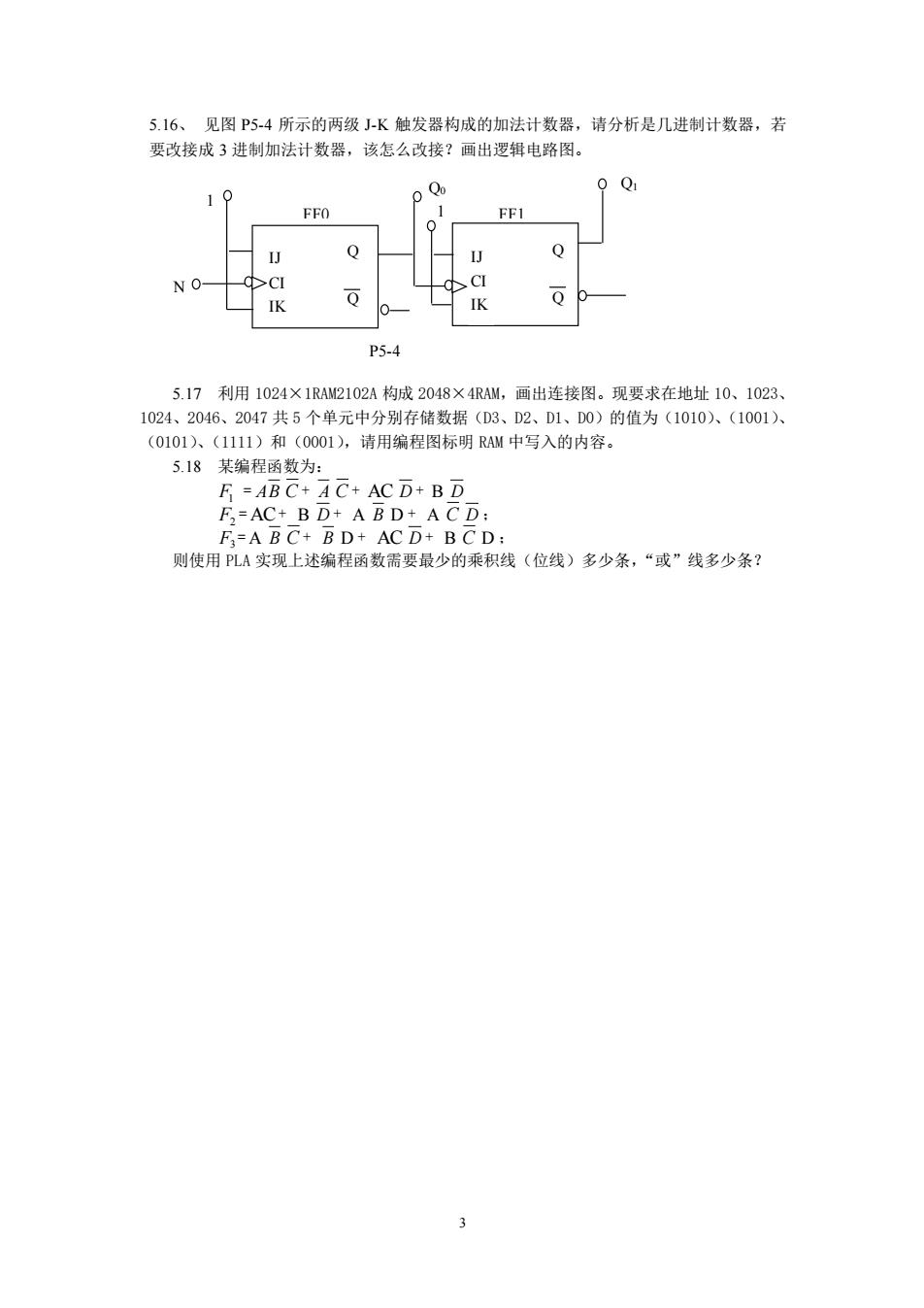

3 5.16、 见图 P5-4 所示的两级 J-K 触发器构成的加法计数器,请分析是几进制计数器,若 要改接成 3 进制加法计数器,该怎么改接?画出逻辑电路图。 5.17 利用 1024×1RAM2102A 构成 2048×4RAM,画出连接图。现要求在地址 10、1023、 1024、2046、2047 共 5 个单元中分别存储数据(D3、D2、D1、D0)的值为(1010)、(1001)、 (0101)、(1111)和(0001),请用编程图标明 RAM 中写入的内容。 5.18 某编程函数为: F1 = AB C + A C + AC D + B D F2 = AC + B D + A B D + A C D ; F3 = A B C + B D + AC D + B C D ; 则使用 PLA 实现上述编程函数需要最少的乘积线(位线)多少条,“或”线多少条? IJ CI IK Q Q IJ CI IK Q Q Q1 Q 1 Q N Q Q0 Q FF0 Q FF1 Q P5-4 Q 1