K康芯科技 EDA技术与VHDL 第5章 VHDL状态机

EDA技术与VHDL 第5章 VHDL状态机 KX 康芯科技

K能科拉 5.1状态机设计相关语句 5.1.1类型定义语句 TYPE 数据类型名工S 数据类型定义OF基本数据类型:或 TYPE 数据类型名 IS 数据类型定义; TYPE st1 IS ARRAY 0 TO 15 OF STD LOGIC; TYPE week IS (sun,mon,tue,wed,thu,fri,sat); TYPE m state IS st0,stl,st2,st3,st4,st5 ) SIGNAL present state,next state m state TYPE BOOLEAN IS (FALSE,TRUE);

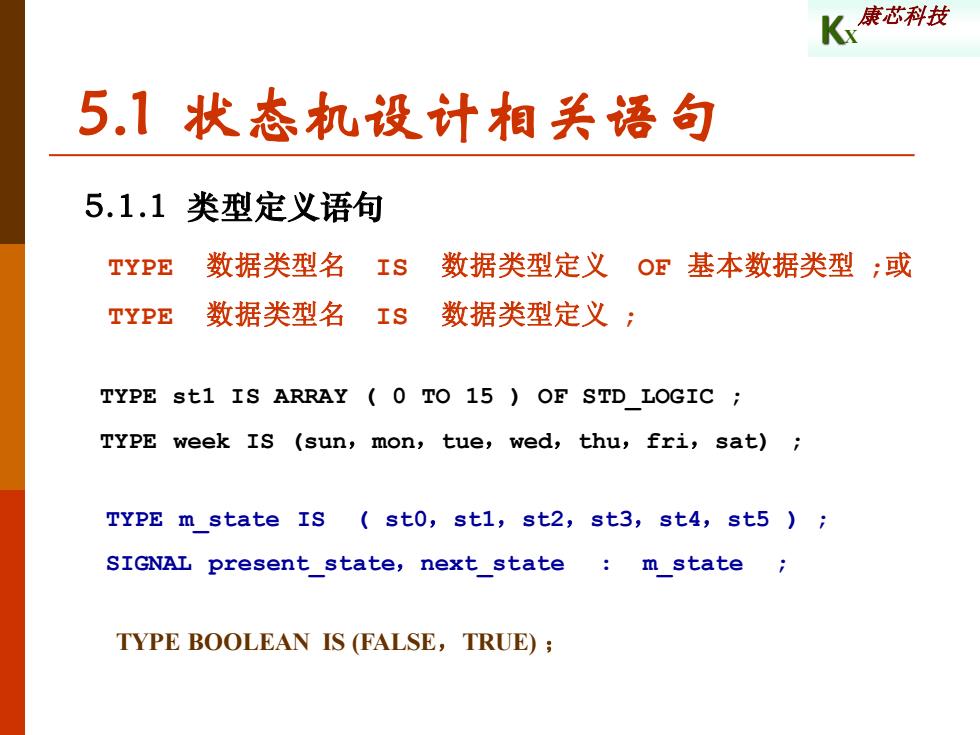

KX 康芯科技 5.1 状态机设计相关语句 5.1.1 类型定义语句 TYPE 数据类型名 IS 数据类型定义 OF 基本数据类型 ;或 TYPE 数据类型名 IS 数据类型定义 ; TYPE st1 IS ARRAY ( 0 TO 15 ) OF STD_LOGIC ; TYPE week IS (sun,mon,tue,wed,thu,fri,sat) ; TYPE m_state IS ( st0,st1,st2,st3,st4,st5 ) ; SIGNAL present_state,next_state : m_state ; TYPE BOOLEAN IS (FALSE,TRUE) ;

K康科技 5.1状态机设计相关语句 5.1.1类型定义语句 TYPE my logic IS 1,Z,U',0); SIGNAL s1 my logic i s1<=Z; SUBTYPE子类型名IS基本数据类型RANGE约束范围; SUBTYPE digits IS INTEGER RANGE 0 to 9;

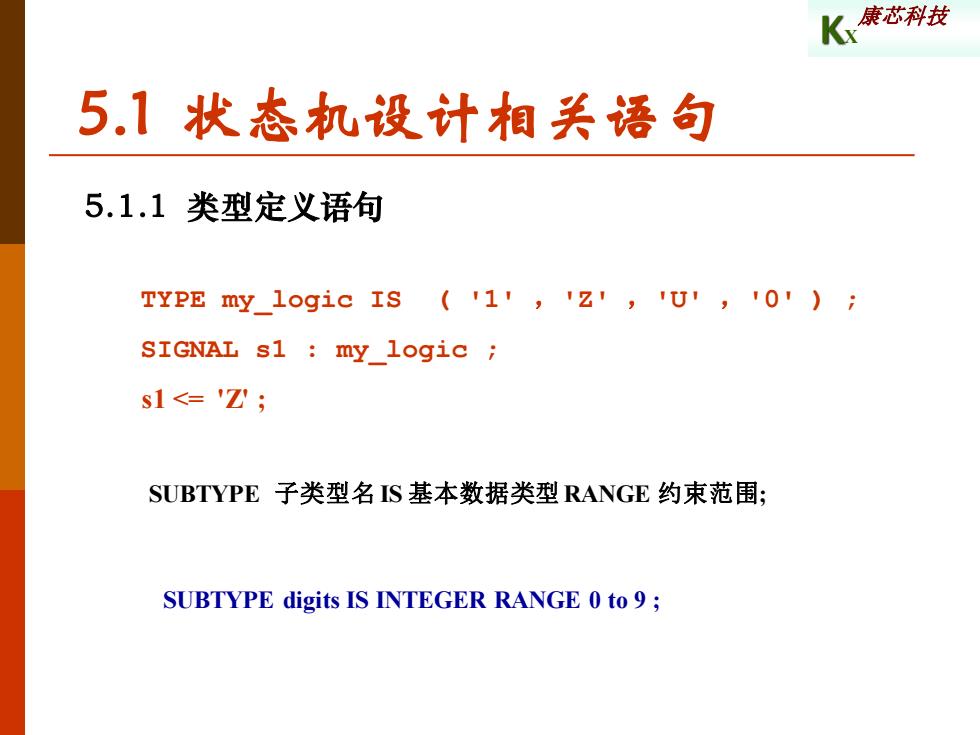

KX 康芯科技 5.1 状态机设计相关语句 5.1.1 类型定义语句 TYPE my_logic IS ( '1' ,'Z' ,'U' , '0' ) ; SIGNAL s1 : my_logic ; s1 <= 'Z' ; SUBTYPE 子类型名IS 基本数据类型 RANGE 约束范围; SUBTYPE digits IS INTEGER RANGE 0 to 9 ;

K康芯科技 5.1状态机设计相关语句 5.1.2状态机的优势 1.状态机克服了纯硬件数字系统顺序方式控制不灵活的缺点; 2.由于状态机的结构相对简单,设计方案相对固定; 3、状态机容易构成性能良好的同步时序逻辑模块; 4、与VDL的其他描述方式相比,状态机的VDL表述丰富多样、 程序层次分明,结构清晰,易读易懂;在排错、修改和模块移植 方面也有其独到的好处; 5、在高速运算和控制方面,状态机更有其巨大的优势。 6、高可靠性

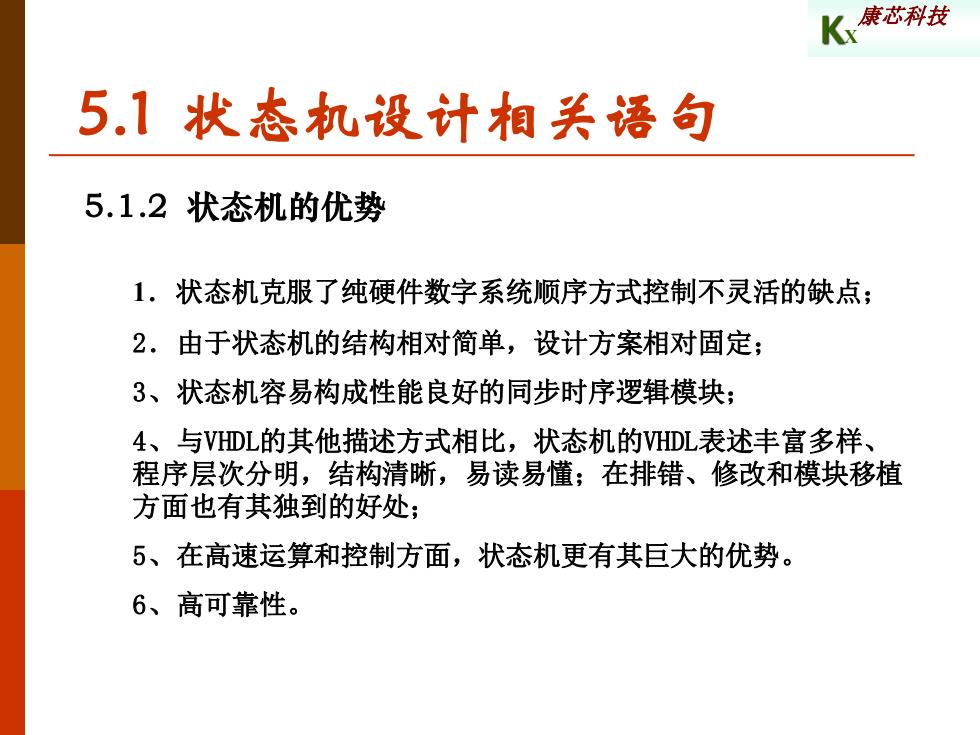

KX 康芯科技 5.1 状态机设计相关语句 5.1.2 状态机的优势 1.状态机克服了纯硬件数字系统顺序方式控制不灵活的缺点; 2.由于状态机的结构相对简单,设计方案相对固定; 3、状态机容易构成性能良好的同步时序逻辑模块; 4、与VHDL的其他描述方式相比,状态机的VHDL表述丰富多样、 程序层次分明,结构清晰,易读易懂;在排错、修改和模块移植 方面也有其独到的好处; 5、在高速运算和控制方面,状态机更有其巨大的优势。 6、高可靠性

K康还科技 5.1状态机设计相关语句 5.1.3状态机结构 1.说明部分 ARCHITECTURE·,.IS TYPE FSM ST IS (s0,s1,s2,s3); SIGNAL current state,next state:FSM ST;

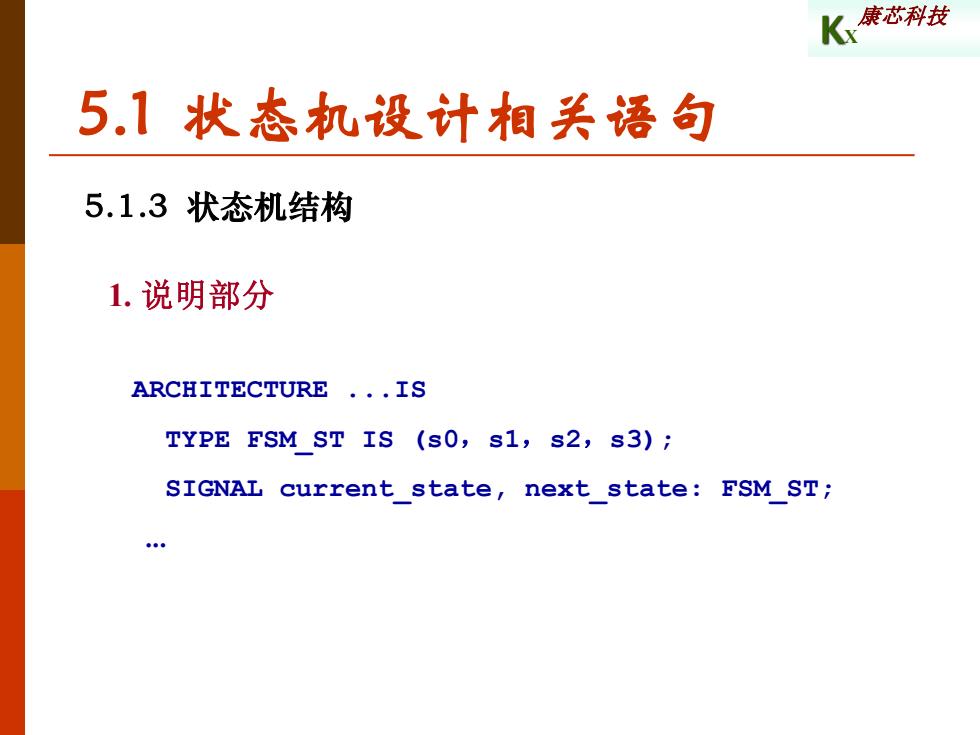

KX 康芯科技 5.1 状态机设计相关语句 5.1.3 状态机结构 1. 说明部分 ARCHITECTURE .IS TYPE FSM_ST IS (s0,s1,s2,s3); SIGNAL current_state, next_state: FSM_ST;