K康芯科技 EDA技术与VHDL 第3章 VHDL基础

EDA技术与VHDL 第3章 VHDL 基础 KX 康芯科技

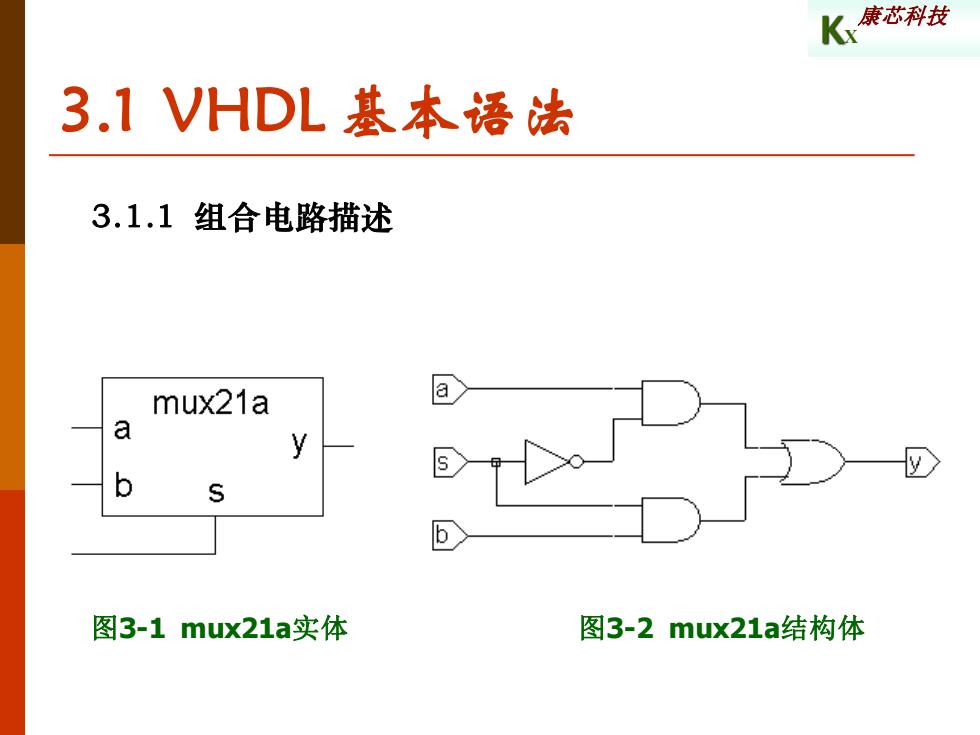

K能芯科技 3.1VHDL基本语法 3.1.1组合电路描述 mux21a y S 图3-1mux21a实体 图3-2mux21a结构体

KX 康芯科技 3.1 VHDL 基本语法 3.1.1 组合电路描述 图3-1 mux21a实体 图3-2 mux21a结构体

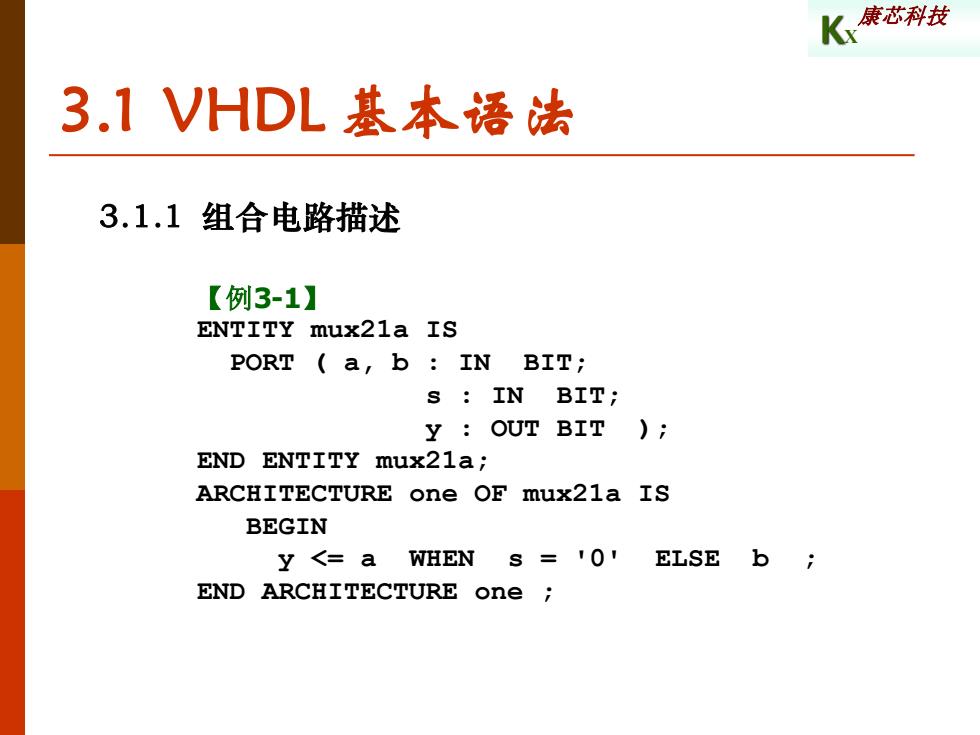

K康还科技 3.1VHDL基本语法 3.1.1组合电路描述 【例3-1】 ENTITY mux21a IS PORT(a,b:IN BIT; s IN BIT; y:OUT BIT ) END ENTITY mux21a; ARCHITECTURE one OF mux21a IS BEGIN y <a WHEN s=0 ELSE b; END ARCHITECTURE one

KX 康芯科技 3.1 VHDL 基本语法 3.1.1 组合电路描述 【例3-1】 ENTITY mux21a IS PORT ( a, b : IN BIT; s : IN BIT; y : OUT BIT ); END ENTITY mux21a; ARCHITECTURE one OF mux21a IS BEGIN y <= a WHEN s = '0' ELSE b ; END ARCHITECTURE one ;

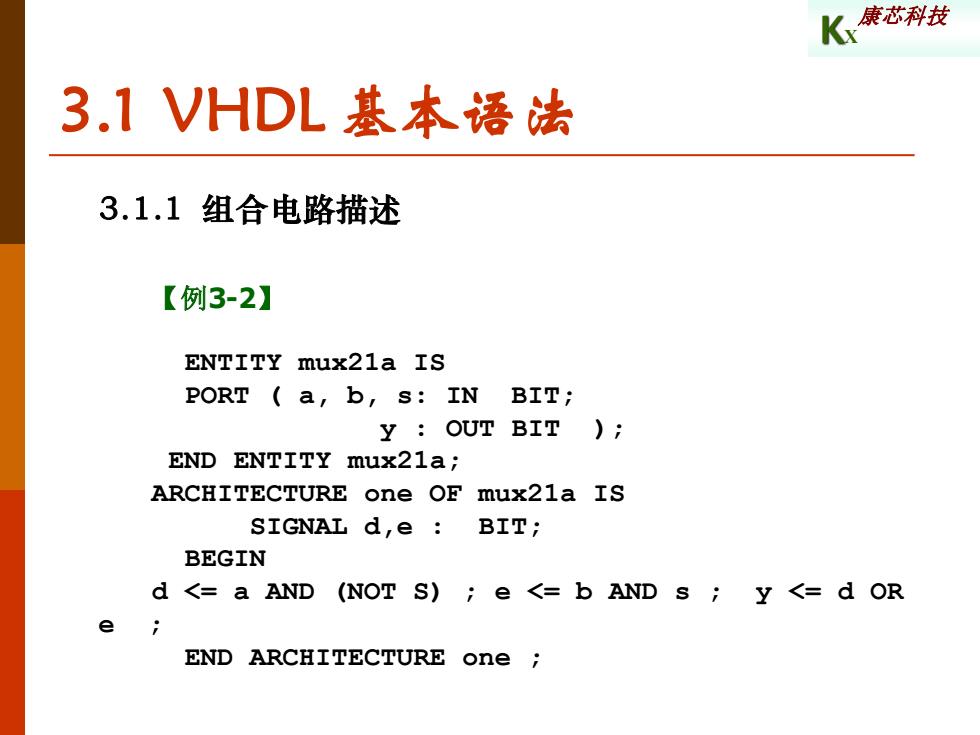

K能苏科技 3.1VHDL基本语法 3.1.1组合电路描述 【例3-2】 ENTITY mux21a IS PORT(a,b,S:IN BIT; y:OUT BIT ) END ENTITY mux21a; ARCHITECTURE one OF mux21a IS SIGNAL d,e:BIT; BEGIN d <-a AND (NOT S);e <-b AND s y <d OR e END ARCHITECTURE one;

KX 康芯科技 3.1 VHDL 基本语法 3.1.1 组合电路描述 【例3-2】 ENTITY mux21a IS PORT ( a, b, s: IN BIT; y : OUT BIT ); END ENTITY mux21a; ARCHITECTURE one OF mux21a IS SIGNAL d,e : BIT; BEGIN d <= a AND (NOT S) ; e <= b AND s ; y <= d OR e ; END ARCHITECTURE one ;

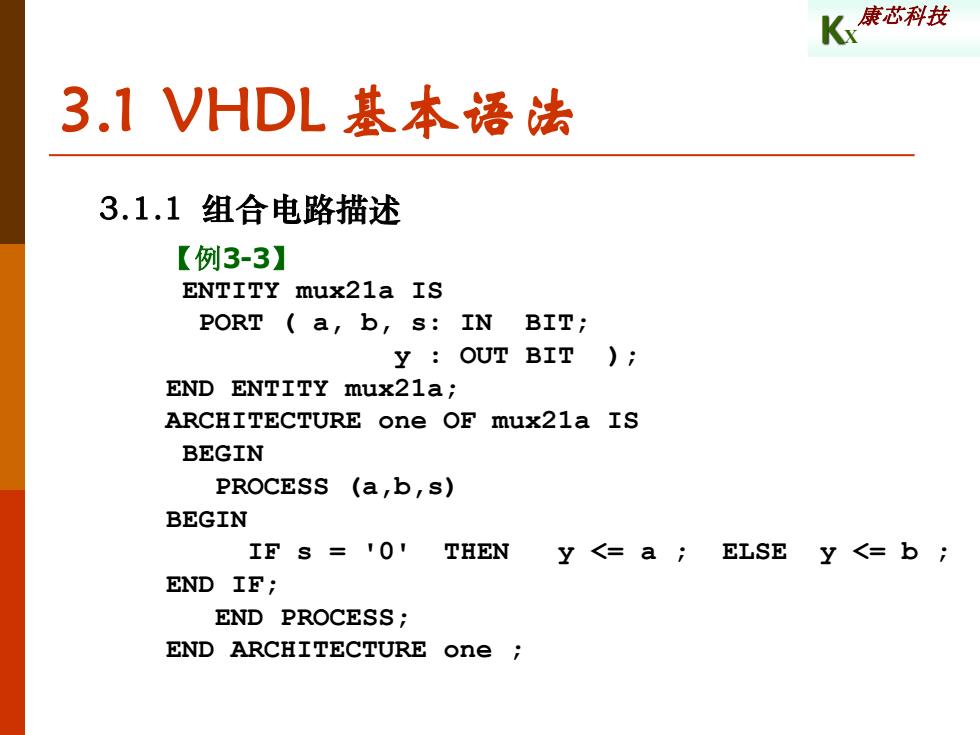

K康还科技 3.1VHDL基本语法 3.1.1组合电路描述 【例3-3】 ENTITY mux21a IS PORT a,b,s:IN BIT; y:OUT BIT ) END ENTITY mux21a; ARCHITECTURE one OF mux21a IS BEGIN PROCESS (a,b,s) BEGIN IF s =10'THEN y <a E工SEY<=b; END IF; END PROCESS; END ARCHITECTURE one;

KX 康芯科技 3.1 VHDL 基本语法 【例3-3】 ENTITY mux21a IS PORT ( a, b, s: IN BIT; y : OUT BIT ); END ENTITY mux21a; ARCHITECTURE one OF mux21a IS BEGIN PROCESS (a,b,s) BEGIN IF s = '0' THEN y <= a ; ELSE y <= b ; END IF; END PROCESS; END ARCHITECTURE one ; 3.1.1 组合电路描述