K康芯科技 EDA技术与VHDL 第7章 VHDL语句

EDA技术与VHDL 第7章 VHDL语句 KX 康芯科技

K康科技 7.1顺序语句 7.1.1赋值语句 信号赋值语句 变量赋值语句 7.1.2F语句 7.1.3CASE语句 选择值[|选择值] 单个普通数值,如6。 数值选择范围,如(2T04),表示取值为2、3或4。 并列数值,如35,表示取值为3或者5。 混合方式,以上三种方式的混合

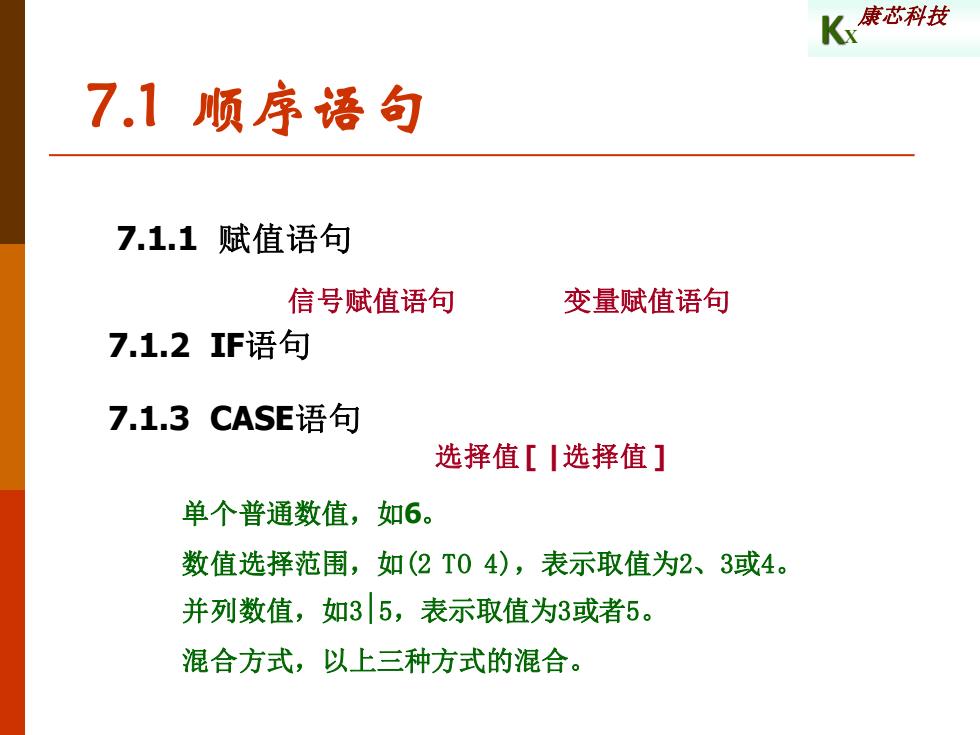

KX 康芯科技 7.1 顺序语句 7.1.1 赋值语句 信号赋值语句 变量赋值语句 7.1.2 IF语句 7.1.3 CASE语句 选择值 [ |选择值 ] 单个普通数值,如6。 数值选择范围,如(2 TO 4),表示取值为2、3或4。 并列数值,如35,表示取值为3或者5。 混合方式,以上三种方式的混合

K康芯科技 【例7-1】 LIBRARY IEEE; USE IEEE.STD LOGIC 1164.ALL; ENTITY mux41 IS PORT (s4,s3,s2,s1 IN STD LOGIC; z4,z3,z2,z1 OUT STD LOGIC); END mux41; ARCHITECTURE activ OF mux41 IS SIGNAL sel:INTEGER RANGE 0 TO 15; BEGIN PROCESS (sel,s4,s3,s2,s1 BEGIN se1<=0: -输入初始值 IF (s1 ='1')THEN sel <sel+1 ELSIF (s2 ='1')THEN sel <sel+2 ELSIF (s3 ='1')THEN sel <sel+4 ELSIF (s4 ='1')THEN sel <sel+8 ELSE NULL; -} 注意,这里使用了空操作语句 END IF z1<='0';z2<='0';z3<='0';z4<='0';-输入初始值 CASE sel IS EN0=>z1<='1': -当se1=0时选中 WHEN13=>,z2<='1I; -当se1为1或3时选中 WEN4To72=>z3<='1'; 当se1为2、4、5、6或7时选中 WHEN OTHERS =z4<=1; 当se1为8~15中任一值时选中 END CASE END PROCESS END activ

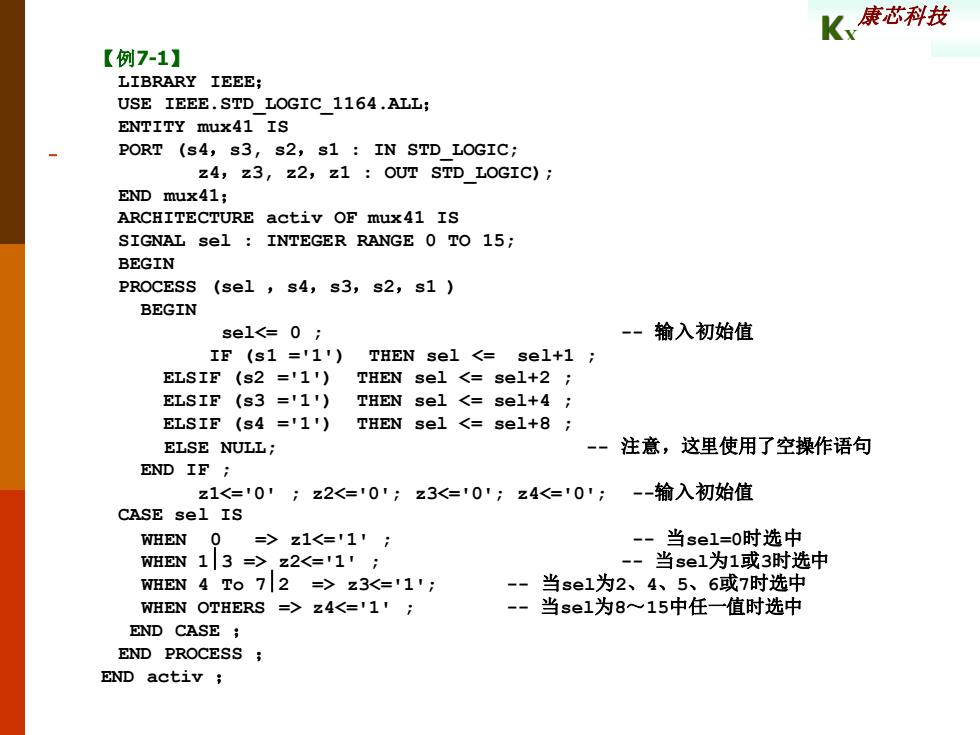

KX 康芯科技 【例7-1】 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY mux41 IS PORT (s4,s3, s2,s1 : IN STD_LOGIC; z4,z3, z2,z1 : OUT STD_LOGIC); END mux41; ARCHITECTURE activ OF mux41 IS SIGNAL sel : INTEGER RANGE 0 TO 15; BEGIN PROCESS (sel ,s4,s3,s2,s1 ) BEGIN sel<= 0 ; - 输入初始值 IF (s1 ='1') THEN sel <= sel+1 ; ELSIF (s2 ='1') THEN sel <= sel+2 ; ELSIF (s3 ='1') THEN sel <= sel+4 ; ELSIF (s4 ='1') THEN sel <= sel+8 ; ELSE NULL; - 注意,这里使用了空操作语句 END IF ; z1<='0' ; z2<='0'; z3<='0'; z4<='0'; -输入初始值 CASE sel IS WHEN 0 => z1<='1' ; - 当sel=0时选中 WHEN 13 => z2<='1' ; - 当sel为1或3时选中 WHEN 4 To 72 => z3<='1'; - 当sel为2、4、5、6或7时选中 WHEN OTHERS => z4<='1' ; - 当sel为8~15中任一值时选中 END CASE ; END PROCESS ; END activ ;

K康还科技 7.1顺序语句 7.1.3 CASE语句 【例7-2】 SIGNAL value INTEGER RANGE 0 TO 15; SIGNAL out1 STD LOGIC 。0 CASE value IS -缺少以WN引导的条件句 END CASE; 。· CASE value IS WHEN 0 =out1<=1; va1ue2~15的值未包括进去 WHEN 1 =out1<=0; END CASE CASE value IS WHEN0T010=>out1<='1';-选择值中5~10的值有重叠 HEN5T015=>out1<='0'; END CASE:

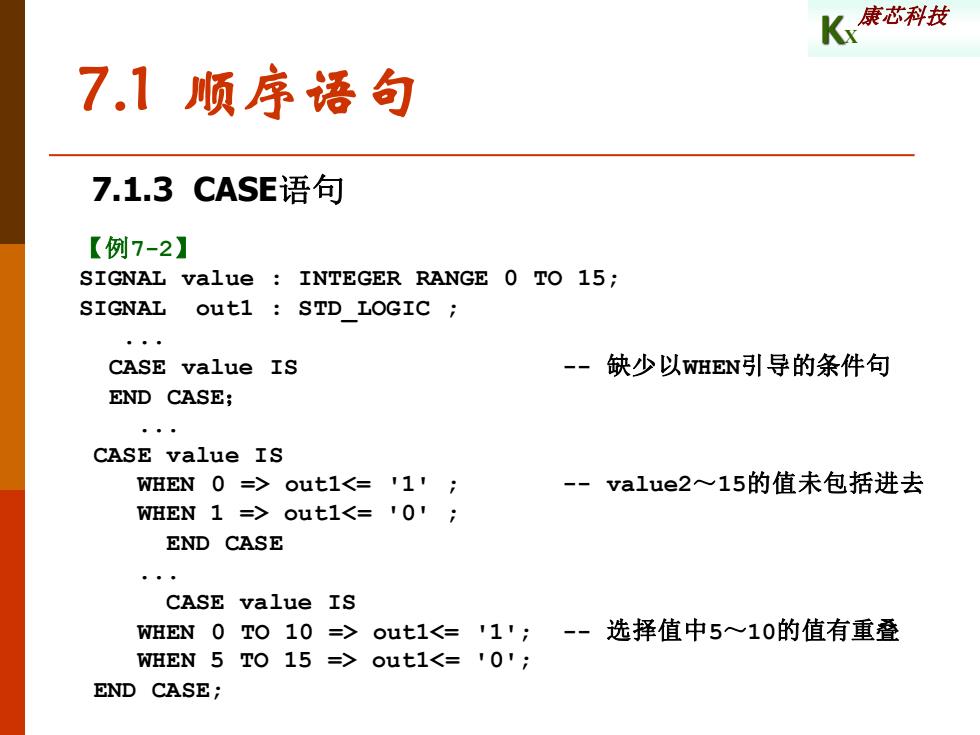

KX 康芯科技 7.1 顺序语句 7.1.3 CASE语句 【例7-2】 SIGNAL value : INTEGER RANGE 0 TO 15; SIGNAL out1 : STD_LOGIC ; . CASE value IS - 缺少以WHEN引导的条件句 END CASE; . CASE value IS WHEN 0 => out1<= '1' ; - value2~15的值未包括进去 WHEN 1 => out1<= '0' ; END CASE . CASE value IS WHEN 0 TO 10 => out1<= '1'; - 选择值中5~10的值有重叠 WHEN 5 TO 15 => out1<= '0'; END CASE;

【例7-3】 LIBRARY IEEE: USE IEEE.STD LOGIC 1164.ALL; USE IEEE.STD LOGIC UNSIGNED.ALL; ENTITY alu IS PORT a,b IN STD LOGIC VECTOR (7 DOWNTO 0); opcode:IN STD LOGIC VECTOR (1 DOWNTO 0); result:OUT STD LOGIC VECTOR (7 DOWNTO 0)); END alu; ARCHITECTURE behave OF alu IS CONSTANT plus STD LOGIC VECTOR (1 DOWNTO 0):=b"00"; CONSTANT minus STD LOGIC VECTOR (1 DOWNTO 0):=b"01"; CONSTANT equal STD LOGIC VECTOR (1 DOWNTO 0):=b"10"; CONSTANT not equal:STD_LOGIC_VECTOR (1 DOWNTO 0):=b"11"; BEGIN PROCESS (opcode,a,b) BEGIN CASE opcode IS EN plus=>result<=a+b;-a、b相加 WHEN minus =result <a -b; -a、b相减 WHEN equal = -a、b相等 IF (a =b)THEN result <x"01"; ELSE result <x"00"; END IF; WHEN not equal = -a、b不相等 IF (a /b)THEN result <x"01"; ELSE result <x"00"; END IF; END CASE; END PROCESS; END behave;

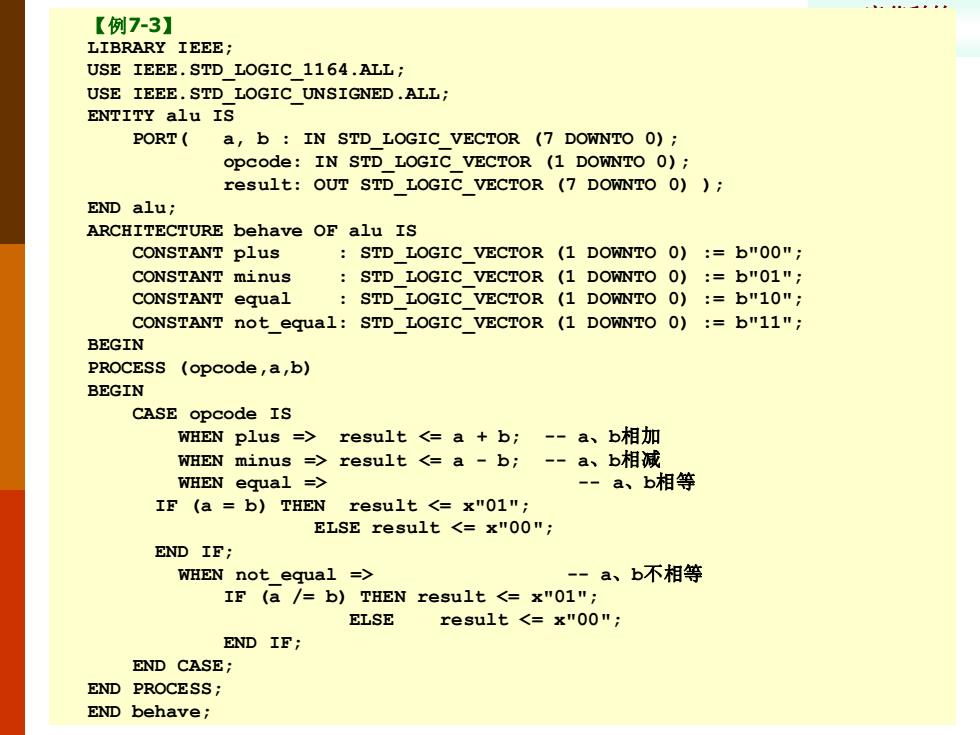

KX 【例7-3】 康芯科技 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY alu IS PORT( a, b : IN STD_LOGIC_VECTOR (7 DOWNTO 0); opcode: IN STD_LOGIC_VECTOR (1 DOWNTO 0); result: OUT STD_LOGIC_VECTOR (7 DOWNTO 0) ); END alu; ARCHITECTURE behave OF alu IS CONSTANT plus : STD_LOGIC_VECTOR (1 DOWNTO 0) := b"00"; CONSTANT minus : STD_LOGIC_VECTOR (1 DOWNTO 0) := b"01"; CONSTANT equal : STD_LOGIC_VECTOR (1 DOWNTO 0) := b"10"; CONSTANT not_equal: STD_LOGIC_VECTOR (1 DOWNTO 0) := b"11"; BEGIN PROCESS (opcode,a,b) BEGIN CASE opcode IS WHEN plus => result <= a + b; - a、b相加 WHEN minus => result <= a - b; - a、b相减 WHEN equal => - a、b相等 IF (a = b) THEN result <= x"01"; ELSE result <= x"00"; END IF; WHEN not_equal => - a、b不相等 IF (a /= b) THEN result <= x"01"; ELSE result <= x"00"; END IF; END CASE; END PROCESS; END behave;