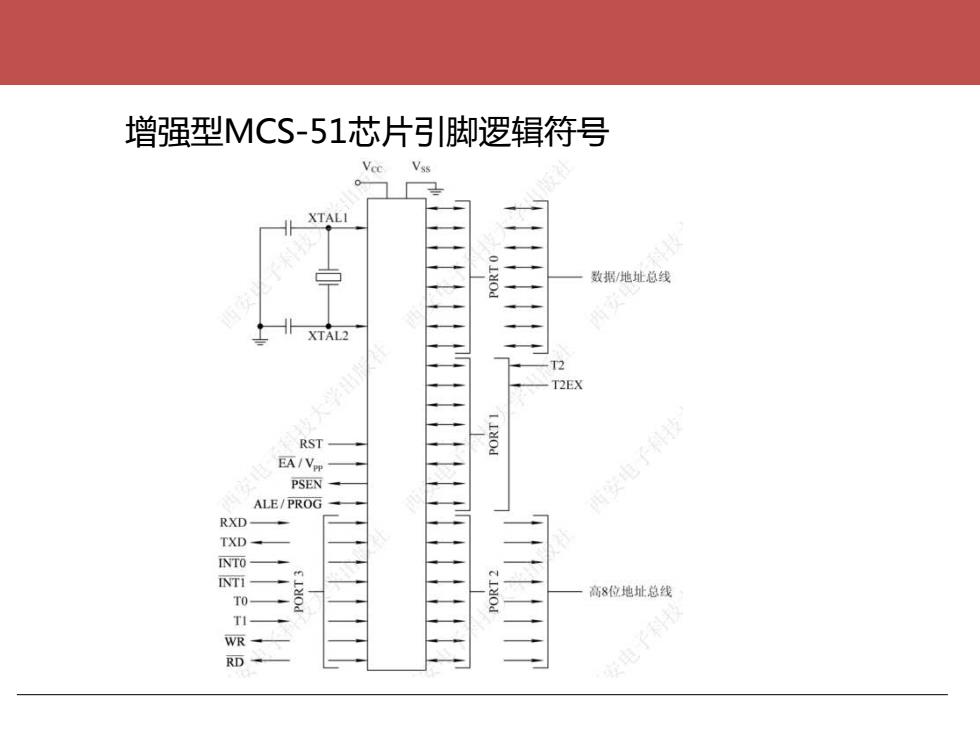

增强型MCS-51芯片引脚逻辑符号VetVssXTAL数据/地址总线XTAL2T2T2EX西安电子科技RSTEA/VppPSENALE/PROGRXDTXDINTOOINT1高8位地址总线TO安电子科技TIWRRD

增强型MCS-51芯片引脚逻辑符号

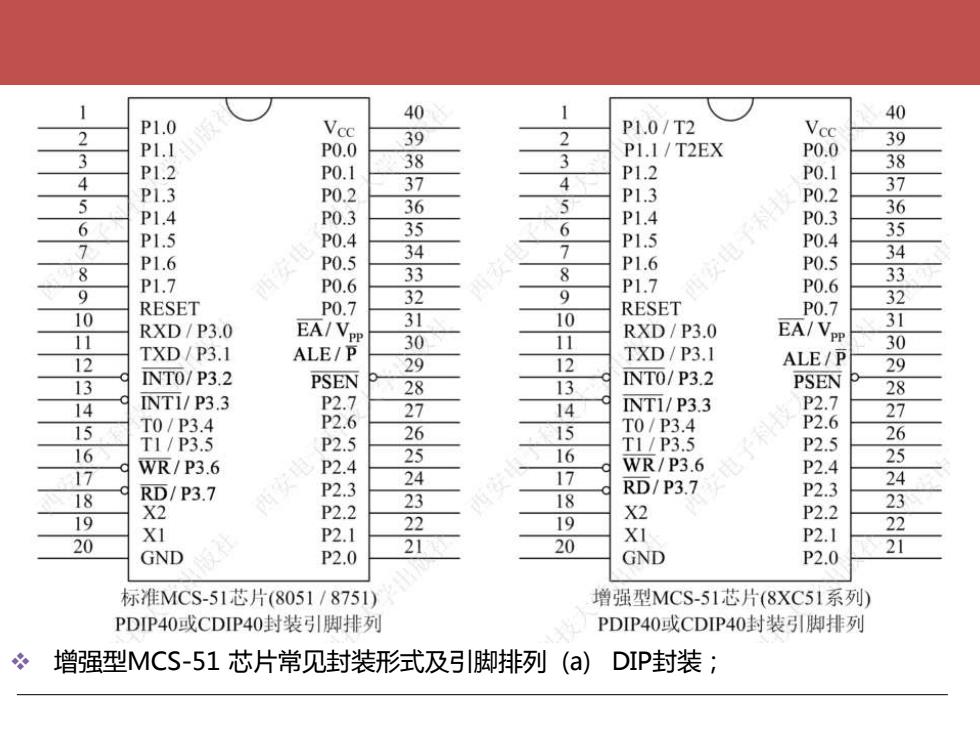

-14040P1.0VccP1.0/T2Vcc223939PI.1PO.0PO.0P1.1/T2EX333838P1.2P1.2P0.1P0.1437374P1.3PO.2P1.3PO.2553636P1.4P0.3P1.4P0.3663535P1.5P1.5P0.4P0.4安电子773434P1.6P1.6P0.5P0.5338338P1.7P0.6P1.7P0.6993232P0.7RESETP0.7RESET31311010EA/VppEA/VpPRXD/P3.0RXD/P3.030113011TXD/P3.1ALEIPTXD /P3.1ALE/P29291212INTO/P3.2INTO/P3.2PSENPSEN13281328P2.7INT1/P3.3P2.7INT1/P3.327142714P2.6P2.6TO/P3.4TO/P3.426152615P2.5P2.5T1 / P3.5T1/P3.516251625P2.4WR/P3.6P2.4WR/P3.624172417RD/P3.7P2.3P2.3RD/P3.723182318X2P2.2P2.2X222192219XIXIP2.1P2.121202120P2.0GNDP2.0GND标准MCS-51芯片(8051/8751)增强型MCS-51芯片(8XC51系列)PDIP40或CDIP40封装引脚排列PDIP40或CDIP40封装引脚排列DIP封装;增强型MCS-51芯片常见封装形式及引脚排列(a)X

❖ 增强型MCS-51 芯片常见封装形式及引脚排列 (a) DIP封装;

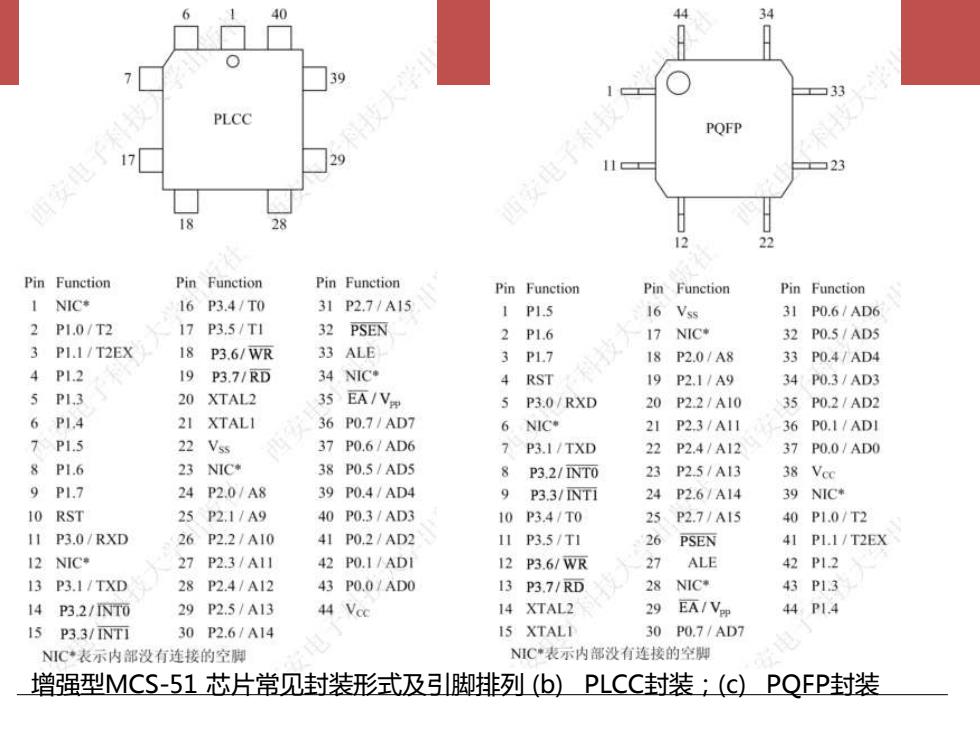

44346140C口O3933科技大PLCC西安电子科技PQFP172911023西安电01828L1222PinPinFunctionFunctionPin FunctionPin FunctionPinPinFunctionFunction-NIC*16P3.4/TO31P2.7/A15161P1.5Vss31P0.6/AD617232PL.0/T2P3.5/T1PSENNIC*21732PO.5/ADSP1.6技318P1.1/T2EX33ALEP3.6/WR3PL71833P2.0/A8P0.4/AD441934NIC*P1.2P3.7/RD4RST1934P2.1/A9P0.3/AD35P132035EA/VmXTAL252035P3.0/RXDP2.2/A10P0.2/AD2216PL436PO.7/AD7XTALINIC*621P2.3/A1136PO.1/ADI7P1.522Vss37P0.67AD672237P3.1/TXDP2.4/A12PO.0/ADO823NIC*P1.638P0.5/ADS23388P2.5/A13VecP3.2/INTO9P1.724P2.0/A839P0.4/AD492439NIC*P3.3/INTIP2.6/A142510RSTP2.11A940P0.3/AD31025P3.4/TOP2.7/A1540P1.0/T22611P3.0/RXDP2.2/A1041PO.2/AD21126P3.5/TIPSEN41P1.1/T2EXNIC*27274212P2.3/A114212ALEP1.2PO.1/ADIP3.6/WRNIC*132843132843P1.3P3.1/TXDP2.4/A12PO.0/ADOP3.7/RDEA/Vp14292944P1.4P2.5/A1344Vcc14XTAL2P3.2/INTO15XTALI301530P0.7/AD7P3.3/INTIP2.6/A14HNIC*表示内部没有连接的空脚NIC*表示内部没有连接的空脚增强型MCS-51芯片常见封装形式及引脚排列(b)PLCC封装:(c)PQFP封装

增强型MCS-51 芯片常见封装形式及引脚排列 (b) PLCC封装;(c) PQFP封装

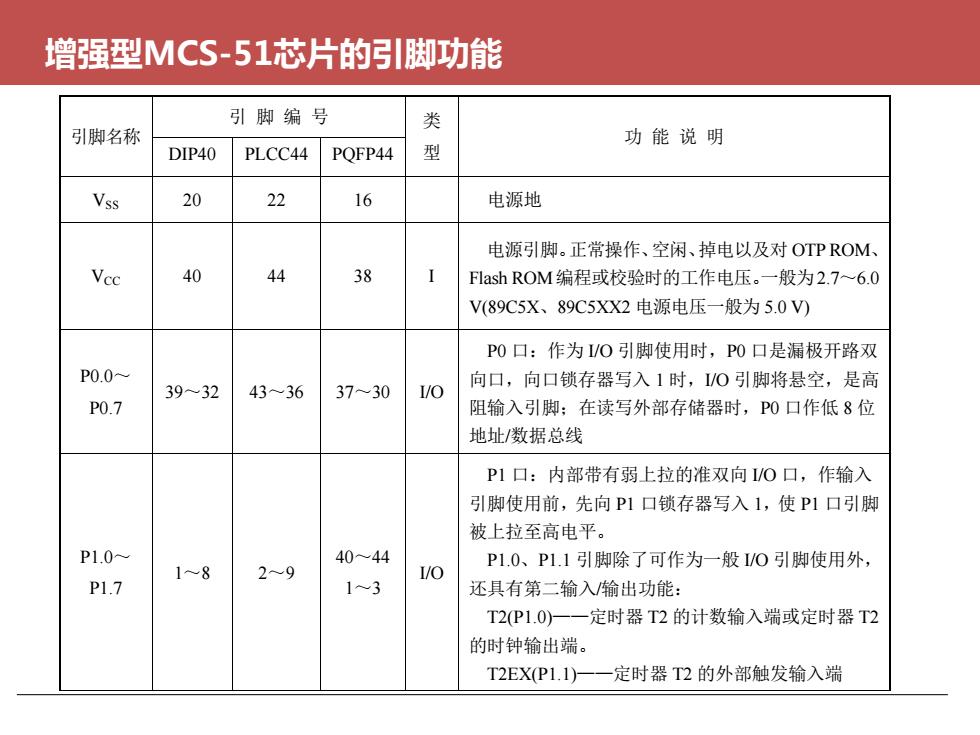

增强型MCS-51芯片的引脚功能引脚编号类引脚名称功能说明型DIP40PLCC44PQFP442022Vss16电源地电源引脚。正常操作、空闲、掉电以及对OTPROM、4044381VccFlashROM编程或校验时的工作电压。一般为2.7~6.0V(89C5X、89C5XX2电源电压一般为5.0V)PO口:作为I/O引脚使用时,PO口是漏极开路双PO.0~向口,向口锁存器写入1时,IO引脚将悬空,是高1/039~3243~3637~30P0.7阻输入引脚;在读写外部存储器时,PO口作低8位地址/数据总线P1口:内部带有弱上拉的准双向I/O口,作输入引脚使用前,先向P1口锁存器写入1,使P1口引脚被上拉至高电平。P1.0~40~44P1.0、P1.1引脚除了可作为一般I/O引脚使用外,I/O1~82~91~3P1.7还具有第二输入/输出功能:T2(P1.0)一一定时器T2的计数输入端或定时器T2的时钟输出端。T2EX(P1.1)一一定时器T2的外部触发输入端

增强型MCS-51芯片的引脚功能 引脚名称 引 脚 编 号 类 型 功 能 说 明 DIP40 PLCC44 PQFP44 VSS 20 22 16 电源地 VCC 40 44 38 I 电源引脚。正常操作、空闲、掉电以及对 OTP ROM、 Flash ROM编程或校验时的工作电压。一般为2.7~6.0 V(89C5X、89C5XX2 电源电压一般为 5.0 V) P0.0~ P0.7 39~32 43~36 37~30 I/O P0 口:作为 I/O 引脚使用时,P0 口是漏极开路双 向口,向口锁存器写入 1 时,I/O 引脚将悬空,是高 阻输入引脚;在读写外部存储器时,P0 口作低 8 位 地址/数据总线 P1.0~ P1.7 1~8 2~9 40~44 1~3 I/O P1 口:内部带有弱上拉的准双向 I/O 口,作输入 引脚使用前,先向 P1 口锁存器写入 1,使 P1 口引脚 被上拉至高电平。 P1.0、P1.1 引脚除了可作为一般 I/O 引脚使用外, 还具有第二输入/输出功能: T2(P1.0)——定时器 T2 的计数输入端或定时器 T2 的时钟输出端。 T2EX(P1.1)——定时器 T2 的外部触发输入端

表2-2增强型MCS-51芯片的引脚功能P2口:内部带有弱上拉的准双向I/O口,作输入P2.0~引脚使用前,先向P2口锁存器写入1,使P2口引脚21~28I/O24~3118~25P2.7被上拉至高电平。在读/写外部存储器时,P2口输出高8位地址信号A15~A85,10~1711,I/OP3口:内部带有弱上拉的准双向I/O口,作输入13~197~13引脚使用前,先向P3口锁存器写入1,使P3口引脚被上拉至高电平。P3口除了可作为一般I/O引脚使用外,还具有第二输入/输出功能:511011RXD(P3.0)一一串行数据接收(输入)端P3.0~701113TXD(P3.1)一一串行数据发送(输出)端P3.7112148INTO(P3.2)一一外中断0输入端911315INTI(P3.3)一一外中断1输入端1141610TO(P3.4)一一定时/计数器TO的外部输入端1151711T1(P3.5)一一定时/计数器T1的外部输入端1618120WR(P3.6)一一外部数据存储器写选通信号,低电平有效0171913RD(P3.7)一一外部数据存储器读选通信号,低电平有效

❖ 表2-2 增强型MCS-51芯片的引脚功能 P2.0~ P2.7 21~28 24~31 18~25 I/O P2 口:内部带有弱上拉的准双向 I/O 口,作输入 引脚使用前,先向 P2 口锁存器写入 1,使 P2 口引脚 被上拉至高电平。在读/写外部存储器时,P2 口输出 高 8 位地址信号 A15~A8 P3.0~ P3.7 10~17 10 11 12 13 14 15 16 17 11, 13~19 11 13 14 15 16 17 18 19 5, 7~13 5 7 8 9 10 11 12 13 I/O I O I I I I O O P3 口:内部带有弱上拉的准双向 I/O 口,作输入 引脚使用前,先向 P3 口锁存器写入 1,使 P3 口引脚 被上拉至高电平。 P3 口除了可作为一般 I/O 引脚使用外,还具有第 二输入/输出功能: RXD(P3.0)——串行数据接收(输入)端 TXD(P3.1)——串行数据发送(输出)端 INT0(P3.2)——外中断 0 输入端 INT1 (P3.3)——外中断 1 输入端 T0(P3.4)——定时/计数器 T0 的外部输入端 T1(P3.5)——定时/计数器 T1 的外部输入端 WR (P3.6)——外部数据存储器写选通信号,低电 平有效RD (P3.7)——外部数据存储器读选通信号,低电 平有效